Текст описания приведен в факсимильном виде.

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств для выполнения арифметических операций умножения аргументов множимого [mj]f(2n) и множителя [ni]f(2n) в позиционном формате. Техническим результатом является повышение быстродействия выполнения операций умножения. Способ заключается в следующем: для каждых двух условно «i» и «i+1» аргументов аналогового сигнала множителя и аналоговых сигналов позиционной структуры аргументов множимого формируют структуры аргументов аналоговых сигналов частичных произведений посредством линейных логических структур И1, И2; формируют позиционную структуру аналоговых сигналов предварительной суммы посредством линейной логической структуры И3 и объединяют посредством линейной логической функции ИЛИ1 для последующего логического суммирования в функциональной структуре сумматора со структурой аргументов аналоговых сигналов промежуточных сумм старших разрядов, которую формируют путем объединения посредством линейной логической функции ИЛИ2 промежуточных сумм условно «i+2» и «i+3» аргументов аналогового сигнала множителя и аналоговых сигналов позиционной структуры аргументов множимого, сформированных посредством линейных логических структур И4, И5, И6.

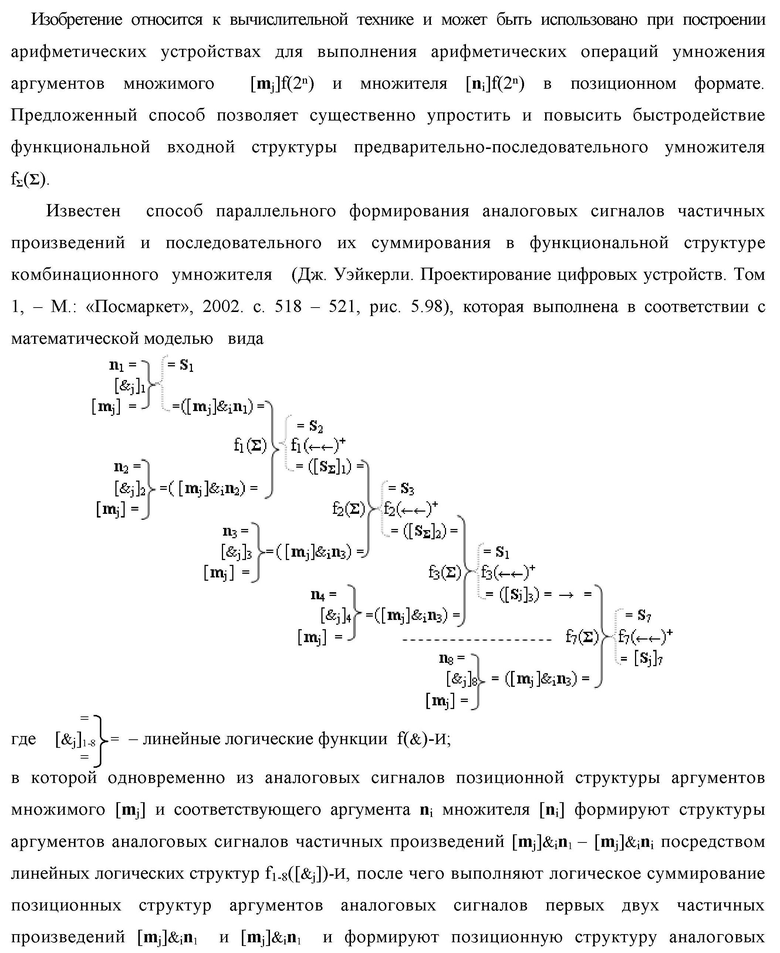

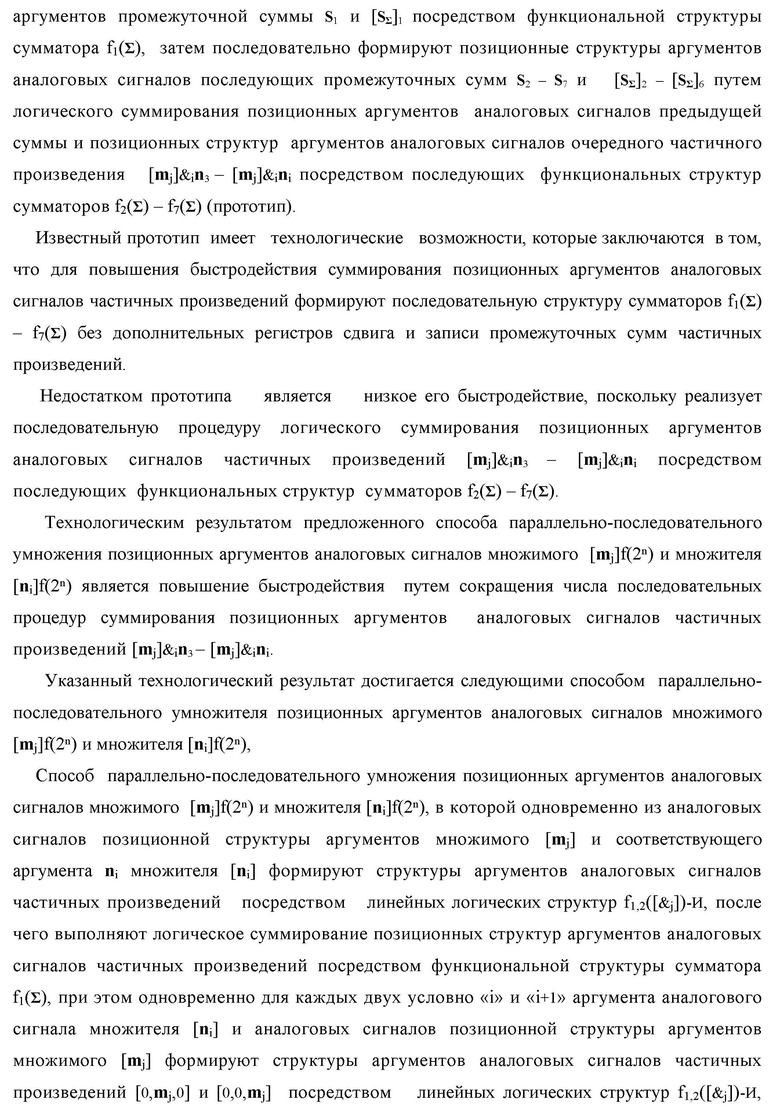

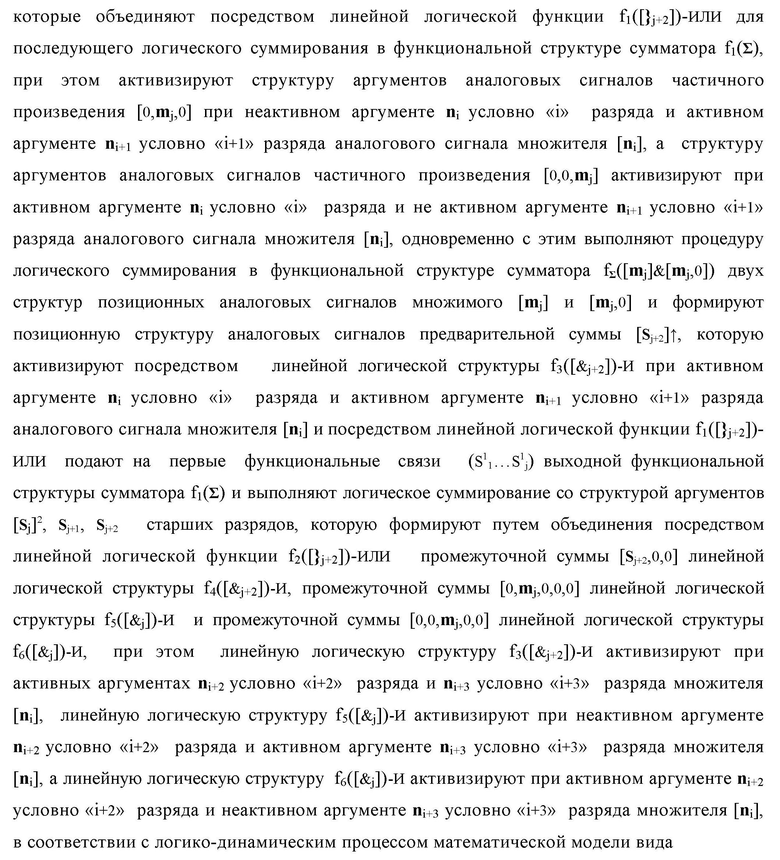

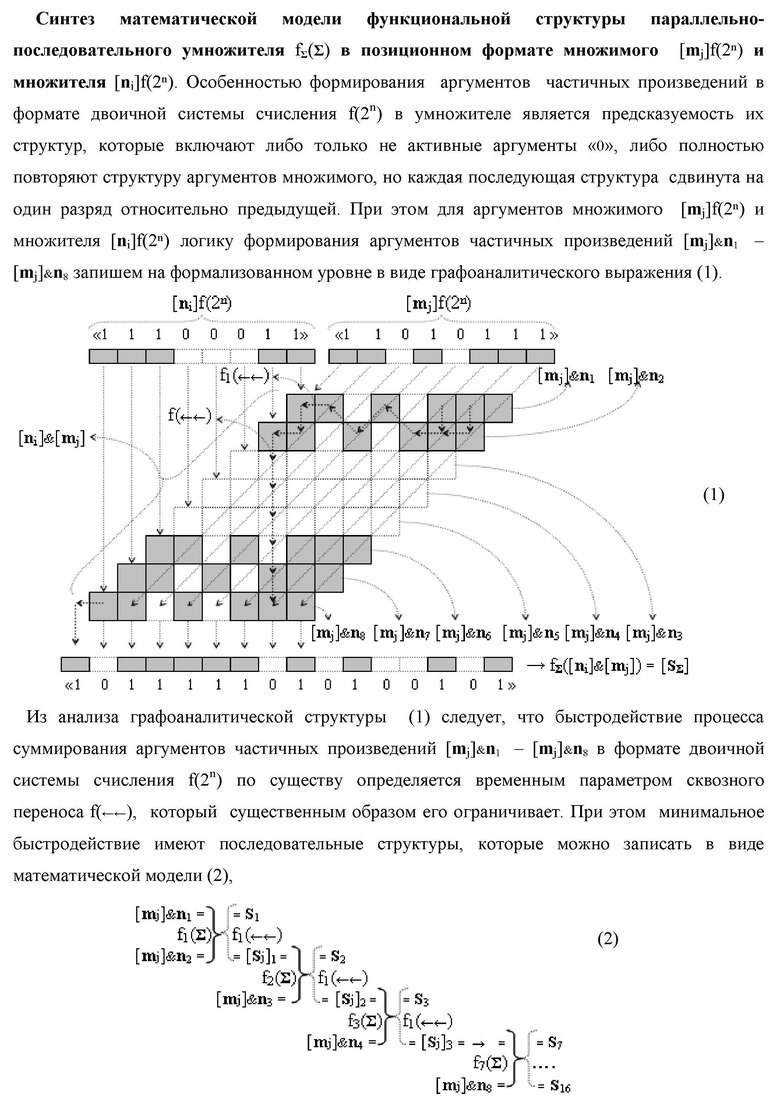

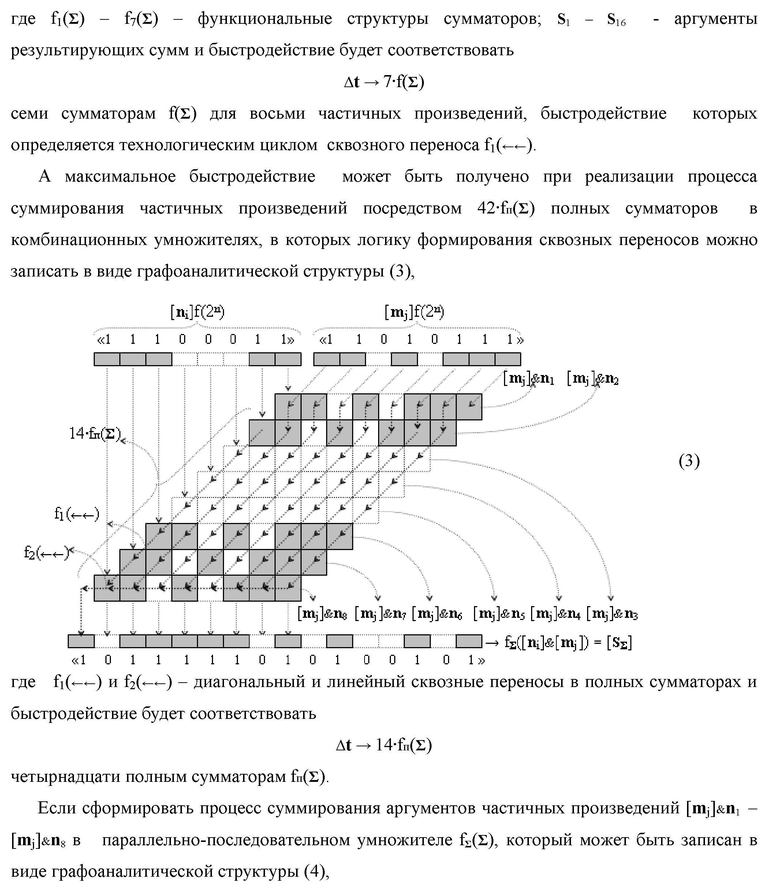

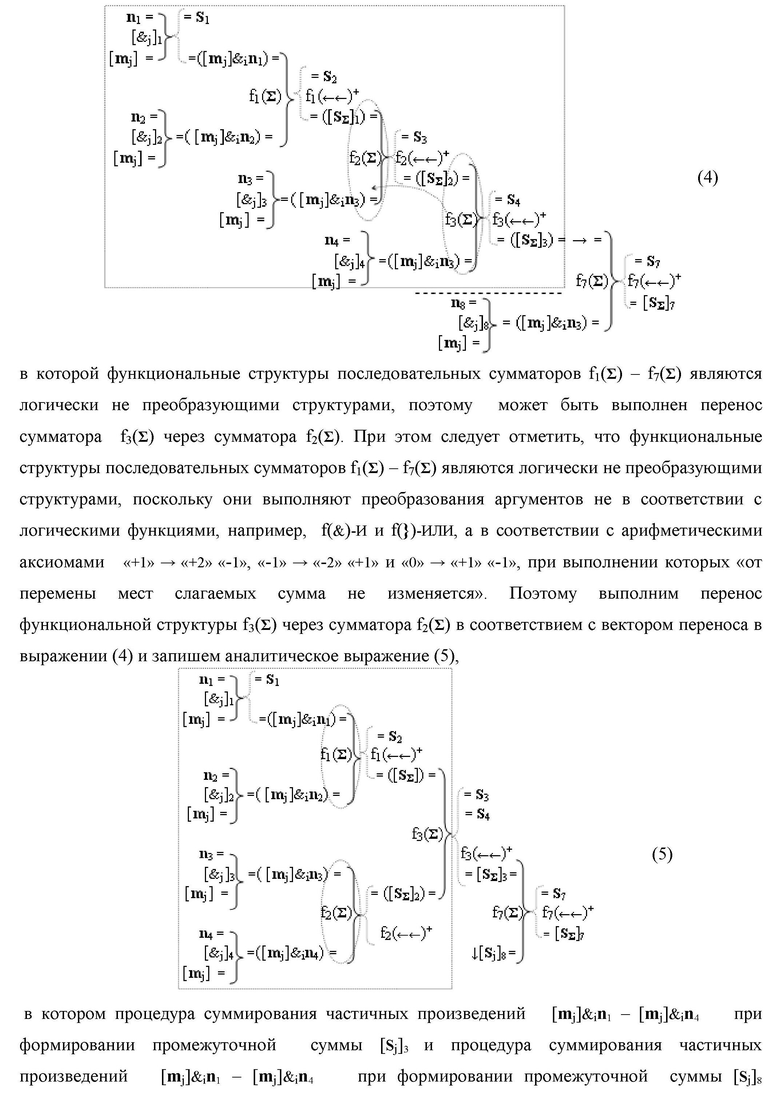

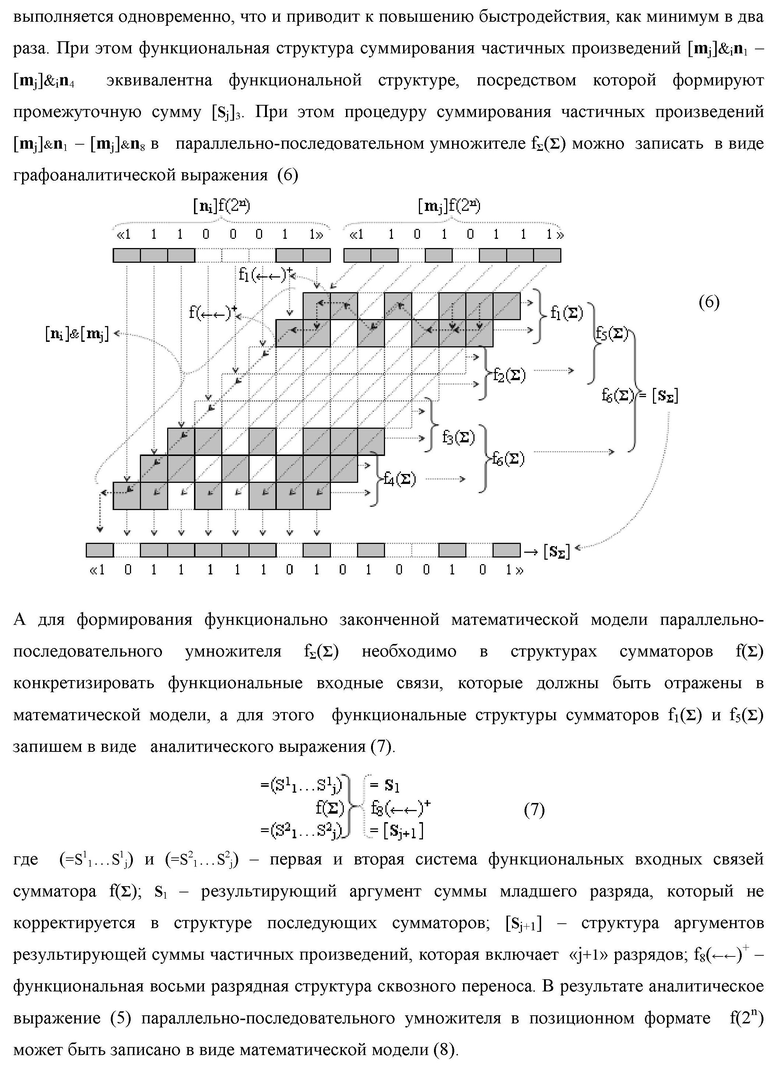

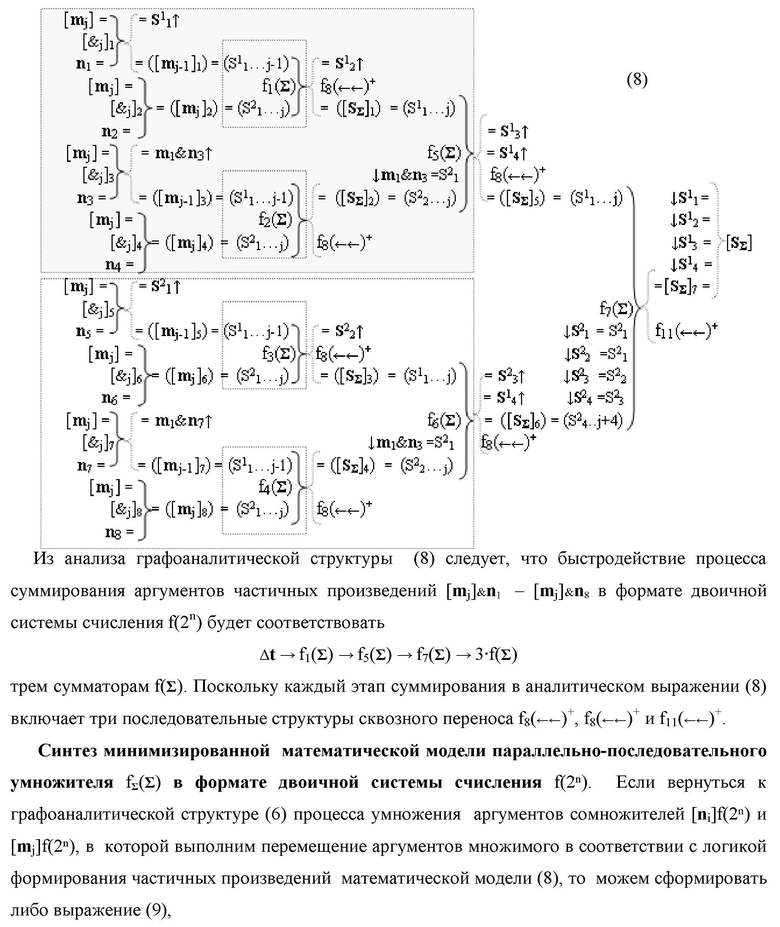

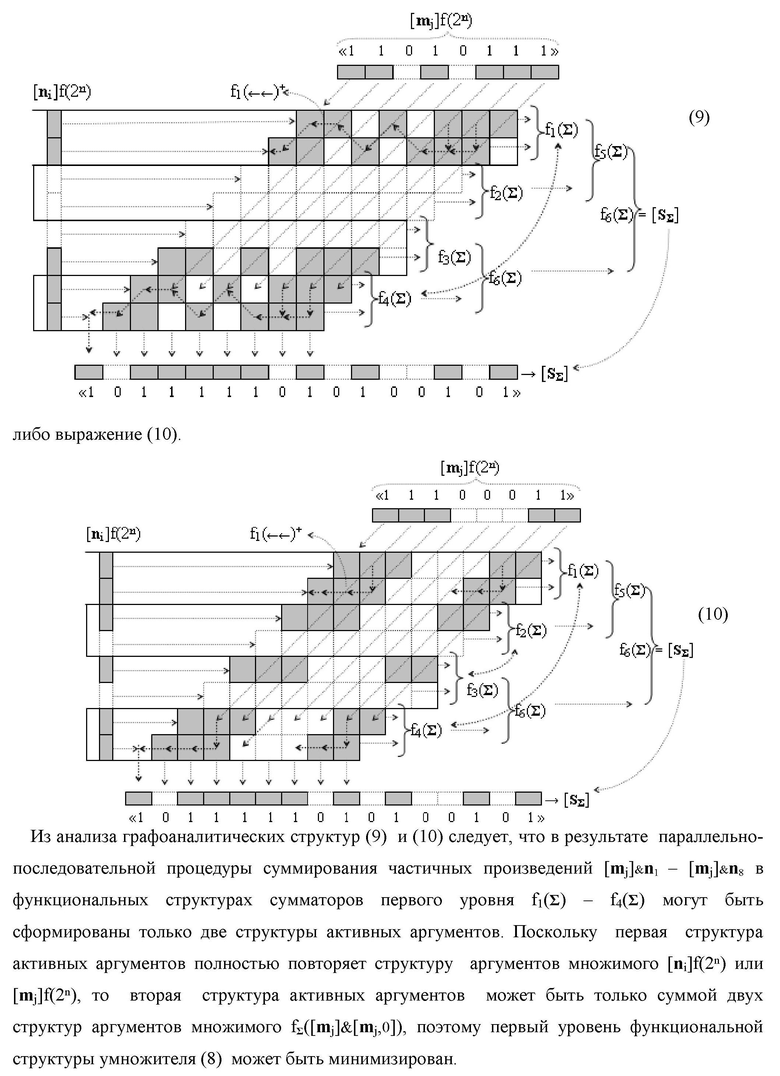

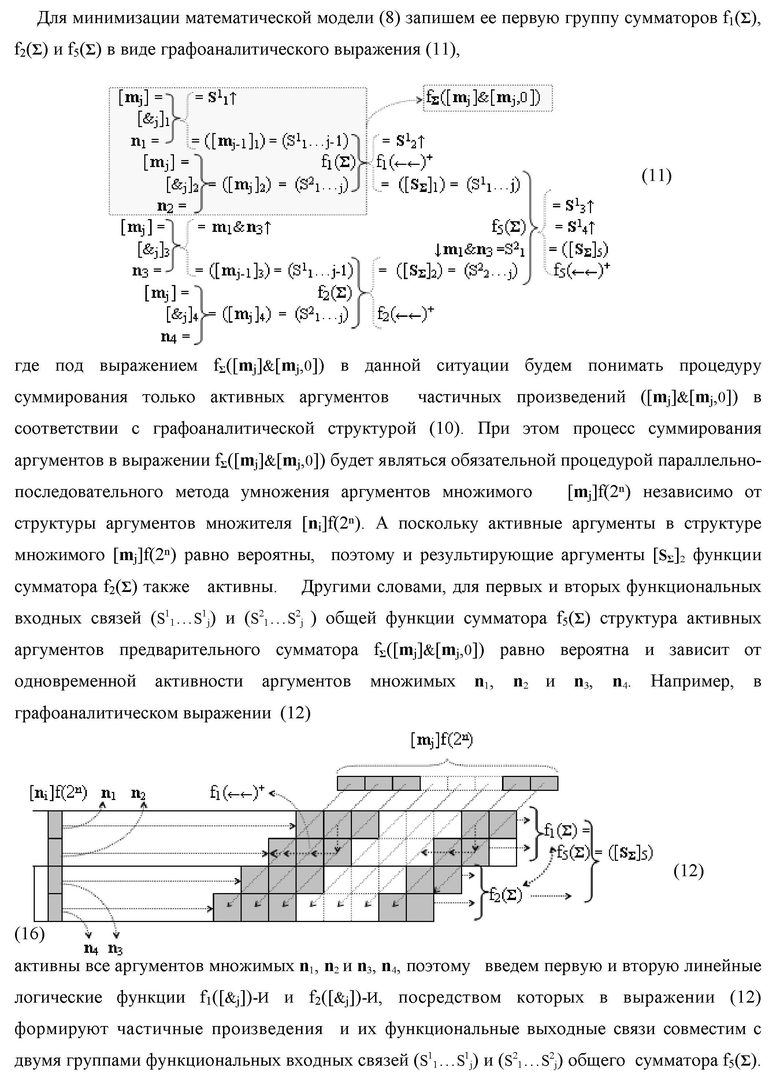

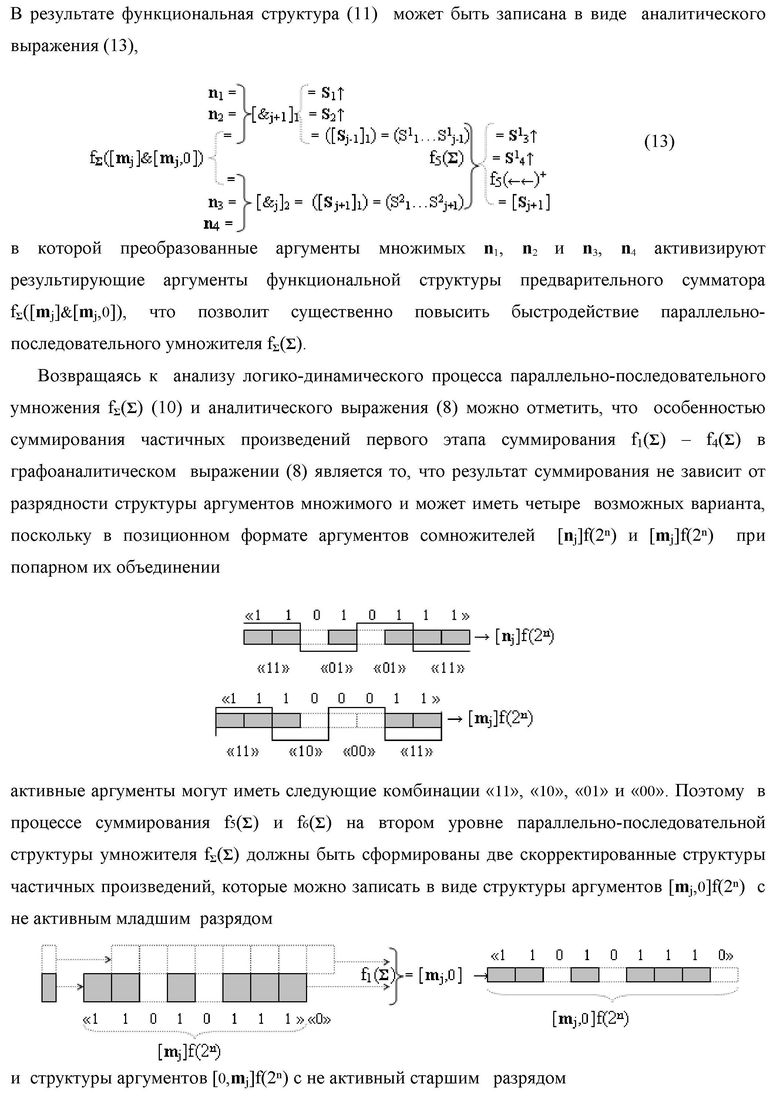

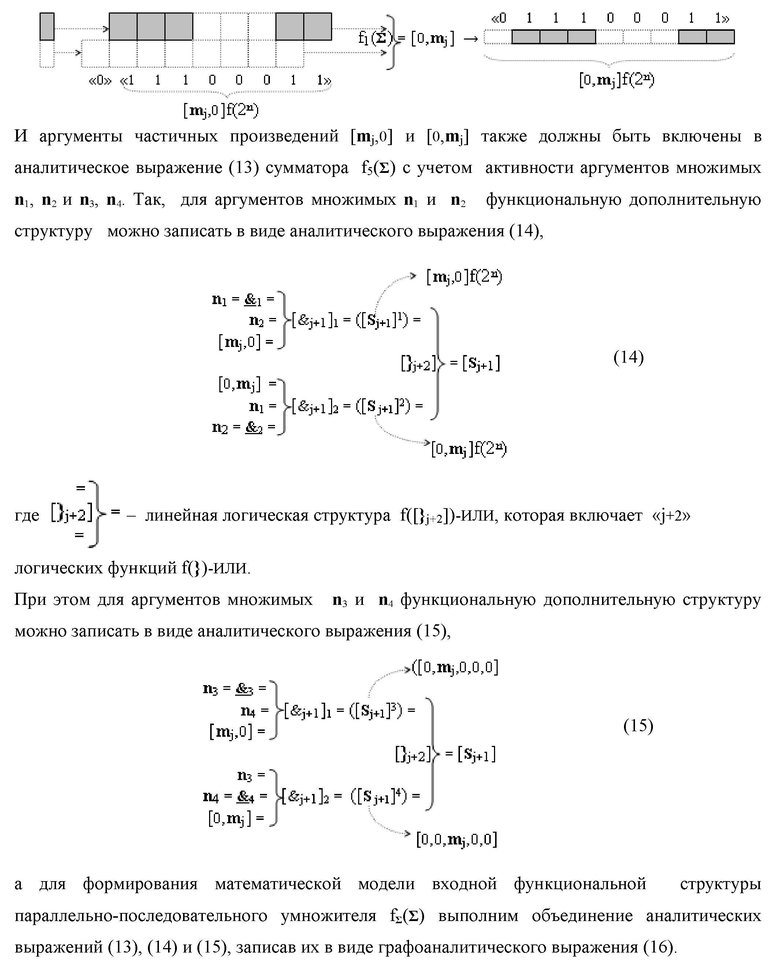

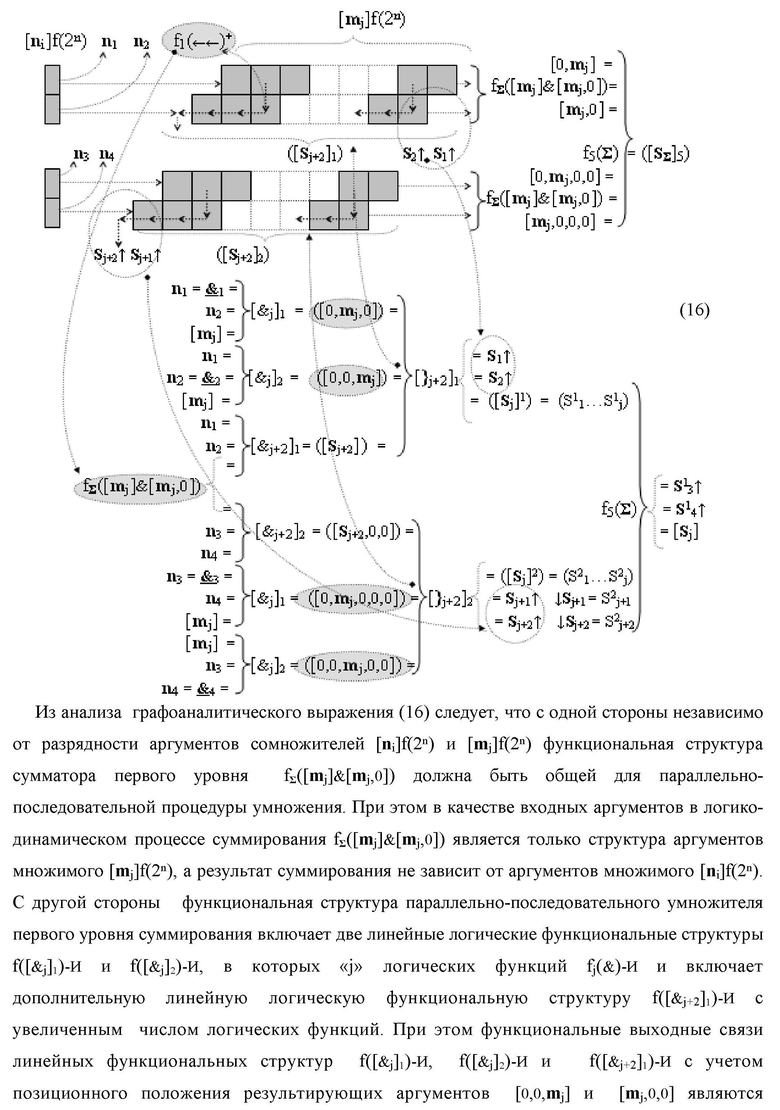

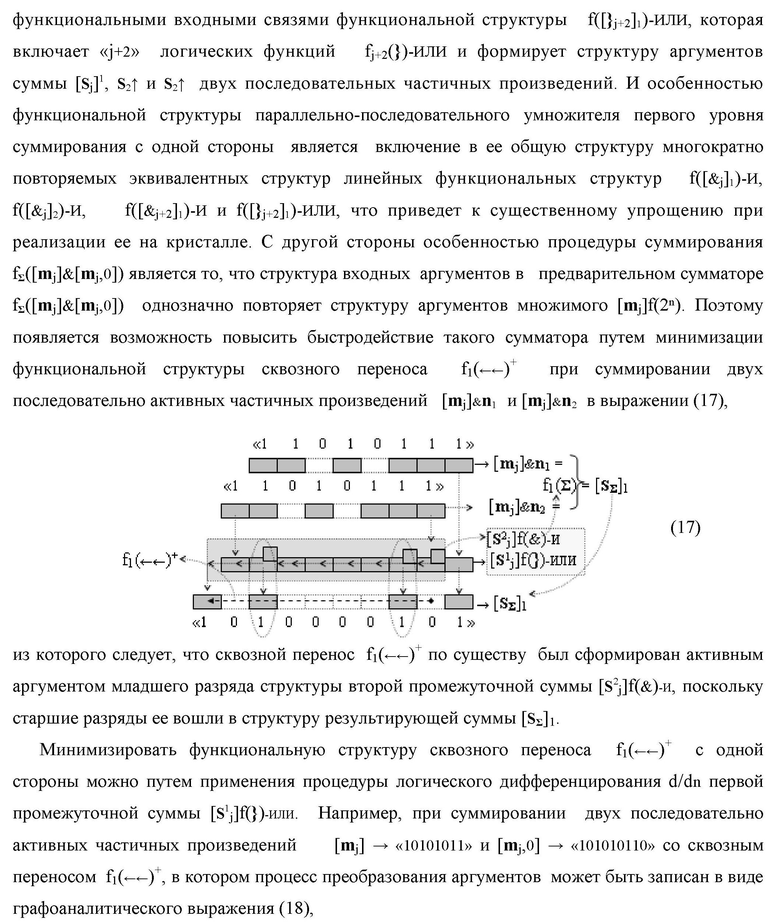

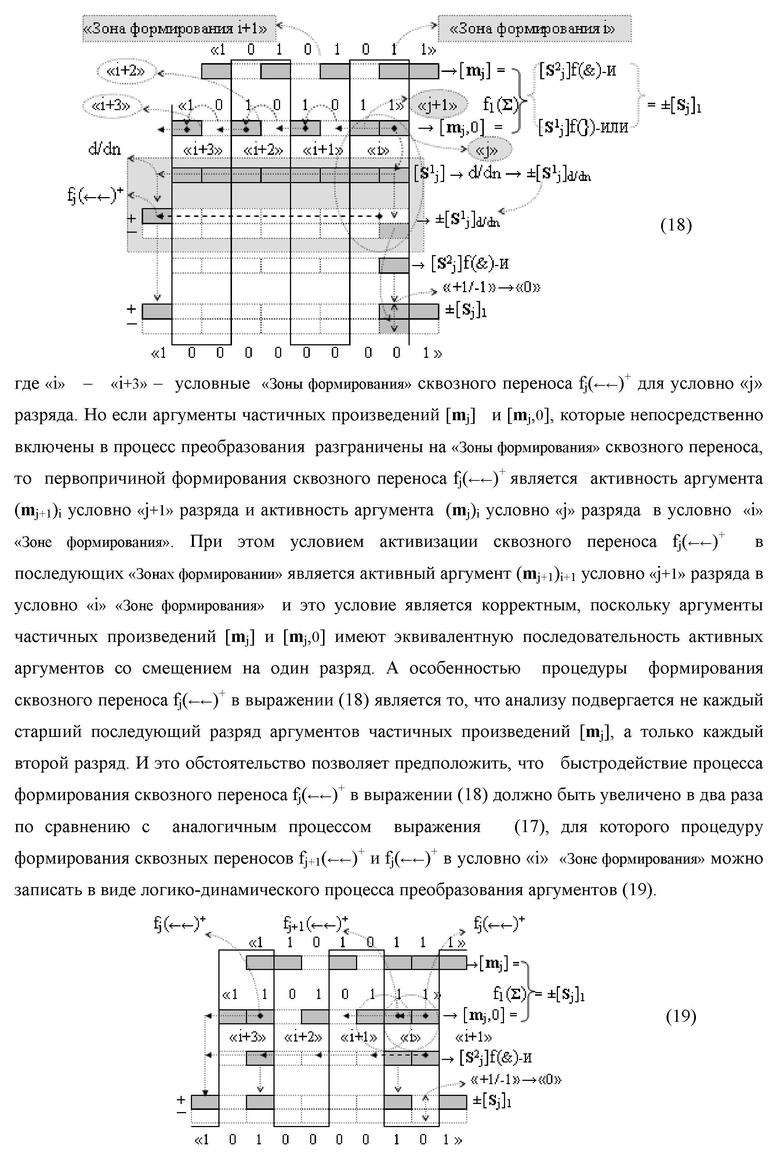

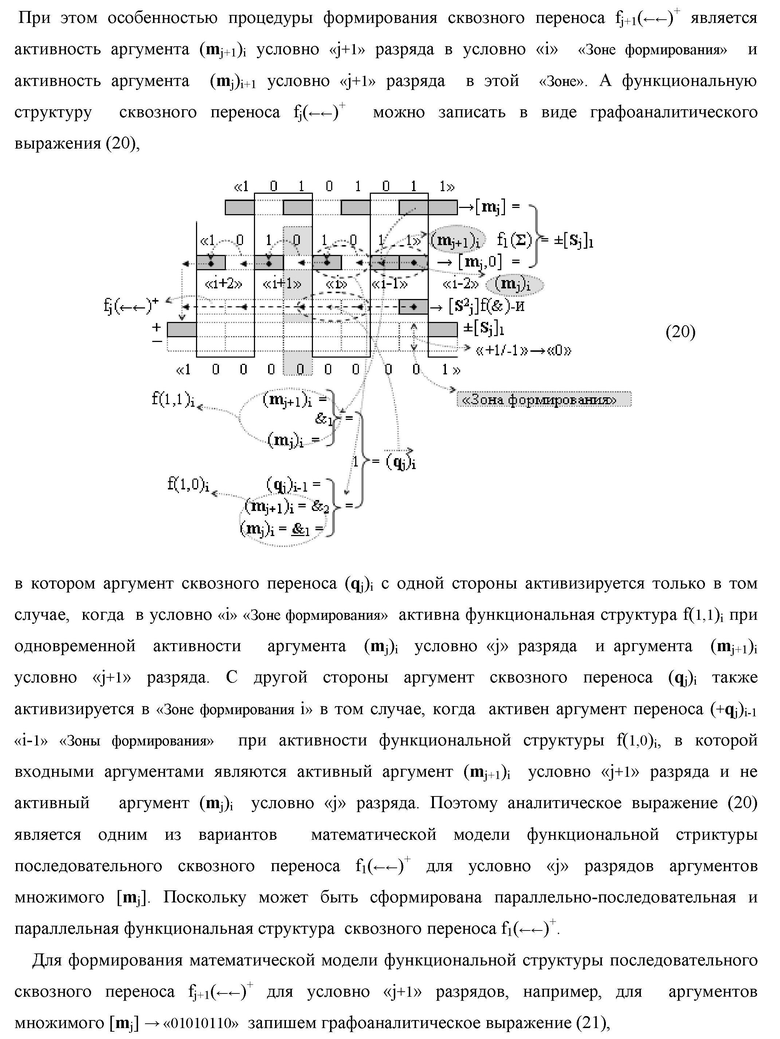

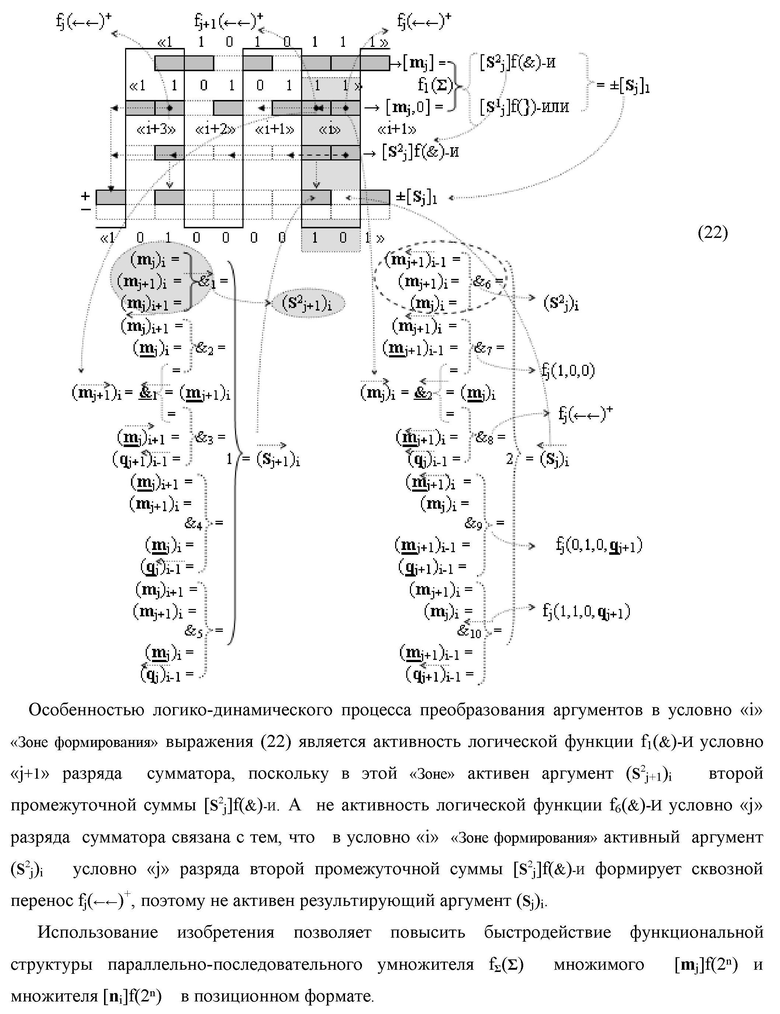

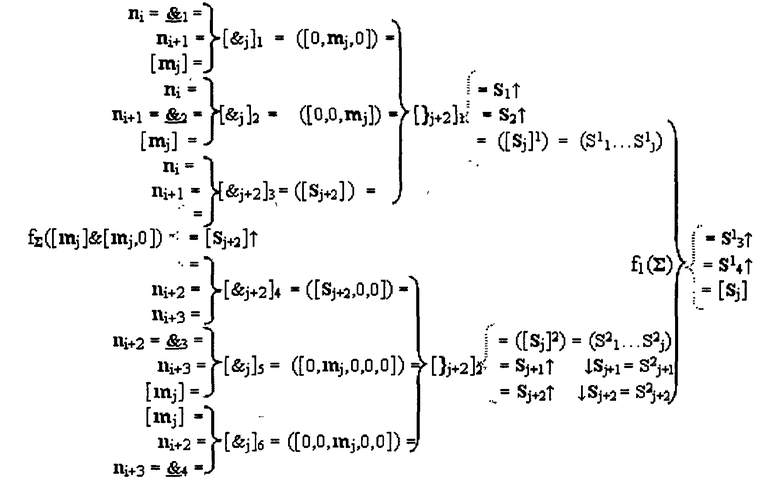

Способ параллельно-последовательного умножения позиционных аргументов аналоговых сигналов множимого [mj]f(2n) и множителя [ni]f(2n), в которой одновременно из аналоговых сигналов позиционной структуры аргументов множимого [mj] и соответствующего аргумента ni множителя [ni] формируют структуры аргументов аналоговых сигналов частичных произведений посредством линейных логических структур f1,2([&j])-И, после чего выполняют логическое суммирование позиционных структур аргументов аналоговых сигналов частичных произведений посредством функциональной структуры сумматора f1(Σ), отличающийся тем, что одновременно для каждых двух условно «i» и «i+1» аргумента аналогового сигнала множителя [ni] и аналоговых сигналов позиционной структуры аргументов множимого [mj] формируют структуры аргументов аналоговых сигналов частичных произведений [0,mj,0] и [0,0,mj] посредством линейных логических структур f1,2([&j])-И, которые объединяют посредством линейной логической функции f1([}j+2])-ИЛИ для последующего логического суммирования в функциональной структуре сумматора f1(Σ), при этом активизируют структуру аргументов аналоговых сигналов частичного произведения [0,mj,0] при неактивном аргументе ni, условно «i» разряда и активном аргументе ni+1 условно «i+1» разряда аналогового сигнала множителя [ni], a структуру аргументов аналоговых сигналов частичного произведения [0,0,mj] активизируют при активном аргументе ni условно «i» разряда и не активном аргументе ni+1 условно «i+1» разряда аналогового сигнала множителя [ni], одновременно с этим выполняют процедуру логического суммирования в функциональной структуре сумматора fΣ([mj]&[mj,0]) двух структур позиционных аналоговых сигналов множимого [mj] и [mj,0] и формируют позиционную структуру аналоговых сигналов предварительной суммы [Sj+2]↑, которую активизируют посредством линейной логической структуры f3([&j+2])-И при активном аргументе ni условно «i» разряда и активном аргументе ni+1 условно «i+1» разряда аналогового сигнала множителя [ni], посредством линейной логической функции f1([}j+2])-ИЛИ подают на первые функциональные связи (S1 1…S1 j) выходной функциональной структуры сумматора f1(Σ) и выполняют логическое суммирование со структурой аргументов [Sj]2, Sj+1, Sj+2 старших разрядов, которую формируют путем объединения посредством линейной логической функции f2([}j+2])-ИЛИ промежуточной суммы [Sj+2,0,0] линейной логической структуры f4([&j+2])-И, промежуточной суммы [0,mj,0,0,0] линейной логической структуры f5([&j])-И и промежуточной суммы [0,0,mj,0,0] линейной логической структуры f6([&j])-И, при этом линейную логическую структуру f3([&j+2])-И активизируют при активных аргументах ni+2 условно «i+2» разряда и ni+3 условно «i+3» разряда множителя [ni], линейную логическую структуру f5([&j])-И активизируют при неактивном аргументе ni+2 условно «i+2» разряда и активном аргументе ni+3 условно «i+3» разряда множителя [ni], а линейную логическую структуру f6([&j])-И активизируют при активном аргументе ni+2 условно «i+2» разряда и неактивном аргументе ni+3 условно «i+3» разряда множителя [ni] в соответствии с логико-динамическим процессом математической модели вида

где fΣ([mj]&[mj,0]) - функциональная структура процедуры логического суммирования двух структур позиционных аналоговых сигналов множимого [mj] и [mj,0], которая формирует позиционную структуру аргументов аналоговых сигналов предварительной суммы [Sj+2]↑;

- линейная логическая структура f1([&j])-И и f3([&j+2])-И, которая включает «j» и «j+2» логических функций f(&)-И;

- линейная логическая структура f1([&j])-И и f3([&j+2])-И, которая включает «j» и «j+2» логических функций f(&)-И;  - линейная логическая структура f([}j+2])-ИЛИ, которая включает «j+2» логических функций f(})-ИЛИ, при этом линейная логическая структура f1([}j+2])-ИЛИ формирует результирующие аргументы S1↑, S2↑ и первую промежуточную сумму [Sj]1, а линейная логическая структура f2([}j+2])-ИЛИ формирует результирующие аргументы Sj+1↑, Sj+2↑ и вторую промежуточную сумму [Sj]2;

- линейная логическая структура f([}j+2])-ИЛИ, которая включает «j+2» логических функций f(})-ИЛИ, при этом линейная логическая структура f1([}j+2])-ИЛИ формирует результирующие аргументы S1↑, S2↑ и первую промежуточную сумму [Sj]1, а линейная логическая структура f2([}j+2])-ИЛИ формирует результирующие аргументы Sj+1↑, Sj+2↑ и вторую промежуточную сумму [Sj]2;

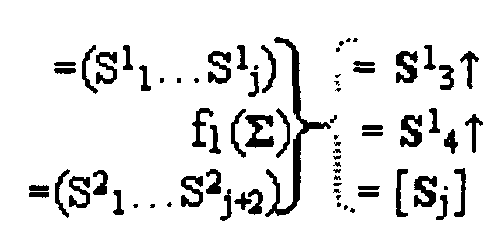

- функциональной структуре сумматора, в которой (=S1 1…S1 j) и (=S2 1…S2 j+2) являются первыми и вторыми системами функциональных входных связей для приема аргументов аналоговых сигналов промежуточных сумм [Sj]1 и [Sj]2, ↓Sj+1, ↓Sj+2.

- функциональной структуре сумматора, в которой (=S1 1…S1 j) и (=S2 1…S2 j+2) являются первыми и вторыми системами функциональных входных связей для приема аргументов аналоговых сигналов промежуточных сумм [Sj]1 и [Sj]2, ↓Sj+1, ↓Sj+2.

| ДЖ | |||

| УЭЙКЕРЛИ | |||

| Проектирование цифровых устройств | |||

| - М.: «Постмаркет», т.1, с.519-521, рис.5.98 | |||

| ФУНКЦИОНАЛЬНАЯ ВХОДНАЯ СТРУКТУРА ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОГО УМНОЖИТЕЛЯ ФОРМАТА ПОЗИЦИОННО-ЗНАКОВОЙ СИСТЕМЫ СЧИСЛЕНИЯ f(+/-) | 2008 |

|

RU2378684C1 |

| US 5986587 A, 16.11.1999 | |||

| US 5907499 A, 25.05.1999. | |||

Авторы

Даты

2011-12-20—Публикация

2010-03-04—Подача