Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано в телеметрических системах с времяимпульсной модуляцией (ВИМ).

Известен программируемый преобразователь код-временной интервал (см. Авт.св. СССР №752797, 30.07.1980. Программируемый преобразователь код-временной интервал. А.Г. Караеев, С.Д. Перехватов, И.Т. Золототрубов, опубл. в БИ №28 от 30.07.1980), который содержит генератор импульсов, выход которого соединен через первый вход первого элемента И со счетным входом счетчика импульсов, входы которого подсоединены к выходам регистра памяти, а выход соединен с первым входом триггера, второй элемент И, первый вход которого соединен с выходом первого элемента И, второй вход - с инверсным выходом триггера, а выход - с первым входом генератора импульсов, второй вход которого соединен со входной шиной, с третьим входом счетчика импульсов и со вторым входом первого элемента И, первый вход которого соединен со вторым входом триггера, прямой выход которого подключен к выходной шине.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбрано в качестве прототипа.

Недостатком вышеуказанного устройства является низкая помехозащищенность, невозможность преобразования больших массивов информации из-за наличия единственной ячейки памяти, представленной регистром, отсутствие системы управления преобразователем, непосредственно участвующей в процессе загрузки данных в регистр и формирующей запускающие импульсы.

Кроме того, поскольку значение преобразуемых данных определяется длительностью выходного импульса, то при воздействии помехи, длительность импульса может быть искажена или импульс может быть интерпретирован как два раздельных импульса вместо одного. Также, во время преобразования массива данных, возможно слияние соседних выходных импульсов. Для того, чтобы предотвратить слияние, необходимо введение задержки между спадом предыдущего импульса и фронтом последующего импульса. При этом, длительность задержки должна составлять не менее одного периода тактового генератора. Это усложняет систему управления преобразователем, увеличивает время преобразования информации, а как следствие - снижает быстродействие преобразователя в целом.

Решаемой технической задачей является создание цифрового преобразователя код-временной интервал, обладающего повышенной надежностью, точностью и быстродействием.

Достигаемым техническим результатом является формирование последовательности импульсов, при этом временной интервал между соседними импульсами несет информацию о преобразуемом коде, от которого зависит длительность временного интервала.

Для достижения технического результата в цифровом преобразователе код-временной интервал, содержащем первое запоминающее устройство, первый счетчик временных интервалов, первый и второй логические элементы И, первый триггер, новым является то, что дополнительно введены второй, третий, четвертый, пятый, шестой триггеры, первый, второй, третий логические элементы ИЛИ, первый и второй счетчики адреса, счетчик-защитного интервала времени, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы НЕ, первый, второй, третий, четвертый, пятый, шестой буферные элементы, третий, четвертый, пятый, шестой, седьмой, восьмой логические элементы И, второе запоминающее устройство, первый и второй резисторы, второй счетчик временного интервала, первый, второй, третий, четвертый логические элементы ИЛИ-НЕ и логический элемент И-НЕ, выход которого соединен со вторым входом второго логического элемента И, первый вход которого соединен со входом установки в состояние логического нуля первого триггера, со входом установки в состояние логического нуля счетчика защитного интервала времени, с первым входом управления преобразователя, второй вход которого соединен со вторым входом первого логического элемента ИЛИ, с первым входом второго логического элемента ИЛИ и со вторым входом третьего логического элемента ИЛИ, первый вход которого является восьмым входом управления преобразователя, выход второго логического элемента И соединен со входом установки в состояние логического нуля второго триггера, вход данных и тактовый вход которого объединены между собой и соединены с объединенными входами данных и тактовыми входами третьего и четвертого триггера, с объединенными входами данных D1 и D2 счетчика защитного интервала, с шестым входом управления преобразователя, с объединенными входами старших разрядов адреса А8, А9 первого и второго запоминающих устройств, группы выходов которых соединены с группами выходов пятого и шестого буферных элементов и группами входов первого и второго счетчиков временных интервалов, выходы переноса которых соединены с соответствующими входами четвертого логического элемента И, выход которого соединен со входом шестого логического элемента НЕ, выход которого соединен с тактовым входом пятого триггера, вход данных и вход установки в состояние логической единицы объединены между собой и соединены с первыми входами седьмого и восьмого логических элементов И, со входом данных и со входом установки в состояние логической единицы шестого триггера, со входами установки в состояние логического нуля первого и второго счетчиков временных интервалов, со входами D0 и D3 счетчика временных интервалов, со входом установки состояния логического нуля первого счетчика адреса, с объединенными входами разрешения счета и разрешения переноса первого счетчика адреса и с объединенными входами установки в состояние логического нуля и входом разрешения счета второго счетчика адреса, с входом данных и со входом установки в состояние логической единицы первого триггера и со вторым выводом первого резистора, первый вывод которого является третьим входом управления преобразователя, четвертый вход которого соединен со входами разрешения параллельной загрузки данных первого и второго счетчиков адреса, со вторым входом второго логического элемента ИЛИ, со входом третьего логического элемента НЕ, выход которого соединен со вторыми входами первого и второго логических элементов ИЛИ-НЕ и со входом пятого логического элемента НЕ, выход которого соединен с первым входом пятого логического элемента И и со вторым входом шестого логического элемента И, первый вход которого соединен с инверсным выходом четвертого триггера, вход установки в состояние логической единицы которого соединен с выходом третьего логического элемента ИЛИ-НЕ, первый вход которого и первый вход первого логического элемента ИЛИ-НЕ объединены и соединены с прямым выходом шестого триггера, вход установки в состояние логического нуля которого соединен с выходом шестого логического элемента И, тактовый вход шестого триггера соединен с выходом седьмого логического элемента НЕ и с вторым входом первого логического элемента И, первый вход которого соединен с выходом второго логического элемента ИЛИ и с тактовым входом первого триггера, а выход соединен с тактовыми входами первого и второго счетчиков адреса, группы входов которых являются первой и второй группами входов данных преобразователя и соединены с группами входов пятого и шестого буферных элементов соответственно, входы разрешения третьего состояния которых объединены между собой и соединены со входами записи первого и второго запоминающих устройств, со входом первого логического элемента НЕ с выходом первого логического элемента ИЛИ и со входами разрешения третьего состояния третьего и четвертого буферных элементов, группы входов которых являются соответственно, первой и второй группами входов адреса преобразователя, при этом группа выходов третьего буферного элемента соединена с первыми группами первого и второго запоминающих устройств и с группой выходов первого буферного элемента, группа входов которого соединена с группой выходов первого счетчика адреса, группа выходов четвертого буферного элемента соединена со вторыми группами входов первого и второго запоминающих устройств с группой выходов второго буферного элемента, группа входов которого соединена с группой выходов второго счетчика адреса, входы разрешения третьего состояния первого и второго буферных элементов объединены между собой и соединены с выходом первого логического элемента НЕ, второй вход логического элемента И-НЕ соединен с выходом переноса первого счетчика адреса и со входом разрешения переноса второго счетчика адреса, выход переноса которого соединен через второй резистор с первым входом логического элемента И-НЕ, первый вход первого логического элемента ИЛИ является пятым входом управления преобразователя, инверсный выход первого триггера соединен со входами выбора микросхемы первого и второго запоминающих устройств, вход разрешения параллельной загрузки данных, вход разрешения счета, вход разрешения переноса первого счетчика временных интервалов, вход разрешения параллельной загрузки данных, вход разрешения счета второго счетчика временных интервалов объединены между собой и соединены со вторым входом пятого логического элемента И и с прямым выходом третьего триггера, вход установки в состояние логического нуля которого соединен с выходом первого логического элемента ИЛИ-НЕ, а вход установки в состояние логической единицы третьего триггера соединен с выходом четвертого логического элемента НЕ, вход которого соединен с первым входом второго логического элемента ИЛИ-НЕ и с выходом переноса счетчика защитного интервала, вход разрешения параллельной загрузки данных, вход разрешения счета и вход разрешения переноса которого объединены и соединены с прямым выходом четвертого триггера, вход установки в состояние логического нуля которого соединен с выходом второго логического элемента ИЛИ-НЕ, тактовые входы первого и второго счетчиков временных интервалов объединены и соединены с тактовым входом счетчика защитных интервалов и с выходом третьего логического элемента И, первый вход которого является седьмым входом управления преобразователя, а второй вход соединен с прямым выходом второго триггера, вход установки в состояние логической единицы которого соединен с выходом третьего логического элемента ИЛИ и со входом второго логического элемента НЕ, выход которого соединен со вторым входом третьего логического элемента ИЛИ-НЕ, выход данных D1 первого счетчика временных интервалов соединен с первым входом четвертого логического элемента ИЛИ-НЕ, выход которого соединен со вторыми входами седьмого и восьмого логических элементов И, выходы которых являются соответствующими выходами преобразователя, вход седьмого логического элемента НЕ соединен с выходом четвертого логического элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом пятого триггера, вход установки в состояние логического нуля которого соединен с выходом пятого логического элемента И, вход разрешения переноса второго счетчика временных интервалов соединен с первым входом четвертого логического элемента И.

Новая совокупность существенных признаков в заявляемом устройстве позволяет производить отсчет каждого временного интервала, несущего информацию об исходном коде, от предыдущего сформированного импульса. Изменение частоты сигналов синхронизации, формируемых внешним генератором, позволяет варьировать длительность временных интервалов и изменять скорость передачи информации. В отличие от известного программируемого преобразователя код-временной интервал, в предлагаемом преобразователе, погрешность получения временного интервала не зависит от длительности и периода тактовых импульсов и определяется точностью задания частоты сигналов синхронизации.

Кроме того, благодаря наличию в составе преобразователя запоминающих устройств, возможно преобразование как одного слова данных, так и организация непрерывного преобразования массива информации, ограниченного объемом запоминающих устройств. В виду наличия автоматической системы управления преобразователем, преобразование информации происходит без участия внешней управляющей системы, что увеличивает быстродействие.

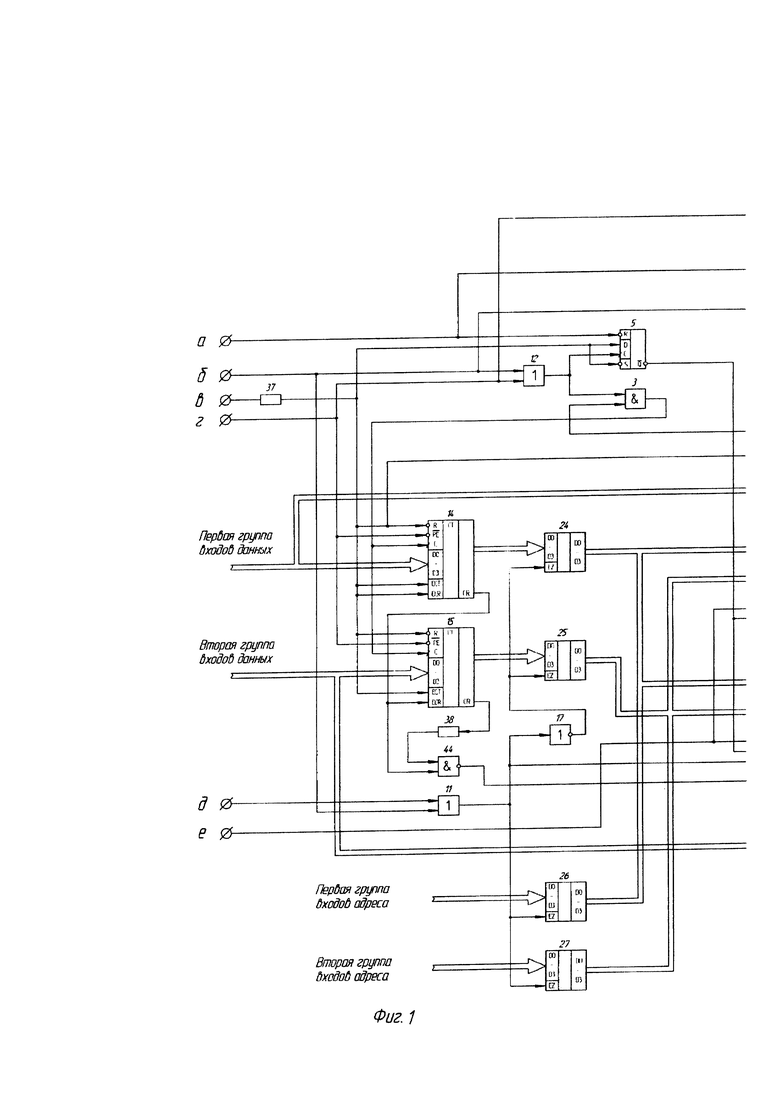

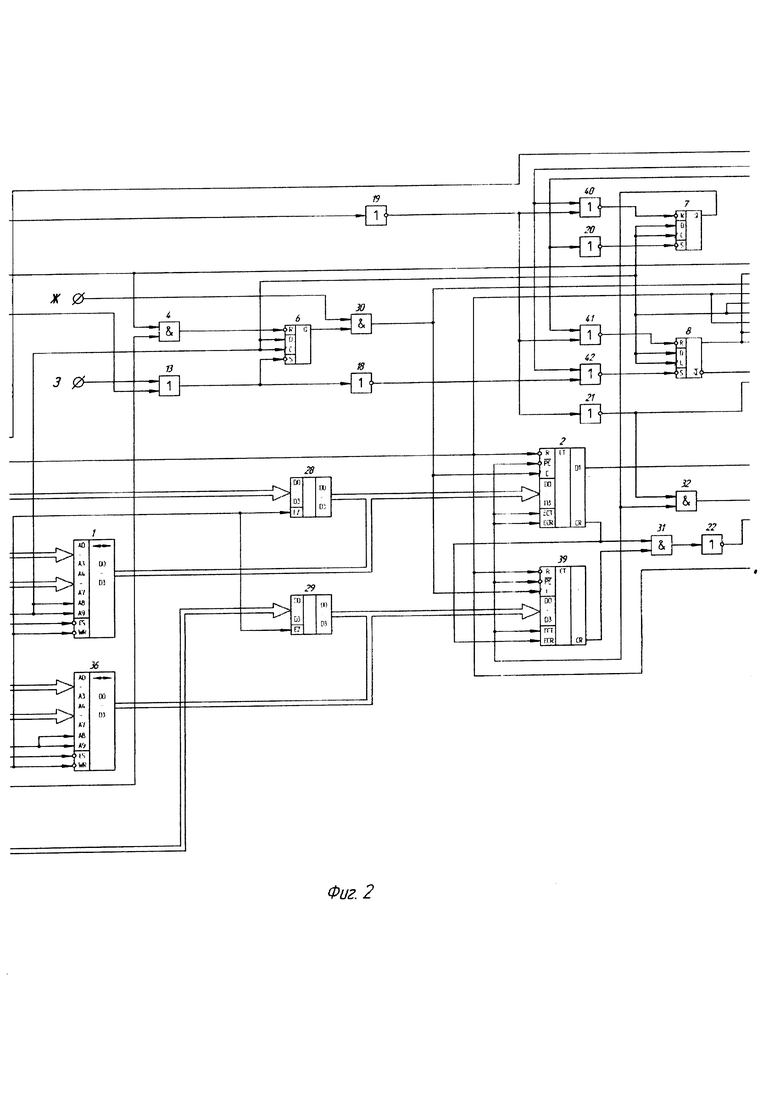

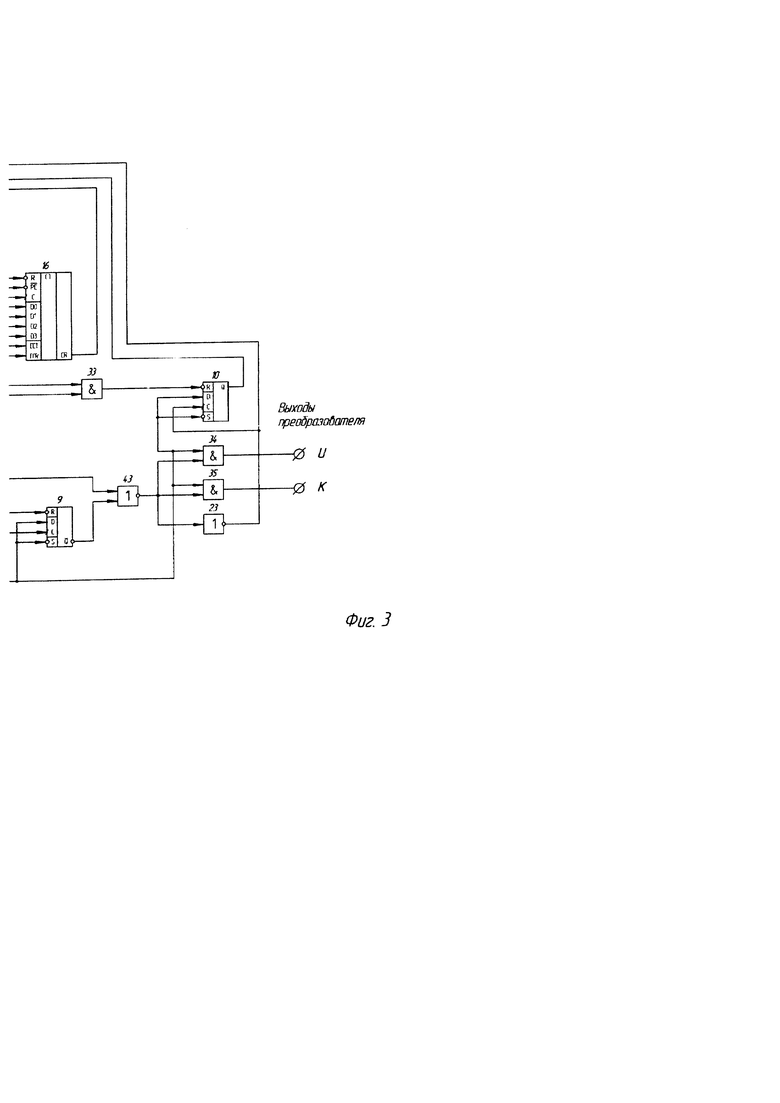

На фиг. 1, 2 и 3 представлена структурная схема заявляемого устройства.

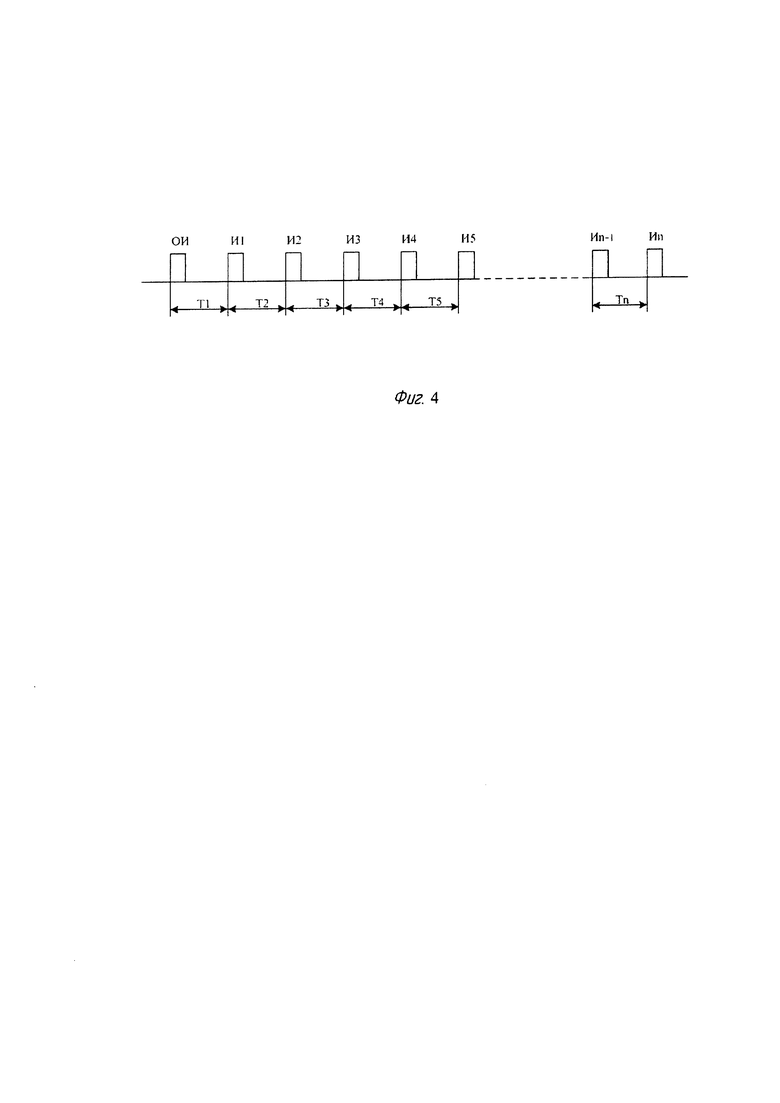

На фиг. 4 представлена структура выходной информации преобразователя, где

ОИ - опорный импульс;

И1…Иn - импульсы последовательности, полученные в результате работы преобразователя;

Т1…Тn - временные интервалы, которыми представлены данные в результате преобразования.

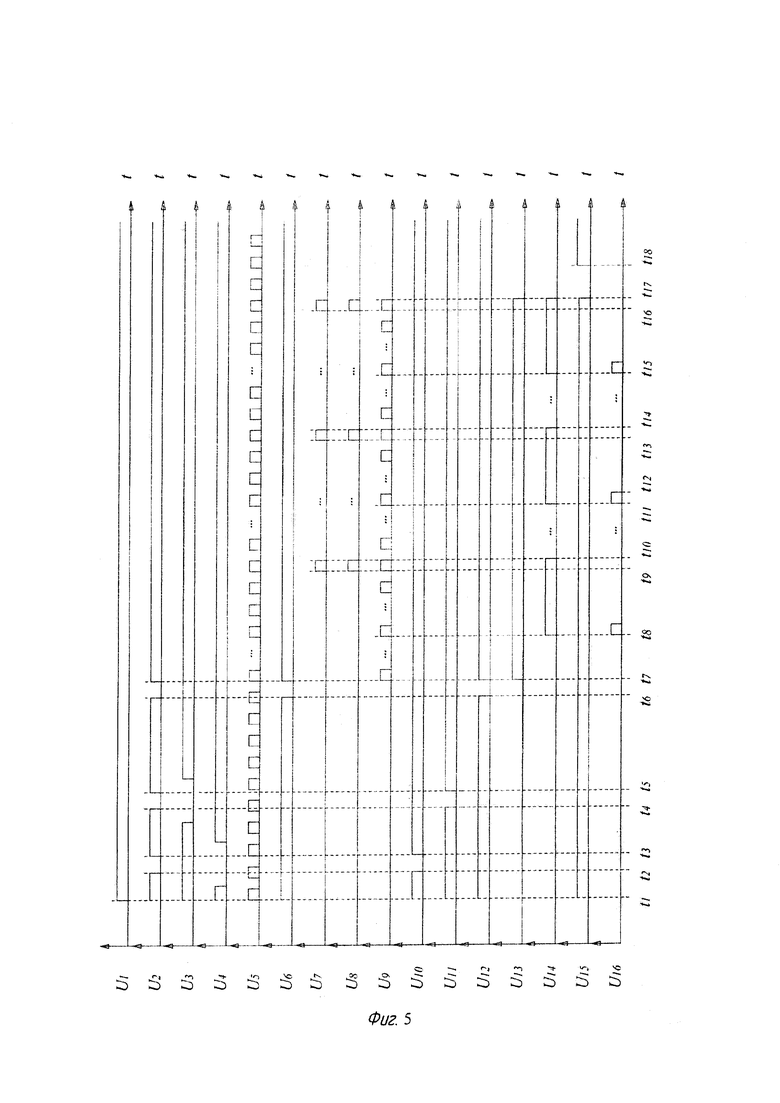

На фиг. 5 представлены временные диаграммы работы устройства.

Цифровой преобразователь код-временной интервал содержит первое запоминающее устройство 1, первый счетчик временных интервалов 2, первый 3 и второй 4 логические элементы И, первый 5, второй 6, третий 7, четвертый 8, пятый 9, шестой 10 триггеры, первый 11, второй 12, третий 13 логические элементы ИЛИ, первый 14 и второй 15 счетчики адреса, счетчик защитного интервала времени 16, первый 17, второй 18, третий 19, четвертый 20, пятый 21, шестой 22, седьмой 23 элементы НЕ, первый 24, второй 25, третий 26, четвертый 27, пятый 28, шестой 29 буферные элементы, третий 30, четвертый 31, пятый 32, шестой 33, седьмой 34, восьмой 35 логические элементы И, второе запоминающее устройство 36, первый 37 и второй 38 резисторы, второй счетчик временного интервала 39, первый 40, второй 41, третий 42, четвертый 43 логические элементы ИЛИ-НЕ и логический элемент И-НЕ 44. Выход логического элемента И-НЕ 44 соединен со вторым входом второго логического элемента И 4, первый вход которого соединен со входом установки в состояние логического нуля первого триггера 5 и со входом установки в состояние логического нуля счетчика защитного интервала времени 16, с первым входом управления преобразователя «а», второй вход «б» которого соединен со вторым входом первого логического элемента ИЛИ 11, с первым входом второго логического элемента ИЛИ 12 и со вторым входом третьего логического элемента ИЛИ 13, первый вход которого является восьмым входом управления преобразователя «з», выход второго логического элемента И 4 соединен со входом установки в состояние логического нуля второго триггера 6, вход данных и тактовый вход которого объединены между собой и соединены с объединенными входами данных и тактовыми входами третьего 7 и четвертого 8 триггера, с объединенными входами данных D1 и D2 счетчика защитного интервала времени 16, с шестым входом управления преобразователя «е», с объединенными входами старших разрядов адреса А8, А9 первого 1 и второго 36 запоминающих устройств, группы входов/выходов которых соединены с группами выходов пятого 28 и шестого 29 буферных элементов и группами входов первого 2 и второго 39 счетчиков временных интервалов, выход переноса первого счетчика временных интервалов 2 соединен со входом разрешения переноса второго счетчика временных интервалов 39 и с первым входом четвертого логического элемента И 31, выход переноса второго счетчика временных интервалов 39 соединен со вторым входом четвертого логического элемента И 31, выход которого соединен со входом шестого логического элемента НЕ 22, выход которого соединен с тактовым входом пятого триггера 9, вход данных и вход установки в состояние логической единицы которого объединены между собой и соединены с первыми входами седьмого 34 и восьмого 35 логических элементов И, со входом данных и со входом установки в состояние логической единицы шестого триггера 10, со входами установки в состояние логического нуля первого 2 и второго 39 счетчиков временных интервалов, со входами D0 и D3 счетчика защитного интервала времени 16, со входом установки в состояние логического нуля первого счетчика адреса 14, с объединенными входами разрешения счета и разрешения переноса первого счетчика адреса 14 и с объединенными входами установки в состояние логического нуля и входом разрешения счета второго счетчика адреса 15, с входом данных и со входом установки в состояние логической единицы первого триггера 5 и через первый резистор 37 соединен с третьим входом управления преобразователя «в», четвертый вход «г» которого соединен со входами разрешения параллельной загрузки данных первого 14 и второго 15 счетчиков адреса, со вторым входом второго логического элемента ИЛИ 12, со входом третьего логического элемента НЕ 19, выход которого соединен со вторыми входами первого 40 и второго 41 логических элементов ИЛИ-НЕ и со входом пятого логического элемента НЕ 21, выход которого соединен с первым входом пятого логического элемента И 32 и со вторым входом шестого 33 логического элемента И, первый вход которого соединен с инверсным выходом четвертого триггера 8, вход установки в состояние логической единицы которого соединен с выходом третьего логического элемента ИЛИ-НЕ 42, первый вход которого и первый вход первого логического элемента ИЛИ-НЕ 40 объединены и соединены с прямым выходом шестого триггера 10, вход установки в состояние логического нуля которого соединен с выходом шестого логического элемента И 33, тактовый вход шестого триггера 10 соединен с выходом седьмого логического элемента НЕ 23 и со вторым входом первого логического элемента И 3, первый вход которого соединен с выходом второго логического элемента ИЛИ 12 и с тактовым входом первого триггера 5, а выход соединен с тактовыми входами первого 14 и второго 15 счетчиков адреса, группы входов которых являются первой и второй группами входов данных преобразователя и соединены с группами входов пятого 28 и шестого 29 буферных элементов соответственно, входы разрешения третьего состояния которых объединены между собой и соединены со входами записи первого 1 и второго 36 запоминающих устройств, со входом первого логического элемента НЕ 17, с выходом первого логического элемента ИЛИ 11 и со входами разрешения третьего состояния третьего 26 и четвертого 27 буферных элементов, группы входов которых являются соответственно первой и второй группами входов адреса преобразователя, при этом группа выходов третьего буферного элемента 26 соединена с первыми группами входов адреса первого 1 и второго 36 запоминающих устройств и с группой выходов первого буферного элемента 24, группа входов которого соединена с группой выходов первого счетчика адреса 14, группа выходов четвертого буферного элемента 27 соединена со вторыми группами входов адреса первого 1 и второго 36 запоминающих устройств, с группой выходов второго буферного элемента 25, группа входов которого соединена с группой выходов второго счетчика адреса 15, входы разрешения третьего состояния первого 24 и второго 25 буферных элементов объединены между собой и соединены с выходом первого логического элемента НЕ 17, второй вход логического элемента И-НЕ 44 соединен с выходом переноса первого счетчика адреса 14 и со входом разрешения переноса второго счетчика адреса 15, выход переноса которого соединен через второй резистор 38 с первым входом логического элемента И-НЕ 44, первый вход первого логического элемента ИЛИ 11 является пятым входом управления преобразователя «д», инверсный выход первого триггера 5 соединен со входами выбора микросхемы первого 1 и второго 36 запоминающих устройств, вход разрешения параллельной загрузки данных, вход разрешения счета, вход разрешения переноса первого счетчика временных интервалов 2, вход разрешения параллельной загрузки данных, вход разрешения счета второго счетчика временных интервалов 39 объединены между собой и соединены со вторым входом пятого логического элемента И 32 и с прямым выходом третьего триггера 7, вход установки в состояние логического нуля которого соединен с выходом первого логического элемента ИЛИ-НЕ 40, а вход установки в состояние логической единицы третьего триггера 7 соединен с выходом четвертого логического элемента НЕ 20, вход которого соединен с первым входом второго 41 логического элемента ИЛИ-НЕ и с выходом переноса счетчика защитного интервала 16, вход разрешения параллельной загрузки данных, вход разрешения счета и вход разрешения переноса которого объединены и соединены с прямым выходом четвертого триггера 8, вход установки в состояние логического нуля которого соединен с выходом второго 41 логического элемента ИЛИ-НЕ, тактовые входы первого 2 и второго 39 счетчиков временных интервалов объединены и соединены с тактовым входом счетчика защитных интервалов 16 и с выходом третьего 30 логического элемента И, первый вход которого является седьмым входом управления преобразователя «ж», а второй вход соединен с прямым выходом второго 6 триггера, вход установки в состояние логической единицы которого соединен с выходом третьего 13 логического элемента ИЛИ и со входом второго 18 логического элемента НЕ, выход которого соединен со вторым входом третьего 42 логического элемента ИЛИ-НЕ, выход данных D1 первого 2 счетчика временных интервалов соединен с первым входом четвертого 43 логического элемента ИЛИ-НЕ, выход которого соединен со вторыми входами седьмого 34 и восьмого 35 логических элементов И, выходы которых являются выходами преобразователя, «и» и «к», соответственно, вход седьмого 23 логического элемента НЕ соединен с выходом четвертого 43 логического элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом пятого 9 триггера, вход установки в состояние логического нуля которого соединен с выходом пятого 32 логического элемента И.

Устройство работает следующим образом.

На этапе установки преобразователя в исходное состояние, со входа управления "а" преобразователя поступает сигнал сброса. Подаваемый сигнал, поступает на входы установки в состояние логического нуля триггера 5 и счетчика защитного интервала 16, а также на первый вход логического элемента И 4, вызывая обнуление триггера 5 и счетчика защитного интервала 16. На выходе логического элемента И 4, появляется сигнал с уровнем логического нуля, поступающий на вход установки в состояние логического нуля триггера 6 и вызывающий его обнуление. Со входа управления преобразователя «в», через резистор 37 подается сигнал с уровнем логической единицы на вход установки в состояние логического нуля, вход разрешения счета и вход разрешения переноса счетчика адреса 14, на вход установки в состояние логического нуля и вход разрешения счета счетчика адреса 15, на входы установки в состояние логического нуля счетчиков временных интервалов 2 и 39, входы D0 и D3 счетчика защитного интервала 16, входы данных D и входы установки в состояние логической единицы S триггеров 9 и 10, на первые входы логических элементов И 34 и 35. Со входа управления преобразователя «е», подается сигнал с уровнем логического нуля, поступающий на входы адреса А8, А9 запоминающих устройств 1 и 36, тактовые входы С, входы данных D триггеров 6, 7 и 8, входы данных Dl, D2 счетчика защитного интервала 16.

При загрузке данных в запоминающие устройства 1 и 36 преобразователя, сигналы с активным уровнем логического нуля, со входов управления преобразователя "б" и "д" поступают на второй и первый входы логического элемента ИЛИ 11 и на его выходе, на время, между точками t2 и t3, формируется сигнал низкого логического уровня, поступающий на входы разрешения третьего состояния буферных элементов 26, 27, 28 и 29, разрешая их работу, и на вход логического элемента НЕ 17, а также на входы записи запоминающих устройств 1 и 36. За период времени между точками t2 и t3, данные, с первой и второй групп входов данных преобразователя, через буферные элементы 28 и 29 поступают на входы/выходы данных D0…D3 запоминающих устройств 1 и 36 соответственно. Адрес, с первой и второй групп входов адреса преобразователя, через буферные элементы 26 и 27 поступает на входы адреса А0…A3 и А4…А7 запоминающих устройств 1 и 36 соответственно. Запись данных в ячейки памяти запоминающих устройств 1 и 36 осуществляется в момент времени t3, по фронту сигнала с выхода логического элемента ИЛИ 11. Процесс записи повторяется до заполнения необходимого количества ячеек памяти.

Сигнал с уровнем логической единицы на входе логического элемента НЕ 17, вызывает формирование на его выходе сигнала с уровнем логического нуля и поступая на входы разрешения третьего состояния буферных элементов 24 и 25 разрешает их работу. Данные, с групп выходов данных D0…D3 счетчиков адреса 14 и 15, поступают через буферные элементы 24 и 25 на входы адреса запоминающих устройств 1 и 36. При этом, работа буферных элементов 26, 27, 28 и 29 запрещена и их выходы находятся в третьем, высокоимпедансном состоянии, так как на выходе логического элемента ИЛИ 11 присутствует сигнал с уровнем логической единицы. С первой и второй групп входов данных преобразователя, данные, содержащие адрес предустановленной ячейки памяти, поступают на входы данных счетчиков 14 и 15. Подаваемый со входа управления "г" преобразователя сигнал, с уровнем логического нуля поступает на входы разрешения параллельной загрузки данных счетчиков адреса 14 и 15, разрешая запись данных, а также на вход логического элемента НЕ 19 и на второй вход логического элемента ИЛИ 12. Сигнал низкого логического уровня, подаваемый на вход управления "б" преобразователя и сигнал низкого логического уровня, подаваемый на вход "г" преобразователя, поступая на первый и второй входы логического элемента ИЛИ 12, вызывают формирование на его выходе сигнала с низким логическим уровнем на время между точками t4 и t5. Сигнал низкого логического уровня, поступая на тактовый вход триггера 5 и на первый вход логического элемента И 3, вызывает в момент времени t5 переключение выхода триггера 5 в предварительно установленное состояние логической единицы, задаваемое подключением входа данных триггера ко входу управления "в" преобразователя через резистор 37, а также формирование на выходе логического элемента И 3 сигнала с уровнем логической единицы, поступающего на тактовые входы счетчиков адреса 14 и 15, вызывая запись данных. Установленный таким образом, в состояние логической единицы триггер 5, на инверсном выходе формирует сигнал с уровнем логического нуля, поступающий на входы выбора микросхемы запоминающих устройств 1 и 36, разрешая чтение данных из их ячеек. Поступивший на вход логического элемента НЕ 19 сигнал с уровнем логического нуля, формирует на его выходе сигнал с уровнем логической единицы, который в свою очередь поступает на вторые входы логических элементов ИЛИ-НЕ 40, 41 и на вход логического элемента НЕ 21 и вызывает формирование на их выходах сигналов с уровнем логического нуля. Поступление на входы установки в состояние логического нуля триггеров 7 и 8, сигналов с выходов логических элементов ИЛИ-НЕ 40, 41, вызывают сброс каждого из триггеров, соответственно. На их прямых выходах формируются сигналы с уровнем логического нуля. Поступивший на вход логического элемента НЕ 21 сигнал с уровнем логической единицы, вызывает формирование на его выходе сигнала с уровнем логического нуля, поступающего на первый вход логического элемента И 32 и второй вход логического элемента И 33, вызывая формирование на их выходах сигналов с уровнем логического нуля. Сформированные сигналы, с выходов логических элементов И 32, 33 поступают на входы установки в состояние логического нуля триггеров 9 и 10 соответственно, вызывая их сброс. На этом завершается подготовка преобразователя к работе с данными.

Для запуска преобразователя в работу, на его входы управления "б" и "з" подаются сигналы с уровнем логического нуля, комбинация которых, поступающая на входы логического элемента ИЛИ 13, вызывает формирование на его выходе, на время между точками t6-t7, сигнала с уровнем логического нуля, поступающим на вход установки в состояние логической единицы триггера 6 и на вход логического элемента НЕ 18. Поступающий на вход установки в состояние логической единицы триггера 6 сигнал с уровнем логического нуля, вызывает установку на его прямом выходе сигнала с уровнем логической единицы, который, поступает на второй вход логического элемента И 30. Тактовые сигналы, подаваемые со входа "ж" преобразователя на первый вход логического элемента И 30, совместно с сигналом, подаваемым с прямого выхода триггера 6, вызывают формирование на выходе логического элемента И 30, в момент времени t7, сигналов синхронизации. Сигналы синхронизации поступают на тактовые входы счетчика защитного интервала 16, счетчиков временных интервалов 2 и 39. Поступивший с выхода логического элемента НЕ 13 сигнал с уровнем логического нуля, поступает на вход логического элемента НЕ 18 и на его выходе формируется сигнал с уровнем логической единицы, поступающий на второй вход логического элемента ИЛИ-НЕ 42, с выхода которого, сформированный сигнал низкого логического уровня поступает на вход установки в состояние логической единицы триггера 8, вызывая формирование на его прямом выходе сигнала с уровнем логической единицы, а на его инверсном выходе сигнала с уровнем логического нуля. Поступление сигнала с прямого выхода триггера 8 на входы разрешения параллельной загрузки данных, разрешения счета и разрешения переноса счетчика защитного интервала 16, разрешает отсчет защитного интервала времени. Счетчик считает до переполнения и по окончании счета формируется сигнал переноса, в момент времени t8. Сигнал переноса, поступает на вход логического элемента НЕ 20 и первый вход логического элемента ИЛИ-НЕ 41,. на выходе которого формируется сигнал с уровнем логического нуля, поступающий на вход установки в состояние логического нуля триггера 8, вызывая его сброс и как следствие остановку работы счетчика защитного интервала 16. Сигнал с уровнем логической единицы, поступая на вход логического элемента НЕ 20, вызывает формирование на его выходе сигнала с уровнем логического нуля, который, поступая на вход установки в состояние логической единицы триггера 7, в момент времени t7, вызывает формирование на его прямом выходе сигнала с уровнем логической единицы. Далее, сигнал с прямого выхода триггера 7 поступает на входы разрешения параллельной загрузки данных, разрешения счета и разрешения переноса первого счетчика временных интервалов 2, а также на входы разрешения параллельной загрузки данных и разрешения счета второго счетчика временных интервалов. В момент времени t7 разрешается работа первого 2 и второго 39 счетчиков временных интервалов. Счетчики считают до переполнения, начиная от значений данных, предварительно загруженных из ячеек памяти запоминающих устройств 1 и 36, соответственно. После окончания счета, на выходе счетчика 2 формируется сигнал переноса, поступающий на вход разрешения переноса счетчика временных интервалов 39. После того, как на выходах переноса счетчиков временных интервалов 2 и 39 сформируются сигналы переноса, на выходе логического элемента И 31 появится сигнал с уровнем логической единицы, поступающий на вход логического элемента НЕ 22. Поступивший на тактовый вход триггера 9 сигнал с уровнем логического нуля, вызывает переключение его инверсного выхода в состояние логического нуля. С выхода D1 счетчика временных интервалов 2, сигнал с уровнем логического нуля, поступает на первый вход логического элемента ИЛИ-НЕ 43 и вызывает формирование на его выходе сигнала с уровнем логического нуля, поступающего на вторые входы логических элементов И 34, 35 и на вход логического элемента НЕ 23. На выходах логических элементов И 34, 35, в моменты времени t9, t13, t16 формируются выходные импульсы, поступающие на выходы "и" и "к" преобразователя. Сигнал с уровнем логического нуля, с выхода логического элемента НЕ 23 поступает на тактовый вход триггера 10 и вызывает переключение его прямого выхода в состояние высокого логического уровня. Поступая на первые входы логических элементов ИЛИ-НЕ 40 и 42, с выхода триггера 10, сигнал высокого логического уровня, вызывает формирование на их выходах сигналов с низким логическим уровнем. В свою очередь, эти сигналы вызывают сброс триггера 7 и установку триггера 8. Сигнал с выхода логического элемента НЕ 23, поступая на второй вход логического элемента И 3, вызывает формирование на его выходе сигнала с уровнем логического нуля. По фронту сигнала с выхода логического элемента И 3 происходит переключение счетчиков адреса 14 и 15. Описанная последовательность действий повторяется до переполнения счетчиков адреса 14 и 15. С выхода переноса счетчика адреса 14 сигнал переноса поступает на второй вход логического элемента И-НЕ 44, а с выхода переноса счетчика адреса 15 на первый вход логического элемента И-НЕ 44 через резистор 38. При поступлении сигналов переноса от счетчиков адреса 14 и 15 на входы логического элемента И-НЕ 44, на его выходе формируется сигнал низкого логического уровня, поступающий на второй вход логического элемента И 4 и на его выходе формируется сигнал с уровнем логического нуля. В результате этого, триггер 6 сбрасывается и на выходе логического элемента И 30 прекращается формирование сигналов синхронизации, поступающих на тактовые входы счетчика защитного интервала 16 и счетчиков временных интервалов 2 и 39. На этом работа преобразователя завершается.

Заявляемое устройство реализовано в составе серийно выпускаемого прибора, что позволяет сделать вывод о его промышленной применимости. Данное устройство реализовано на микросхемах серий: 537, 1554 и 1564. Цифровой преобразователь код-временной интервал обладает повышенной точностью, надежностью и быстродействием. Это обусловлено тем, что временной интервал, несущий информацию, представлен паузой между двумя смежными импульсами, а не длительностью одного импульса как у прототипа и не зависит от момента поступления сигнала на начало преобразования, а также от периода и длительности тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для вычисления функции | 1985 |

|

SU1290305A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680759C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ | 2010 |

|

RU2428737C1 |

| Цифровой компенсатор выпадений телевизионного сигнала яркости | 1985 |

|

SU1269274A1 |

| Программируемое устройство управления | 1986 |

|

SU1448393A1 |

| Устройство для измерения характеристик синусоидального сигнала | 1985 |

|

SU1307366A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ОШИБОК В КАНАЛЕ | 2001 |

|

RU2192038C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано в телеметрических системах с времяимпульсной модуляцией (ВИМ). Технический результат заключается в повышении надежности работы цифрового преобразователя. Технический результат достигается за счет цифрового преобразователя код-временной интервал, который содержит первое запоминающее устройство, первый счетчик временных интервалов, первый и второй логические элементы И, первый триггер, второй, третий, четвертый, пятый, шестой триггеры, первый, второй, третий логические элементы ИЛИ, первый и второй счетчики адреса, счетчик защитного интервала времени, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы НЕ, первый, второй, третий, четвертый, пятый, шестой буферные элементы, третий, четвертый, пятый, шестой, седьмой, восьмой логические элементы И, второе запоминающее устройство, первый и второй резисторы, второй счетчик временного интервала, первый, второй, третий, четвертый логические элементы ИЛИ-НЕ и логический элемент И-НЕ. 5 ил.

Цифровой преобразователь код-временной интервал, содержащий первое запоминающее устройство, первый счетчик временных интервалов, первый и второй логические элементы И, первый триггер, отличающийся тем, что дополнительно введены второй, третий, четвертый, пятый, шестой триггеры, первый, второй, третий логические элементы ИЛИ, первый и второй счетчики адреса, счетчик защитного интервала времени, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы НЕ, первый, второй, третий, четвертый, пятый, шестой буферные элементы, третий, четвертый, пятый, шестой, седьмой, восьмой логические элементы И, второе запоминающее устройство, первый и второй резисторы, второй счетчик временного интервала, первый, второй, третий, четвертый логические элементы ИЛИ-НЕ и логический элемент И-НЕ, выход которого соединен со вторым входом второго логического элемента И, первый вход которого соединен со входом установки в состояние логического нуля первого триггера, со входом установки в состояние логического нуля счетчика защитного интервала времени, с первым входом управления преобразователя, второй вход которого соединен со вторым входом первого логического элемента ИЛИ, с первым входом второго логического элемента ИЛИ и со вторым входом третьего логического элемента ИЛИ, первый вход которого является восьмым входом управления преобразователя, выход второго логического элемента И соединен со входом установки в состояние логического нуля второго триггера, вход данных и тактовый вход которого объединены между собой и соединены с объединенными входами данных и тактовыми входами третьего и четвертого триггера, с объединенными входами данных D1 и D2 счетчика защитного интервала, с шестым входом управления преобразователя, с объединенными входами старших разрядов адреса А8, А9 первого и второго запоминающих устройств, группы входов/выходов которых соединены с группами выходов пятого и шестого буферных элементов и группами входов первого и второго счетчиков временных интервалов, выход переноса первого счетчика временных интервалов соединен со входом разрешения переноса второго счетчика временных интервалов и с первым входом четвертого логического элемента И, выход переноса второго счетчика временных интервалов соединен со вторым входом четвертого логического элемента И, выход которого соединен со входом шестого логического элемента НЕ, выход которого соединен с тактовым входом пятого триггера, вход данных и вход установки в состояние логической единицы которого объединены между собой и соединены с первыми входами седьмого и восьмого логических элементов И, со входом данных и со входом установки в состояние логической единицы шестого триггера, со входами установки в состояние логического нуля первого и второго счетчиков временных интервалов, со входами D0 и D3 счетчика защитного интервала, со входом установки в состояние логического нуля первого счетчика адреса, с объединенными входами разрешения счета и разрешения переноса первого счетчика адреса и с объединенными входами установки в состояние логического нуля и входом разрешения счета второго счетчика адреса, с входом данных и со входом установки в состояние логической единицы первого триггера и через первый резистор соединен с третьим входом управления преобразователя, четвертый вход которого соединен со входами разрешения параллельной загрузки данных первого и второго счетчиков адреса, со вторым входом второго логического элемента ИЛИ, со входом третьего логического элемента НЕ, выход которого соединен со вторыми входами первого и второго логических элементов ИЛИ-НЕ и со входом пятого логического элемента НЕ, выход которого соединен с первым входом пятого логического элемента И и со вторым входом шестого логического элемента И, первый вход которого соединен с инверсным выходом четвертого триггера, вход установки в состояние логической единицы которого соединен с выходом третьего логического элемента ИЛИ-НЕ, первый вход которого и первый вход первого логического элемента ИЛИ-НЕ объединены и соединены с прямым выходом шестого триггера, вход установки в состояние логического нуля которого соединен с выходом шестого логического элемента И, тактовый вход шестого триггера соединен с выходом седьмого логического элемента НЕ и с вторым входом первого логического элемента И, первый вход которого соединен с выходом второго логического элемента ИЛИ и с тактовым входом первого триггера, а выход соединен с тактовыми входами первого и второго счетчиков адреса, группы входов которых являются первой и второй группами входов данных преобразователя и соединены с группами входов пятого и шестого буферных элементов соответственно, входы разрешения третьего состояния которых объединены между собой и соединены со входами записи первого и второго запоминающих устройств, со входом первого логического элемента НЕ с выходом первого логического элемента ИЛИ и со входами разрешения третьего состояния третьего и четвертого буферных элементов, группы входов которых являются соответственно первой и второй группами входов адреса преобразователя, при этом группа выходов третьего буферного элемента соединена с первыми группами входов адреса первого и второго запоминающих устройств и с группой выходов первого буферного элемента, группа входов которого соединена с группой выходов первого счетчика адреса, группа выходов четвертого буферного элемента соединена со вторыми группами входов адреса первого и второго запоминающих устройств, с группой выходов второго буферного элемента, группа входов которого соединена с группой выходов второго счетчика адреса, входы разрешения третьего состояния первого и второго буферных элементов объединены между собой и соединены с выходом первого логического элемента НЕ, второй вход логического элемента И-НЕ соединен с выходом переноса первого счетчика адреса и со входом разрешения переноса второго счетчика адреса, выход переноса которого соединен через второй резистор с первым входом логического элемента И-НЕ, первый вход первого логического элемента ИЛИ является пятым входом управления преобразователя, инверсный выход первого триггера соединен со входами выбора микросхемы первого и второго запоминающих устройств, вход разрешения параллельной загрузки данных, вход разрешения счета, вход разрешения переноса первого счетчика временных интервалов, вход разрешения параллельной загрузки данных, вход разрешения счета второго счетчика временных интервалов объединены между собой и соединены со вторым входом пятого логического элемента И и с прямым выходом третьего триггера, вход установки в состояние логического нуля которого соединен с выходом первого логического элемента ИЛИ-НЕ, а вход установки в состояние логической единицы третьего триггера соединен с выходом четвертого логического элемента НЕ, вход которого соединен с первым входом второго логического элемента ИЛИ-НЕ и с выходом переноса счетчика защитного интервала, вход разрешения параллельной загрузки данных, вход разрешения счета и вход разрешения переноса которого объединены и соединены с прямым выходом четвертого триггера, вход установки в состояние логического нуля которого соединен с выходом второго логического элемента ИЛИ-НЕ, тактовые входы первого и второго счетчиков временных интервалов объединены и соединены с тактовым входом счетчика защитных интервалов и с выходом третьего логического элемента И, первый вход которого является седьмым входом управления преобразователя, а второй вход соединен с прямым выходом второго триггера, вход установки в состояние логической единицы которого соединен с выходом третьего логического элемента ИЛИ и со входом второго логического элемента НЕ, выход которого соединен со вторым входом третьего логического элемента ИЛИ-НЕ, выход данных D1 первого счетчика временных интервалов соединен с первым входом четвертого логического элемента ИЛИ-НЕ, выход которого соединен со вторыми входами седьмого и восьмого логических элементов И, выходы которых являются соответствующими выходами преобразователя, вход седьмого логического элемента НЕ соединен с выходом четвертого логического элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом пятого триггера, вход установки в состояние логического нуля которого соединен с выходом пятого логического элемента И.

| Программируемый преобразователь код-временной интервал | 1978 |

|

SU752797A1 |

| Преобразователь код - временной интервал | 1989 |

|

SU1736000A1 |

| МЕТОД УВЕЛИЧЕНИЯ СКОРОСТИ ЦИФРО-АНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ | 2012 |

|

RU2544738C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

Авторы

Даты

2017-09-07—Публикация

2016-11-21—Подача