Изобретение относится к области радиоэлектроники и может быть использовано в качестве устройств усиления широкополосных сигналов.

В современных аналоговых микросхемах находят широкое применение дифференциальные усилители токов (ДУТ), выполненные на основе двух токовых зеркал [1-19]. Данное схемотехническое решение является основой многих подклассов операционных усилителей, стабилизаторов напряжения, компараторов и т.п. [20].

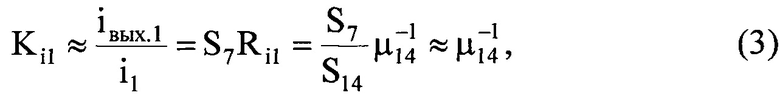

Ближайшим прототипом заявляемого устройства является дифференциальный усилитель тока (входной каскад операционного усилителя (ОУ) по патенту US 8.130.038, fig. 2, а также схема ДУТ по патенту US 7.701.290, fig. 6). Он содержит (фиг. 1) первый 1 и второй 2 токовые входы, связанные с соответствующими выходами дифференциального источника сигнала 3, согласованного с первой 4 шиной источника питания, первый 5 вспомогательный транзистор, затвор которого соединен со стоком и подключен к первому 1 токовому входу, второй 6 вспомогательный транзистор, затвор которого соединен со стоком и подключен ко второму 2 токовому входу, первый 7 выходной транзистор, сток которого соединен с первым 8 токовым выходом устройства, а исток подключен ко второй 9 шине источника питания, второй 10 выходной транзистор, сток которого подключен ко второму 11 токовому выходу устройства, а исток соединен со второй 9 шиной источника питания.

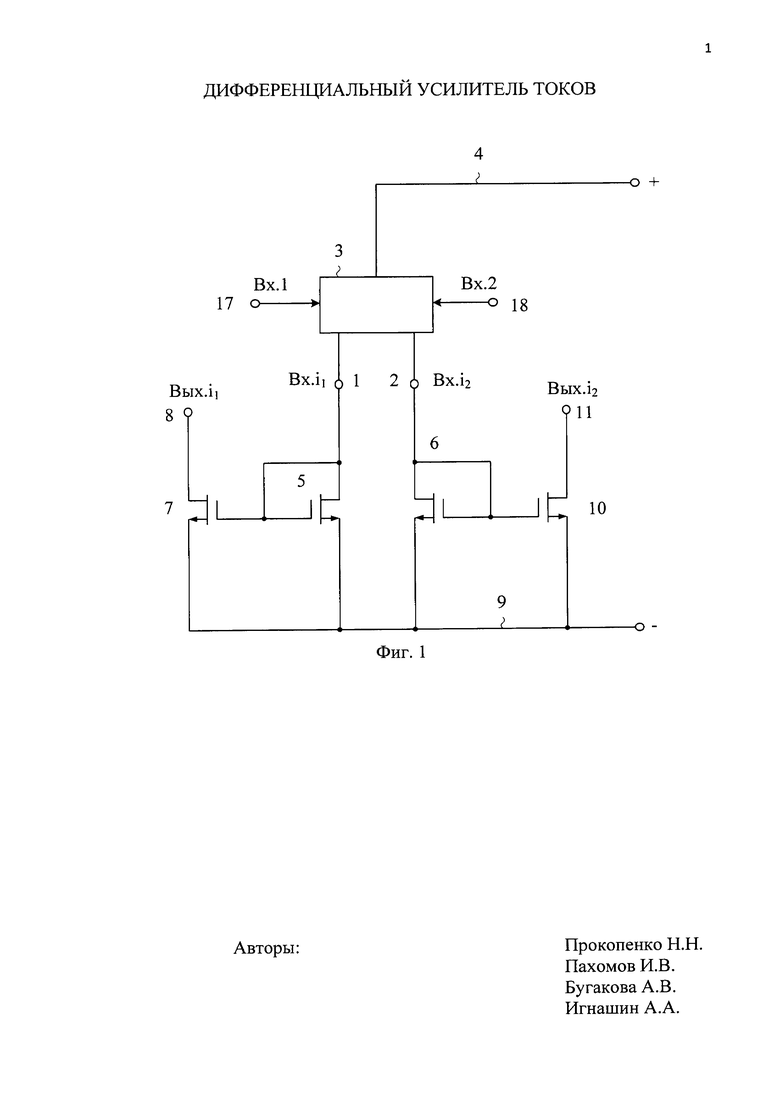

Существенный недостаток известного ДУТ состоит в том, что он имеет невысокий дифференциальный коэффициент усиления по току, который на практике определяется отношением площадей первого 5 вспомогательного и первого 7 выходного транзисторов (второго 6 вспомогательного и второго 10 выходного транзисторов). Как следствие, на базе известного ДУТ не реализуются, например, операционные усилители с повышенным коэффициентом усиления.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления по току ДУТ при сохранении у него опции rail-to-rail.

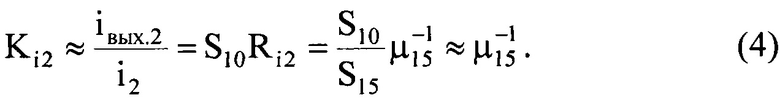

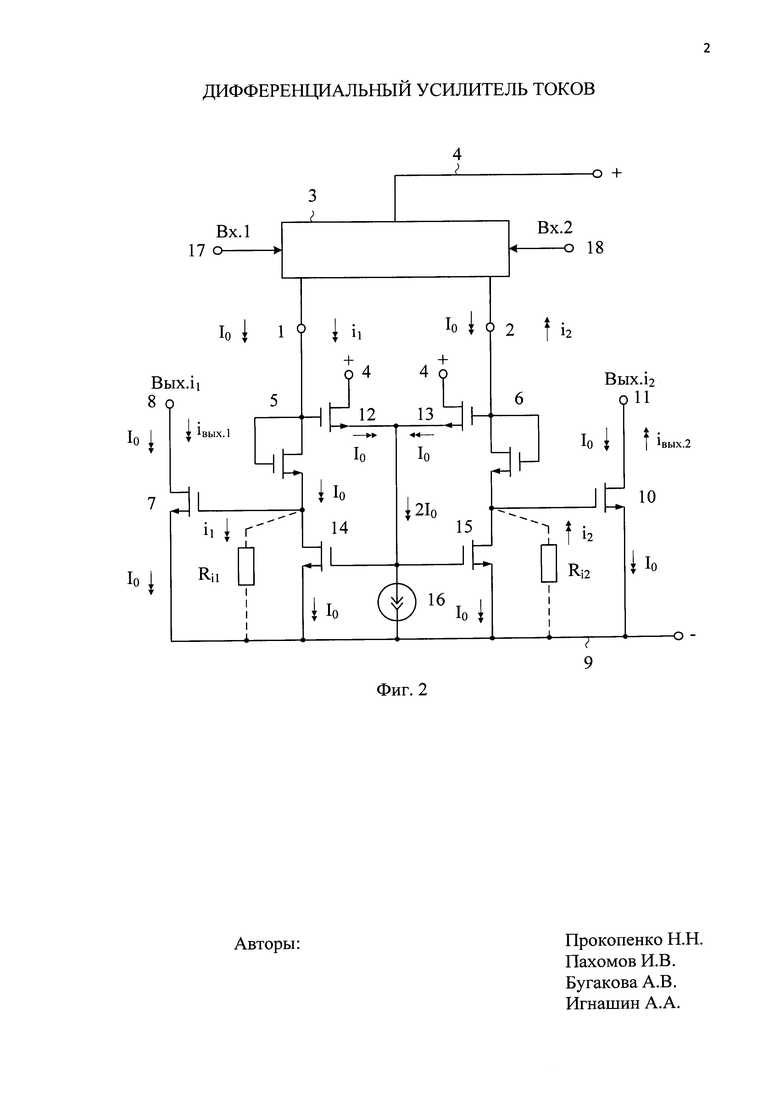

Поставленная задача достигается тем, что в дифференциальном усилителе фиг. 1, содержащем первый 1 и второй 2 токовые входы, связанные с соответствующими выходами дифференциального источника сигнала 3, согласованного с первой 4 шиной источника питания, первый 5 вспомогательный транзистор, затвор которого соединен со стоком и подключен к первому 1 токовому входу, второй 6 вспомогательный транзистор, затвор которого соединен со стоком и подключен ко второму 2 токовому входу, первый 7 выходной транзистор, сток которого соединен с первым 8 токовым выходом устройства, а исток подключен ко второй 9 шине источника питания, второй 10 выходной транзистор, сток которого подключен ко второму 11 токовому выходу устройства, а исток соединен со второй 9 шиной источника питания, предусмотрены новые элементы и связи - в схему введены первый 12, второй 13, третий 14 и четвертый 15 дополнительные транзисторы, затвор первого 12 дополнительного транзистора соединен с первым 1 токовым входом устройства, затвор второго 13 дополнительного транзистора соединен со вторым 2 токовым входом устройства, стоки первого 12 и второго 13 дополнительных транзисторов согласованы с первой 4 шиной источника питания, сток третьего 14 дополнительного транзистора соединен с затвором первого 7 выходного транзистора и истоком первого 5 вспомогательного транзистора, сток четвертого 15 дополнительного транзистора соединен с затвором второго 10 выходного транзистора и истоком второго 6 вспомогательного транзистора, причем истоки первого 12 и второго 13 дополнительных транзисторов подключены к затворам третьего 14 и четвертого 15 дополнительных транзисторов, а истоки третьего 14 и четвертого 15 дополнительных транзисторов связаны со второй 9 шиной источника питания.

На чертеже фиг. 1 показана схема ДУТ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

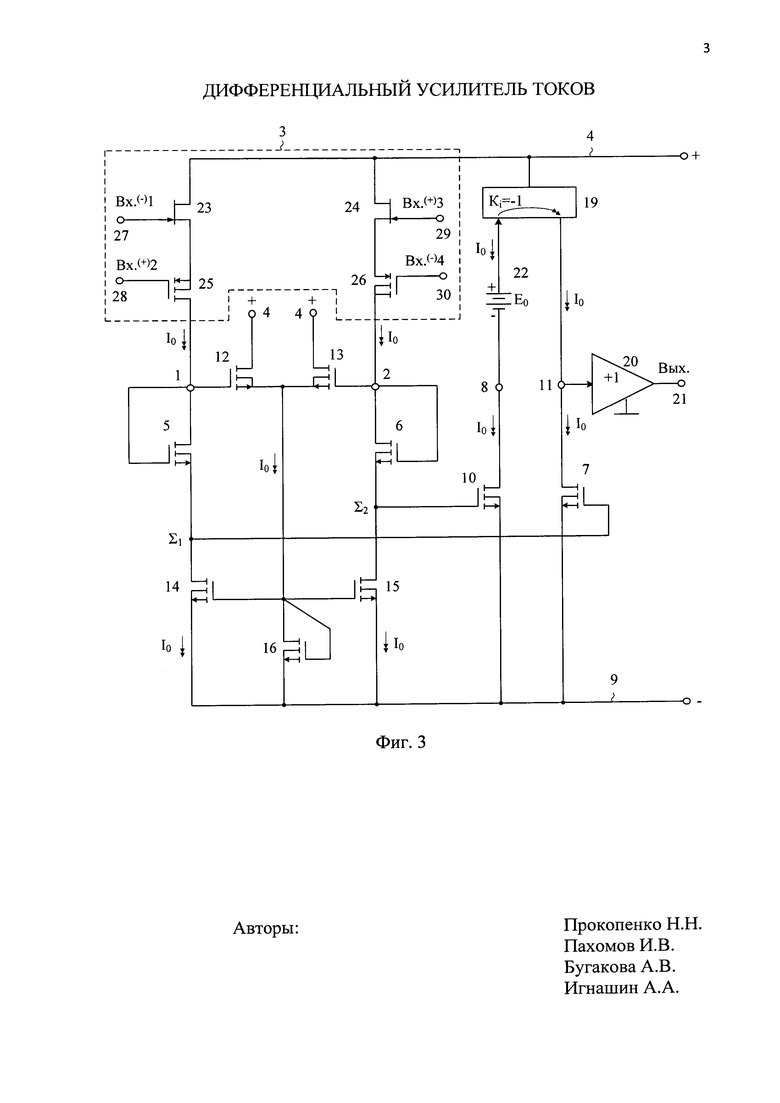

На чертеже фиг. 3, соответствующем п.3 и 4 формулы изобретения, показана схема включения заявляемого ДУТ с конкретным выполнением дифференциального источника сигнала 3.

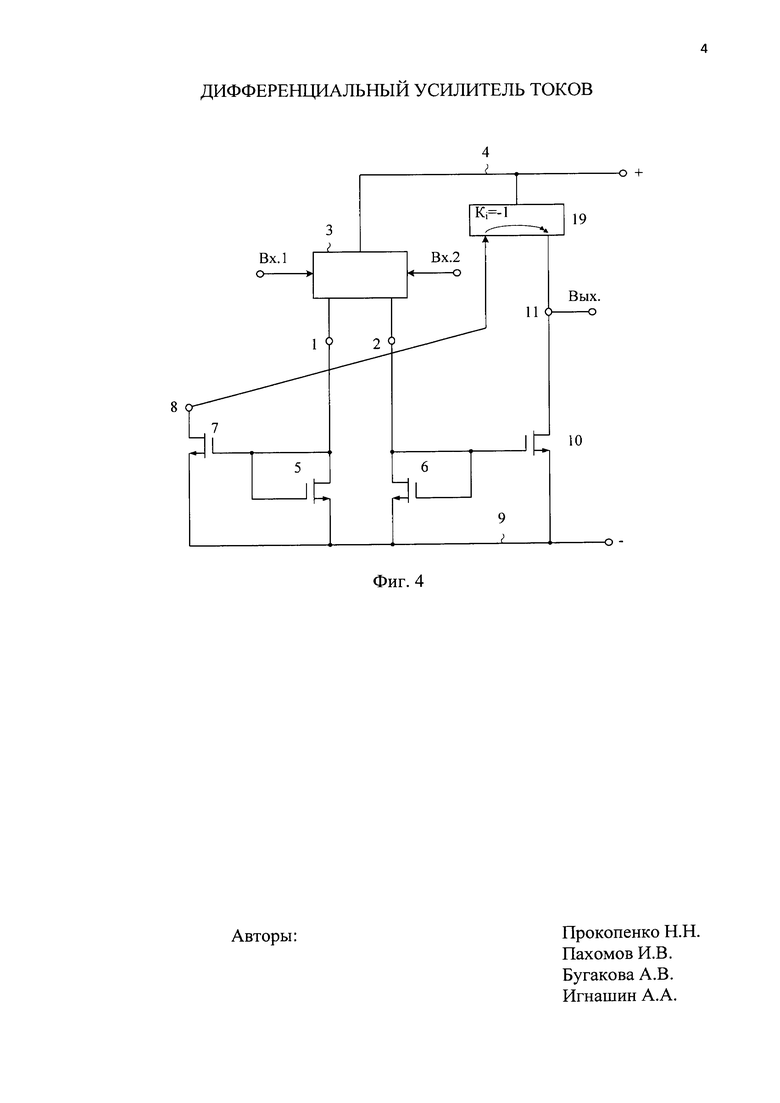

На чертеже фиг. 4 приведена схема включения ДУТ-прототипа в структуре операционного усилителя с опцией rail-to-rail, для которой было проведено сравнительное (с фиг. 3) компьютерное моделирование разомкнутого коэффициента усиления.

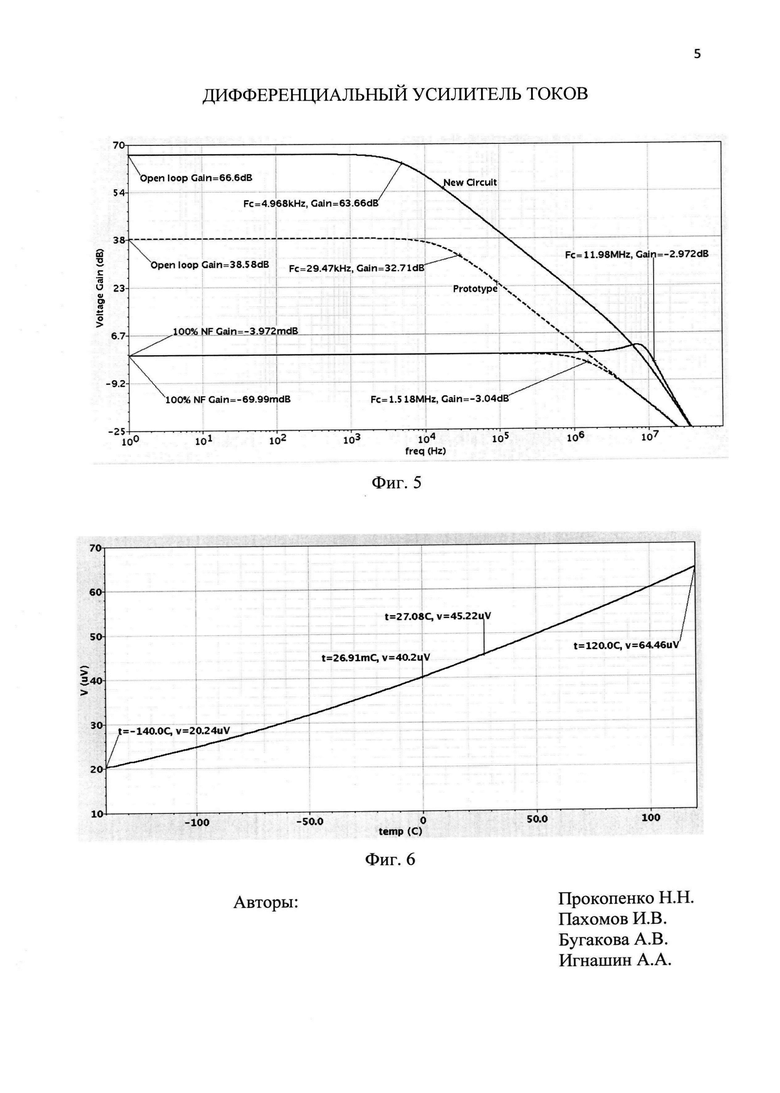

На чертеже фиг. 5 показаны результаты сравнительного моделирования амплитудно-частотной характеристики схемы ОУ с ДУ-прототипом (фиг. 4) и схемы ОУ с заявляемым ДУТ (фиг. 3). Моделирование осуществлялось в среде Cadence на моделях транзисторов XFab для случая, когда сравниваемые ОУ имели 100% отрицательную обратную связь, а также для разомкнутого включения ОУ.

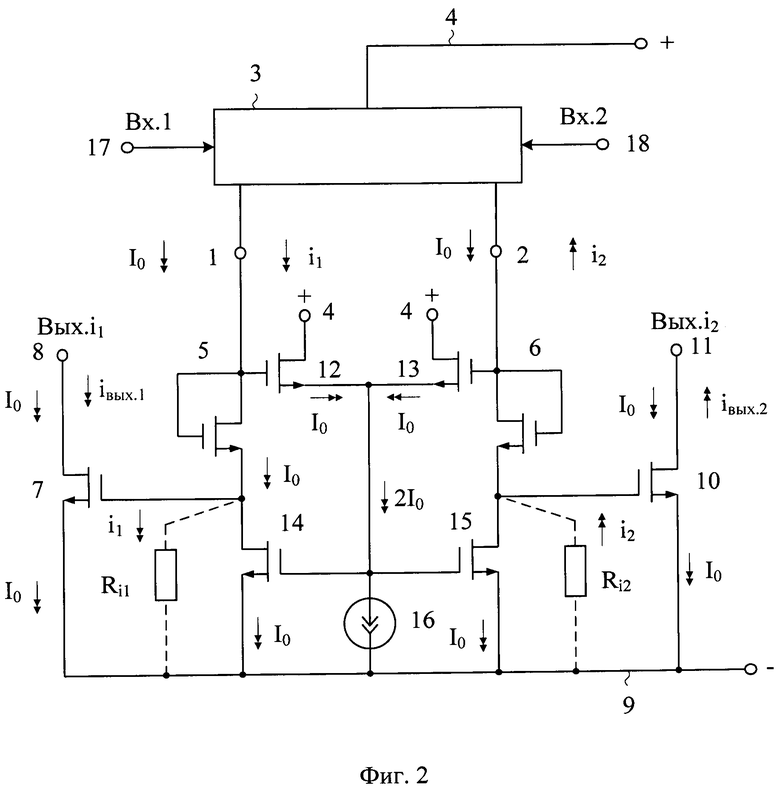

На чертеже фиг. 6 приведена зависимость напряжения смещения нуля (Vos) ОУ фиг. 3 на основе предлагаемого ДУТ от температуры (-140С÷+120С).

Дифференциальный усилитель токов фиг. 2 содержит первый 1 и второй 2 токовые входы, связанные с соответствующими выходами дифференциального источника сигнала 3, согласованного с первой 4 шиной источника питания, первый 5 вспомогательный транзистор, затвор которого соединен со стоком и подключен к первому 1 токовому входу, второй 6 вспомогательный транзистор, затвор которого соединен со стоком и подключен ко второму 2 токовому входу, первый 7 выходной транзистор, сток которого соединен с первым 8 токовым выходом устройства, а исток подключен ко второй 9 шине источника питания, второй 10 выходной транзистор, сток которого подключен ко второму 11 токовому выходу устройства, а исток соединен со второй 9 шиной источника питания. В схему введены первый 12, второй 13, третий 14 и четвертый 15 дополнительные транзисторы, затвор первого 12 дополнительного транзистора соединен с первым 1 токовым входом устройства, затвор второго 13 дополнительного транзистора соединен со вторым 2 токовым входом устройства, стоки первого 12 и второго 13 дополнительных транзисторов согласованы с первой 4 шиной источника питания, сток третьего 14 дополнительного транзистора соединен с затвором первого 7 выходного транзистора и истоком первого 5 вспомогательного транзистора, сток четвертого 15 дополнительного транзистора соединен с затвором второго 10 выходного транзистора и истоком второго 6 вспомогательного транзистора, причем истоки первого 12 и второго 13 дополнительных транзисторов подключены к затворам третьего 14 и четвертого 15 дополнительных транзисторов, а истоки третьего 14 и четвертого 15 дополнительных транзисторов связаны со второй 9 шиной источника питания.

В частном случае в качестве дифференциального источника сигнала 3 в схеме фиг. 2 могут использоваться дифференциальные датчики тока, а также классические дифференциальные каскады со входами 17 и 18, применяемые, например, в операционных усилителях и стабилизаторах напряжения и т.п.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, истоки первого 12 и второго 13 дополнительных транзисторов связаны со второй 9 шиной источника питания через токостабилизирующий двухполюсник 16. В частном случае, в качестве токостабилизирующего двухполюсника могут применяться резисторы, источники опорного тока, а также полевые транзисторы с объединенными выводами стока и затвора (фиг. 3).

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, первый 8 токовый выход устройства подключен ко входу дополнительного токового зеркала 19, согласованного с первой 4 шиной источника питания, выход которого подключен ко второму 11 токовому выходу устройства.

Кроме этого, на чертеже фиг.3, в соответствии с п. 4 формулы изобретения, второй 11 токовый выход устройства соединен со входом дополнительного буферного усилителя 20, выход которого 21 является дополнительным потенциальным выходом устройства.

На чертеже фиг. 3 первый 8 токовый выход устройства подключен ко входу дополнительного токового зеркала 19 через цепь согласования потенциалов 22, способствующую уменьшению нулевого уровня ОУ.

В схеме фиг. 3 дифференциальный источник сигнала 3 реализован в частном случае на полевых транзисторах 23, 24, 25, 26, затворы которых являются входами 27, 28, 29 и 30 мультидифференциального операционного усилителя на основе заявляемого ДУТ.

Рассмотрим работу ДУТ в схеме фиг. 3.

Особенность ДУТ фиг. 3 состоит в том, что в нем обеспечивается стабилизация статического режима за счет введения отрицательной обратной связи по синфазному сигналу, который выделяется на входах 1 и 2. В результате в схеме фиг. 3 при идентичных полевых транзисторах устанавливаются следующие уровни статических токов стоков первого 5 и второго 6 вспомогательных транзисторов, третьего 14 и четвертого 15 дополнительных транзисторов, а также первого 7 и второго 10 выходных транзисторов:

Iс5=Iс6=I0, Ic14=Ic15=I0, Iс7=Iс10=I0,

где I0 - статический ток первого 1 и второго 2 токовых входов, который задается дифференциальным источником сигнала 3.

Повышенный коэффициент усиления по току в схеме рис. 3 реализуется благодаря высокому значению эквивалентного сопротивления на первом 1 и втором 2 токовых входах:

где S14, S15 - крутизна стокозатворной характеристики соответствующих полевых транзисторов (14, 15),

μ14, μ15 _ коэффициенты внутренней обратной связи соответствующих транзисторов (14, 15), характеризующие влияние напряжения на стоке на напряжение затвор-исток (μ=ΔUзи/ΔUсз при Iи=const).

Как следствие, коэффициент усиления по току предлагаемого ДУТ существенно возрастает

Если считать, что μ14≈μ15≈10-2, то при S7=S14, S10=S15 из (3), (4) получаем, что теоретическое значение Ki1≈Ki2≈100. Заметим, что в ДУ-прототипе Ki=l.

Как показывает эксперимент (фиг. 5), предлагаемый дифференциальный усилитель токов имеет (в сравнении с прототипом) на 30 дБ более высокий коэффициент усиления, а также характеризуется повышенной верхней граничной частотой при 100% обратной связи, которая в 8 раз выше аналогичного параметра ДУТ-прототипа.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с известным техническим решением.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.008.667, fig. 1.

2. Патентная заявка US 2008/0278232, fig. 1, fig. 3.

3. Патент US 6.429.735.

4. Патентная заявка US 2005/0017809.

5. Патент US 7.405.622, fig. 3.

6. Патентная заявка US 2006/0226908.

7. Патентная заявка US 2008/0079491, fig. 1.

8. Патентная заявка US 2004/0189386.

9. Патентная заявка US 2004/0174216, fig. 1.

10. Патентная заявка US 2003/0206060, fig. 1.

11. Патент US 6.794.940, fig. 9.

12. Патент US 5.831.480.

13. Патентная заявка US 2006/0226877, fig. 3.

14. Патентная заявка US 2010/0301917, fig. 3.

15. Патент US 8.130.038.

16. Патентная заявка US 2003/0076163, fig. 2.

17. Патентная заявка US 2003/0132803, fig. 4.

18. Патент US 7.183.852, fig. 3.

19. Патентная заявка US 2009/0237163.

20. Эннс В.И., Кобзев Ю.М. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика /Под редакцией канд. техн. наук В.И. Эннса. - М.: Горячая линия-Телеком. - 2005. - 454 с.-С. 207. - Рис. 3.82

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ДВУХКАСКАДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2721942C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ КРУТИЗНОЙ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770915C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2739577C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2021 |

|

RU2766861C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736412C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

Изобретение относится к устройствам усиления широкополосных сигналов. Технический результат заключается в повышении коэффициента усиления по току ДУТ при сохранении у него опции rail-to-rail. Дифференциальный усилитель токов содержит первый, второй, третий и четвертый дополнительные транзисторы, затвор первого дополнительного транзистора соединен с первым токовым входом устройства, затвор второго дополнительного транзистора соединен со вторым (2) токовым входом устройства, стоки первого и второго дополнительных транзисторов согласованы с первой шиной источника питания, сток третьего дополнительного транзистора соединен с затвором первого выходного транзистора и истоком первого вспомогательного транзистора, сток четвертого дополнительного транзистора соединен с затвором второго выходного транзистора и истоком второго вспомогательного транзистора, причем истоки первого и второго дополнительных транзисторов подключены к затворам третьего и четвертого дополнительных транзисторов, а истоки третьего и четвертого дополнительных транзисторов связаны со второй шиной источника питания. 3 з.п. ф-лы, 6 ил.

1. Дифференциальный усилитель токов, содержащий первый (1) и второй (2) токовые входы, связанные с соответствующими выходами дифференциального источника сигнала (3), согласованного с первой (4) шиной источника питания, первый (5) вспомогательный транзистор, затвор которого соединен со стоком и подключен к первому (1) токовому входу, второй (6) вспомогательный транзистор, затвор которого соединен со стоком и подключен ко второму (2) токовому входу, первый (7) выходной транзистор, сток которого соединен с первым (8) токовым выходом устройства, а исток подключен ко второй (9) шине источника питания, второй (10) выходной транзистор, сток которого подключен ко второму (11) токовому выходу устройства, а исток соединен со второй (9) шиной источника питания, отличающийся тем, что в схему введены первый (12), второй (13), третий (14) и четвертый (15) дополнительные транзисторы, затвор первого (12) дополнительного транзистора соединен с первым (1) токовым входом устройства, затвор второго (13) дополнительного транзистора соединен со вторым (2) токовым входом устройства, стоки первого (12) и второго (13) дополнительных транзисторов согласованы с первой (4) шиной источника питания, сток третьего (14) дополнительного транзистора соединен с затвором первого (7) выходного транзистора и истоком первого (5) вспомогательного транзистора, сток четвертого (15) дополнительного транзистора соединен с затвором второго (10) выходного транзистора и истоком второго (6) вспомогательного транзистора, причем истоки первого (12) и второго (13) дополнительных транзисторов подключены к затворам третьего (14) и четвертого (15) дополнительных транзисторов, а истоки третьего (14) и четвертого (15) дополнительных транзисторов связаны со второй (9) шиной источника питания.

2. Дифференциальный усилитель токов по п. 1, отличающийся тем, что истоки первого (12) и второго (13) дополнительных транзисторов связаны со второй (9) шиной источника питания через токостабилизирующий двухполюсник (16).

3. Дифференциальный усилитель токов по п. 1, отличающийся тем, что первый (8) токовый выход устройства подключен ко входу дополнительного токового зеркала (19), согласованного с первой (4) шиной источника питания, выход которого подключен ко второму (11) токовому выходу устройства.

4. Дифференциальный усилитель токов по п. 3, отличающийся тем, что второй (11) токовый выход устройства соединен со входом дополнительного буферного усилителя (20), выход которого (21) является дополнительным потенциальным выходом устройства.

| US 8130038 B2, 06.03.2012 | |||

| US 7701290 B2, 20.04.2010 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2016 |

|

RU2621291C1 |

Авторы

Даты

2018-04-18—Публикация

2017-05-31—Подача