Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, выполненных на R-S триггерах.

Известен асинхронный R-S триггер [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. – М.: Высшая школа, 2004, с. 620, рис. 8.19, а] содержащий два логических элемента ИЛИ-НЕ.

Недостатком его является большое число используемых транзисторов, что усложняет и удорожает устройство. В частности, в каждом двухвходовом эмиттерно-связанном логическом элементе ИЛИ-НЕ [Манаев Е.И. Основы радиоэлектроники. – М.: Радио и связь, 1985, с. 342, рис. 14.23] имеется пять транзисторов, тогда в обсуждаемом асинхронном R-S-триггере содержится большое число транзисторов (десять), что приводит к его усложнению и удорожанию.

Наиболее и близким по технической сущности и достигаемому результату является выбранный в качестве прототипа R-S триггер на МДП транзисторах с индуцированными каналами [Гольденберг Л.М. Импульсные устройства. – М.: Радио и связь, 1981, с. 103, рис. 4.15, а], содержащий шесть полевых транзисторов и источник питающего постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность, так как на прямом выходе Q электрический ток внешней нагрузки формируется только одним из имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовало большее число из имеющихся транзисторов, то это повысило бы нагрузочную способность триггера.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного асинхронного R-S триггера на полевых транзисторах.

Это достигается тем, что в триггерный асинхронный R-S триггер на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, три полевых транзистора с индуцированными каналами n-типа, исток и подложка первого полевого транзистора заземлены, а затвор его образует относительно «земли» вход S триггера на полевых транзисторах, сток второго полевого транзистора соединен со стоком первого транзистора, а подложка подключена к его истоку, исток и подложка третьего полевого транзистора заземлены, а затвор образует относительно «земли» вход R триггера на полевых транзисторах, введены четыре резистора, дополнительный полевой транзистор с индуцированным каналом p-типа и изменено соединение элементов, первый резистор включен между выходом источника питающего постоянного напряжения и общим выводом стоков первого и второго полевых транзисторов, один из выводов второго резистора подсоединен к общему выводу истока и подложки второго полевого транзистора, последовательно между собой включены третий резистор, дополнительный полевой транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, подложка дополнительного полевого транзистора соединена с его истоком и их общий вывод совместно с третьим резистором подключен к стоку третьего полевого транзистора, затвор дополнительного полевого транзистора соединен с общим выводом первого резистора и стоков первого и второго транзисторов, свободный вывод четвертого резистора подключен к свободному выводу второго резистора и их общий вывод образует выход относительно «земли» асинхронного R-S триггера, общий вывод четвертого резистора и стока дополнительного полевого транзистора соединен с затвором второго полевого транзистора.

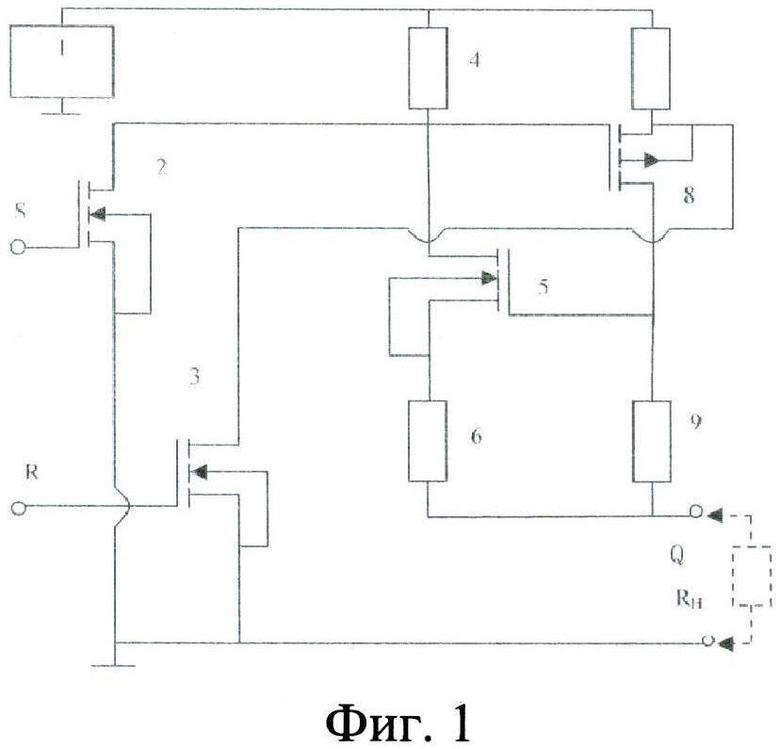

Сущность изобретения поясняется чертежом (фиг. 1).

В триггерном асинхронном R-S триггере на полевых транзисторах общая шина источника 1 питающего постоянного напряжения заземлена. Истоки и подложки полевых транзисторов 2 и 3 с индуцированными каналами n-типа тоже заземлены. Затвор полевого транзистора 2 образует вход S относительно «земли» асинхронного R-S триггера, а затвор транзистора 3 образует вход R. Последовательно между собой включены резистор 4, полевой транзистор 5 с индуцированным каналом n-типа и резистор 6. Свободный вывод резистора 4 подключен к выходу (плюсовой вывод) источника 1 питающего постоянного напряжения. Общий вывод резистора 4 и стока полевого транзистора 5 соединен со стоком полевого транзистора 2. Подложка полевого транзистора 5 подсоединена к его истоку. Также между собой последовательно включены резистор 7, полевой транзистор 8 с индуцированным каналом p-типа и резистор 9. Свободный вывод резистора 7 подсоединен к общему выводу резистора 4 и выхода источника 1 питающего постоянного напряжения. Подложка транзистора 8 подключена к его истоку и их общий вывод совместно с резистором 7 соединен со стоком полевого транзистора 3. Затвор полевого транзистора 8 подключен к общему выводу резистора 4 и стоков двух полевых транзисторов 2 и 5. Общий вывод стока полевого транзистора 8 и резистора 9 подсоединен к затвору резистора 5. Свободный вывод резистора 9 соединен со свободным выводом резистора 6 и их общий вывод образует выход Q относительно «земли» асинхронного R-S триггера. Для наглядности на фиг. 1 пунктирными линиями показано подключение внешней нагрузки RH к выходу асинхронного R-S триггера. Часть схемы на полевых транзисторах 5, 8 и резисторах 4, 6, 7 и 9является триггером на транзисторах противоположного типа проводимости.

Триггерный асинхронный R-S триггер на полевых транзисторах работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень – уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень – уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко четыре вольта).

Работа асинхронного R-S триггера отображается известной табл. 1, где Rt и St – условное отображение сигналов на входах R-S триггера в данный момент времени, Qt+1 условное отображение состояния триггера в последующее время (состояние на выходе) и N-номер строки по порядку.

Табл. 1

2

3

4

1

0

1

0

0

1

Установка 0

Хранение

Запрет

Триггер на транзисторах 5 и 8 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 4 и 9 нулевые значения напряжения. Они прикладываются к затворам транзисторов 5 и 8 , меньше их пороговых напряжений по абсолютной величине и поддерживают транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 5 и 8 открыты, их электрические токи создают напряжения в том числе на резисторах 4 и 9 большие по значениям пороговых напряжений транзисторов по абсолютной величине и поддерживают эти транзисторы в открытом состоянии. Триггер на транзисторах противоположного типа проводимости переходит из первого состояния во второе и наоборот, когда управляющие напряжения превышают соответствующие пороги срабатывания триггера.

При комбинации входных сигналов, соответствующих первой строке табл. 1, низкий уровень напряжения на входе R определяет низкое (малое) значение силы электрического тока через полевой транзистор 3 и соответственно через резистор 7. Тогда на резисторе 7 низкое значение напряжения, меньше порога срабатывания триггера на транзисторах 5, 8 и не влияет на его состояние. Высокий уровень напряжения на входе S (табл. 1) определяет повышенную силу электрического тока транзистора 2, повышенное значение напряжения на резисторе 4, превышающее порог срабатывания триггера на транзисторах 5 и 8. Триггер на транзисторах противоположного типа проводимости теперь во втором состоянии и электрические токи его двух транзисторов создают на внешней нагрузке RH и на выходе Q повышенное значение напряжения – уровень логической единицы.

При комбинации входных сигналов, соответствующих второй строке табл.1, низкий уровень напряжения на входе S предопределяет низкие значения силы электрического тока транзистора 2 и напряжения на резисторе 4. Последнее меньше порога срабатывания триггера на транзисторах 5, 8 и не влияет на состояние этого триггера. Высокий уровень напряжения на входе R вызывает повышенные значения силы электрического тока транзистора 3 и напряжения на резисторе 7. Последнее больше порога срабатывания триггера на транзисторах 5, 8 и в результате этот триггер теперь в первом состоянии. Нулевые значения силы электрического тока двух его транзисторов создают на внешней нагрузке RH и на выходе Q напряжение уровня логического нуля.

При комбинации входных сигналов, соответствующих третьей строке табл. 1, низкие уровни значений напряжений на входах R и S предопределяют пониженные силы электрических токов транзисторов 2, 3 и низкие уровни управляющих напряжений для триггера на транзисторах 5, 8. Эти напряжения меньше пороговых напряжений и триггер на транзисторах 5, 8 не изменяет свое имеющееся состояние. Тогда не изменяется напряжение на выходе R-S триггера, и оно соответствует предыдущей комбинации входных сигналов. То есть это хранение информации.

Комбинация сигналов в четверной строке табл. 1, как и в существующих схемах асинхронных R-S триггеров, так и в рассматриваемой схеме, является запрещенной комбинацией входных сигналов.

Таким образом, электрический ток внешней нагрузки триггерного асинхронного R-S триггера на полевых транзисторах формируют два транзистора 5 и 8, что повышает его нагрузочную способность. В прототипе электрический ток внешней нагрузки формирует только один из имеющихся транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный асинхронный D триггер на полевых транзисторах | 2018 |

|

RU2689197C1 |

| Триггерный асинхронный D триггер на полевых транзисторах | 2022 |

|

RU2789081C1 |

| Триггерный синхронный R-S триггер на полевых транзисторах | 2018 |

|

RU2702051C1 |

| Триггерный двухступенчатый D триггер на полевых транзисторах | 2020 |

|

RU2734428C1 |

| Триггерный синхронный D триггер на полевых транзисторах | 2018 |

|

RU2693301C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2023 |

|

RU2817236C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ на полевых транзисторах | 2023 |

|

RU2813863C1 |

| Триггерный логический элемент И на полевых транзисторах | 2023 |

|

RU2807036C1 |

| Триггерный логический элемент И/И-НЕ на полевых транзисторах | 2024 |

|

RU2827120C1 |

| Триггерный логический элемент И/ИЛИ на полевых транзисторах | 2023 |

|

RU2813862C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, выполненных на R-S триггерах. Технический результат - повышение нагрузочной способности триггерного асинхронного R-S триггера на полевых транзисторах. Для этого предложен триггерный асинхронный R-S триггер на полевых транзисторах, который содержит четыре полевых транзистора, четыре резистора и источник питающего постоянного напряжения. Новым является то, что в него введены четыре резистора, дополнительный полевой транзистор с индуцированным каналом p-типа и изменено соединение элементов. 1 ил., 1 табл.

Триггерный асинхронный R-S триггер на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, три полевых транзистора с индуцированными каналами n-типа, исток и подложка первого полевого транзистора заземлены, а затвор его образует относительно «земли» вход S триггера на полевых транзисторах, сток второго полевого транзистора соединен со стоком первого транзистора, а подложка подключена к его истоку, исток и подложка третьего полевого транзистора заземлены, а затвор образует относительно «земли» вход R триггера на полевых транзисторах, отличающийся тем, что в него введены четыре резистора, дополнительный полевой транзистор с индуцированным каналом p-типа и изменено соединение элементов, первый резистор включен между выходом источника питающего постоянного напряжения и общим выводом стоков первого и второго полевых транзисторов, один из выводов второго резистора подсоединен к общему выводу истока и подложки второго полевого транзистора, последовательно между собой включены третий резистор, дополнительный полевой транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, подложка дополнительного полевого транзистора соединена с его истоком и их общий вывод совместно с третьим резистором подключен к стоку третьего полевого транзистора, затвор дополнительного полевого транзистора соединен с общим выводом первого резистора и стоков первого и второго транзисторов, свободный вывод четвертого резистора подключен к свободному выводу второго резистора и их общий вывод образует выход относительно «земли» асинхронного R-S триггера, общий вывод четвертого резистора и стока дополнительного полевого транзистора соединен с затвором второго полевого транзистора.

| ГОЛЬДЕНБЕРГ Л.М., Импульсные устройства, Москва, Радио и Связь, 1981, стр | |||

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| RS-ТРИГГЕР | 2015 |

|

RU2615069C1 |

| US 8232825 B2, 31.07.2012. | |||

Авторы

Даты

2019-07-02—Публикация

2018-10-16—Подача