Изобретение относится к вычислительной технике, в частности к схемам многопортовой оперативной и сверхоперативной биполярной памяти в интегральном исполнении.

Цель изобретения - повышение быстродействия и помехоустойчивости и упрощение элемента.

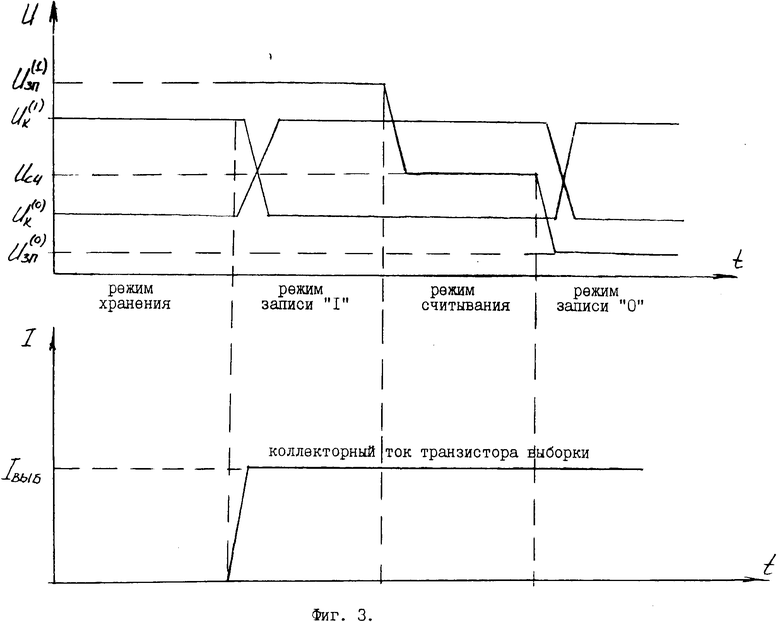

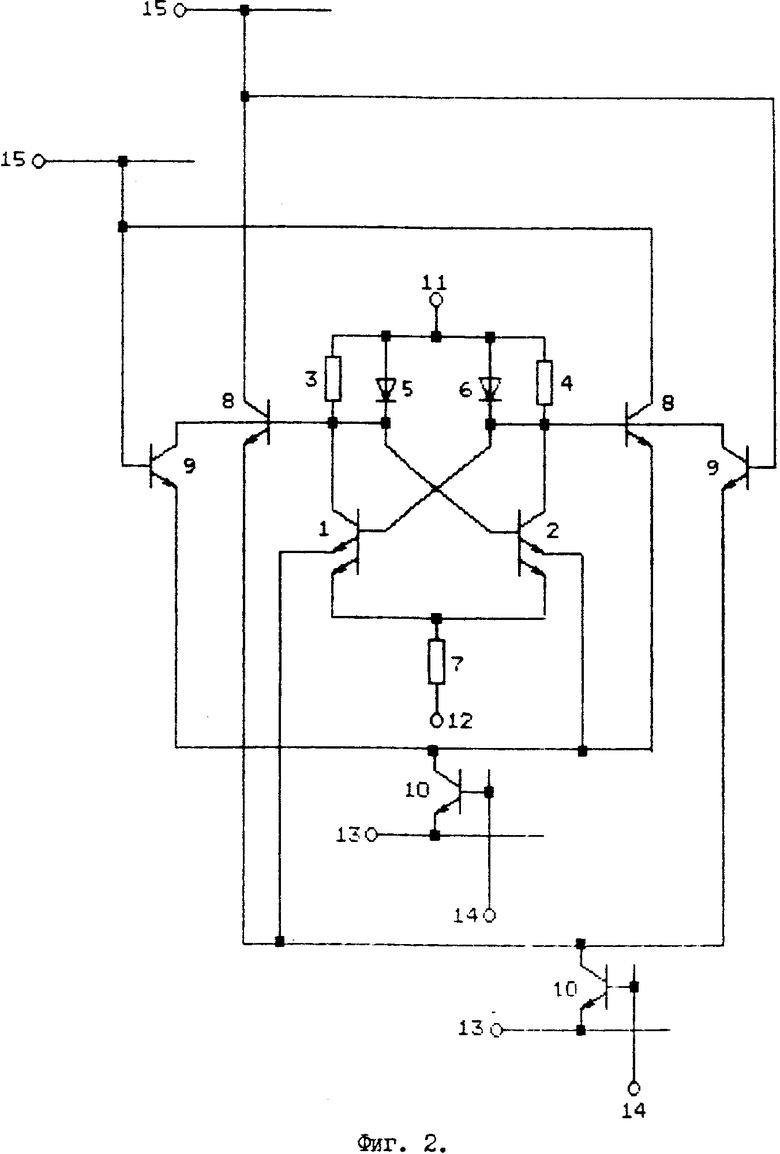

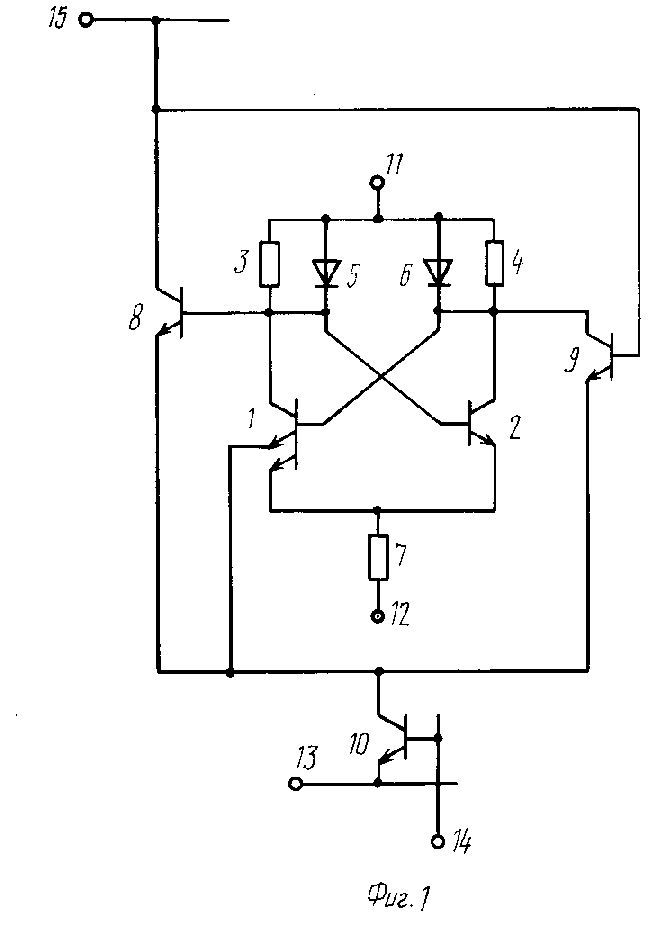

На фиг. 1 представлена электрическая схема предложенного элемента памяти (однопортового); на фиг. 2 - пример двухпортового элемента памяти (в общем случае элемент памяти может содержать несколько портов); на фиг. 3 - временная диаграмма работы элемента памяти во всех основных режимах его работы.

Элемент памяти реализован на биполярных транзисторах n-p-n-структуры. Он содержит первый 1 и второй 2 запоминающие транзисторы, первый 3 и второй 4 нагрузочные резисторы, первый 5 и второй 6 фиксирующие диоды, третий 7 нагрузочный резистор, первый 8 и второй 9 транзисторы связи, транзистор 10 выборки, первую 11 и вторую 12 шины питания, второй 13 и первый 14 входы сигналов выборки, информационный вход-выход 15.

Рассмотрим принцип работы одного порта элемента памяти.

В режиме хранения транзистор 10 не рекомендует ток выборки в триггер на транзисторах 1 и 2, разность потенциалов в котором обеспечивается протеканием тока, задаваемого от шины 12 питания через резистор 7. Шины 11, 12 питания могут быть общими для всего массива элементов памяти в накопителе (допускают произвольное объединение по строкам и столбцам в матрице, включая и одновременное объединение и по строкам, и по столбцам). При коммутации тока выборки элемент памяти может работать в трех основных режимах: режиме считывания, режиме записи "0", режиме записи "1".

В режиме считывания на вход-выход 15 подается потенциал считывания Uсч. Соотношение потенциалов задается следующим:

Uсч < Uк(1) , где Uк(1) - потенциал логической "1" в триггере элемента памяти. При таком соотношении уровней ток выборки протекает либо через эмиттер транзистора 8, либо через эмиттер транзистора 1, коллектор которого подключен к базе транзистора 8, в зависимости от логического состояния элемента памяти. Если на базе транзистора 8 имеется потенциал логической "1", то ток выборки протекает через открытый транзистор 8, в противном случае через запоминающий транзистор 1, коллектор которого подключен к базе транзистора 8 связи, поддерживая током выборки логическое состояние элемента памяти.

В режиме записи "0" на вход-выход 15 подается потенциал записи "0". Соотношение потенциалов задается следующим:

Uзп(о) ≅Uк(1) - UБКнас, где UБКнас - напряжение на коллекторном переходе транзистора 8 связи в режиме насыщения с нулевым коллектором током. При этом, если на базе транзистора 8 в начальный момент времени был потенциал Uк(1), то ток выборки протекает через базу насыщенного транзистора 8, понижая потенциал логической "1". Как только потенциал базы транзистора 8 опустится ниже потенциала Uк(о), происходит динамическое переключение тока в триггер через эмиттер транзистора 1, коллектор которого подключен к базе транзистора 8. В противном случае ток Iвыб протекает через эмиттер транзистора 1, сохраняя логическое состояние элемента памяти. Таким образом, существенно уменьшается время насыщенной работы транзистора 8.

В режиме записи "1" на вход-выход 15 подается потенциал записи "1", величина которого определяется соотношением

Uзп(1) > Uк(1), тогда ток Iвыб коммутируется в транзистор 9, устанавливая на коллекторе этого транзистора потенциал Uк(о), что соответствует единичному состоянию триггера элемента памяти. Таким образом, вход-выход 15 является универсальным одношинным портом записи считывания. Универсальность элемента памяти достигается тем, что каждый порт позволяет проводить как запись, так и считывание информации, используя только одну шину управления портом.

Технико-экономическая эффективность использования заявляемого элемента памяти подтверждается его моделированием на ЭВМ, которое показало значительное повышение быстродействия (время записи уменьшилось примерно в 5 раз) при улучшении помехоустойчивости и уменьшении числа управляющих шин, а также моделированием на его основе электрической схемы восьмипортового ОЗУ статического типа и моделированием ее на ЭВМ, которое показало, что количество управляющих шин в заявляемом элементе памяти меньше и соответственно уменьшается число формирователей по строкам или столбцам накопителя, площадь элемента памяти сокращается на 15% . (56) Валиев К. А. , Орликовский А. А. Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах. М. : Советское радио, с. 95, рис. 4.12а.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти | 1989 |

|

SU1679552A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Устройство для выборки элементов памяти в накопителе | 1980 |

|

SU930385A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1809466A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Формирователь импульсов выборки элементов памяти | 1978 |

|

SU723681A1 |

Использование: в вычислительной технике, в частности в схемах многопортовой оперативной и сверхоперативной биполярной памяти в интегральном исполнении. Сущность изобретения: элемент памяти содержит транзисторы 1,2,8,9,10, резисторы 3,4,7, диоды 5,8. 3 ил.

ЭЛЕМЕНТ ПАМЯТИ, содержащий первый и второй запоминающие n - p - n-транзисторы, эмиттеры которых объединены, а коллекторы соединены с первыми выводами первого и второго нагрузочных резисторов, подключенными к базам соответственно второго и первого запоминающих n - p - n-транзисторов, вторые выводы нагрузочных резисторов подключены к первой шине питания, первый и второй n - p - n-транзисторы связи и n - p - n-транзистор выборки, база и эмиттер которого являются соответственно первым и вторым входами сигналов выборки элемента, а коллектор подключен к эмиттерам первого и второго n - p - n-транзисторов связи, база первого n - p - n-транзистора связи соединена с коллектором первого запоминающего n - p - n-транзистора, а коллектор первого n - p - n-транзистора связи является информационным входом-выходом элемента, отличающийся тем, что, с целью повышения быстродействия и помехоустойчивости и упрощения элемента, он содержит фиксирующие диоды, коллектор второго n - p - n-транзистора связи подключен к базе первого запоминающего n - p - n-транзистора, который содержит дополнительный эмиттер, подключенный к коллектору n - p - n-транзистора выборки, база второго n - p - n-транзистора связи подключена к информационному входу-выходу элемента, аноды фиксирующих диодов соединены с первой шиной питания, а катоды - с базами соответственно второго и первого запоминающих n - p - n-транзисторов, и третий нагрузочный резистор, выводы которого соединены соответственно с эмиттером второго запоминающего n - p - n-транзистора и второй шиной питания.

Авторы

Даты

1994-01-30—Публикация

1991-03-13—Подача