Изобретение относится к вычислительной технике и может быть использовано при построении средств автоматики, функциональных узлов систем управления и др.

Известны параллельные счетчики единиц (см., например, рис. 9.6а на стр. 215 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), которые определяют количество единиц в трехразрядном двоичном числе, задаваемом тремя входными двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных параллельных счетчиков единиц, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка семиразрядного двоичного числа, задаваемого семью входными двоичными сигналами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип параллельный счетчик единиц (рис. 9.6б на стр. 215 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), который содержит логические элементы и определяет количество единиц в трехразрядном двоичном числе, задаваемом тремя входными двоичными сигналами. При этом глубину схемы прототипа образуют три логических элемента.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка семиразрядного двоичного числа, задаваемого семью входными двоичными сигналами.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения определения количества единиц в семиразрядном двоичном числе, задаваемом семью входными двоичными сигналами, при сохранении глубины схемы прототипа.

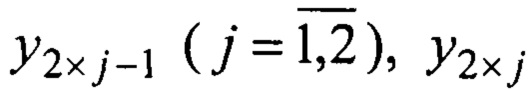

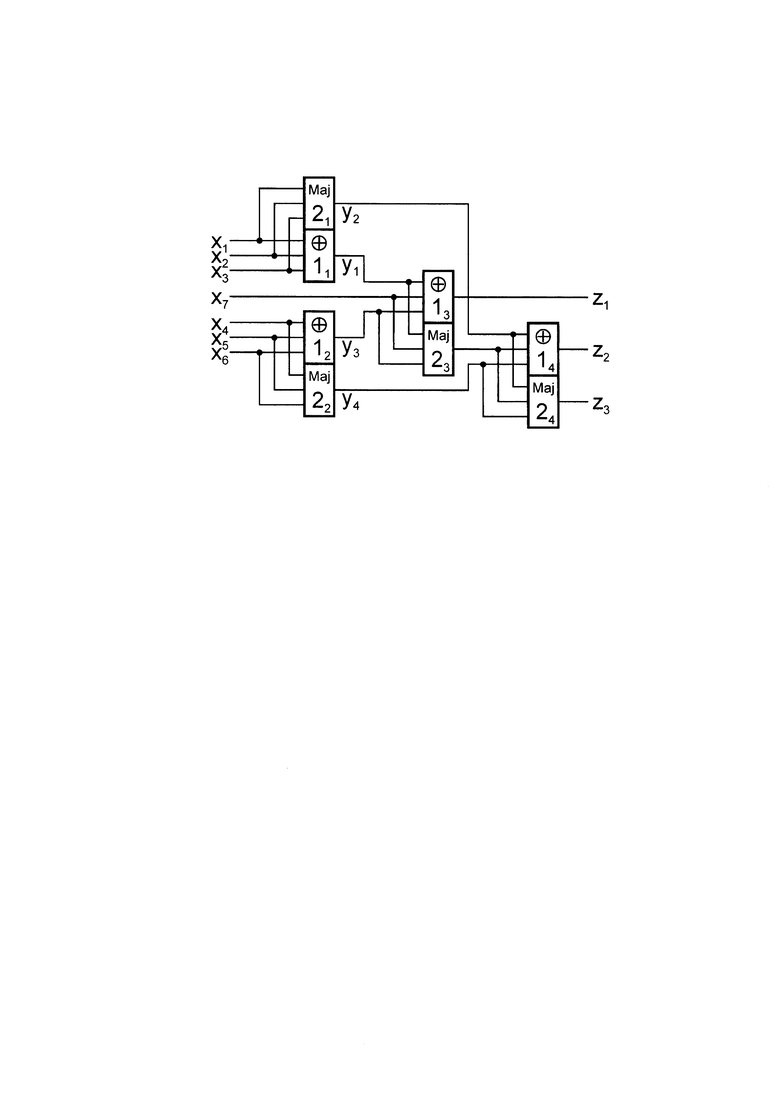

Указанный технический результат при осуществлении изобретения достигается тем, что в параллельном счетчике единиц, содержащем два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, особенность заключается в том, что в него дополнительно введены два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре мажоритарных элемента, причем первый, второй, третий входы i-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым, третьим входами i-го мажоритарного элемента, первый, третий входы третьего и первый, второй, третий входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, третьего, второго мажоритарных элементов, а первый, второй, третий входы j-го

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым, третьим входами i-го мажоритарного элемента, первый, третий входы третьего и первый, второй, третий входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, третьего, второго мажоритарных элементов, а первый, второй, третий входы j-го  второй вход третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход четвертого мажоритарного элемента соединены соответственно с (3 × j-2)-ым, (3 × j-1)-ым, (3 × j)-ым, седьмым входами и третьим выходом параллельного счетчика единиц, первый и второй выходы которого образованы соответственно выходами третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

второй вход третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход четвертого мажоритарного элемента соединены соответственно с (3 × j-2)-ым, (3 × j-1)-ым, (3 × j)-ым, седьмым входами и третьим выходом параллельного счетчика единиц, первый и второй выходы которого образованы соответственно выходами третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

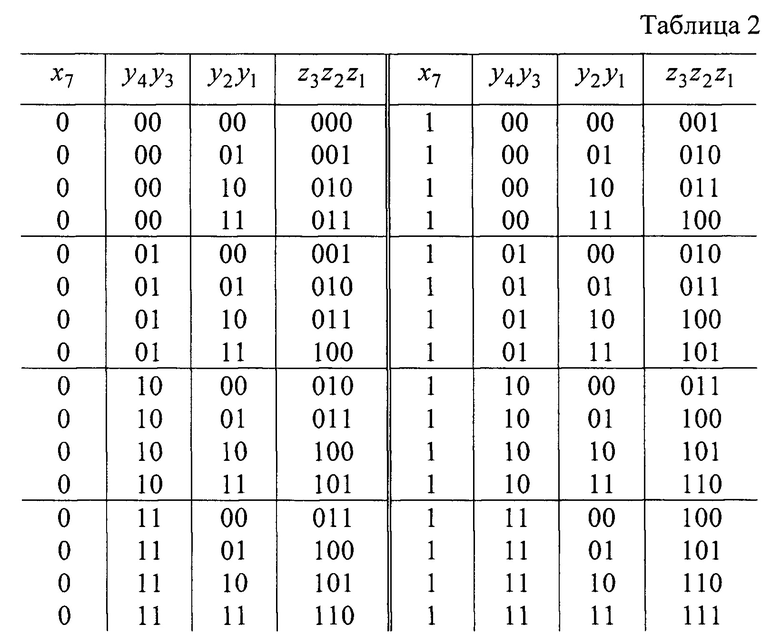

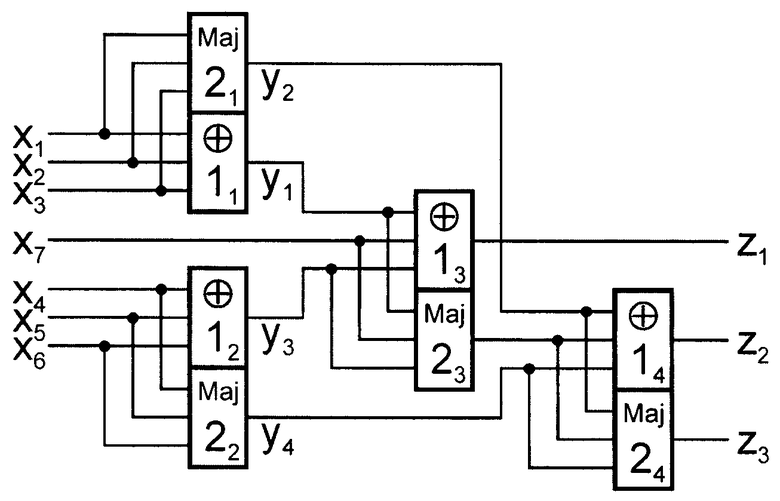

На чертеже представлена схема предлагаемого параллельного счетчика единиц.

Параллельный счетчик единиц содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, …, 14 и мажоритарные элементы 21, …,24, причем первый, второй, третий входы элемента  соединены соответственно с первым, вторым, третьим входами элемента 2i, первый, третий входы элемента 13 и первый, второй, третий входы элемента 14 соединены соответственно с выходами элементов 11, 12 и 21, 23, 22, а первый, второй, третий входы элемента

соединены соответственно с первым, вторым, третьим входами элемента 2i, первый, третий входы элемента 13 и первый, второй, третий входы элемента 14 соединены соответственно с выходами элементов 11, 12 и 21, 23, 22, а первый, второй, третий входы элемента

второй вход элемента 13 и выходы элементов 13, 14, 24 соединены соответственно с (3 × j-2)-ым, (3 × j-1)-ым, (3 × j)-ым, седьмым входами и первым, вторым, третьим выходами параллельного счетчика единиц.

второй вход элемента 13 и выходы элементов 13, 14, 24 соединены соответственно с (3 × j-2)-ым, (3 × j-1)-ым, (3 × j)-ым, седьмым входами и первым, вторым, третьим выходами параллельного счетчика единиц.

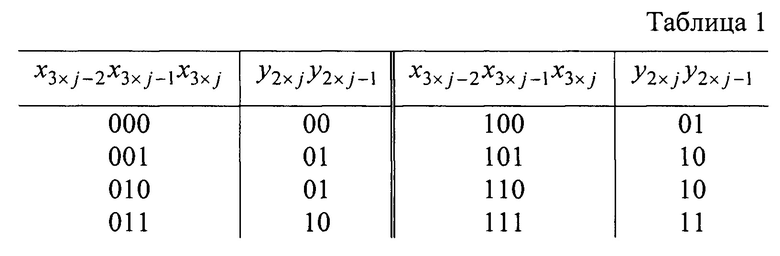

Работа предлагаемого параллельного счетчика единиц осуществляется следующим образом. На его первый,..., седьмой входы подаются соответственно двоичные сигналы х1, …,х7 ∈{0,l}, которые задают подлежащее обработке семиразрядное двоичное число. В представленной ниже табл. 1 приведены значения сигналов  , полученные с учетом работы элементов 1j, 2j для всех возможных наборов значений входных сигналов x3×j-2, x3×j-1, x3×j. В табл. 2 указаны значения выходных сигналов z1, z2, z3 предлагаемого счетчика, полученные с учетом работы соответствующих элементов для всех возможных наборов значений сигналов у1, у2, уз, у4, х7.

, полученные с учетом работы элементов 1j, 2j для всех возможных наборов значений входных сигналов x3×j-2, x3×j-1, x3×j. В табл. 2 указаны значения выходных сигналов z1, z2, z3 предлагаемого счетчика, полученные с учетом работы соответствующих элементов для всех возможных наборов значений сигналов у1, у2, уз, у4, х7.

Согласно табл. 1, табл. 2 имеем z1=β0, z2=β1, z3=β2, где β2β1β0 есть двоичный код количества единиц в семиразрядном двоичном числе, задаваемом двоичными сигналами х1, …, х7.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый параллельный счетчик единиц обладает более широкими по сравнению с прототипом функциональными возможностями, так как определяет количество единиц в семиразрядном двоичном числе, задаваемом семью входными двоичными сигналами. При этом глубину схемы предлагаемого параллельного счетчика единиц образуют три логических элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЦ | 2020 |

|

RU2760252C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2019 |

|

RU2710872C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2021 |

|

RU2776920C1 |

| ДВОИЧНЫЙ СУММАТОР | 2020 |

|

RU2758184C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2019 |

|

RU2747107C1 |

| ВЫЧИТАТЕЛЬ ПО МОДУЛЮ q | 2021 |

|

RU2770798C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789731C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2758186C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2775573C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в расширении функциональных возможностей параллельного счетчика единиц при сохранении глубины схемы прототипа. Параллельный счетчик единиц содержит четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (11, …, 14) и четыре мажоритарных элемента (21, …, 24). За счет указанных элементов и новой схемы их соединения, глубина которой равна 3, обеспечивается определение количества единиц в семиразрядном двоичном числе, задаваемом семью входными двоичными сигналами. 1 ил.

Параллельный счетчик единиц, содержащий два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающийся тем, что в него дополнительно введены два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре мажоритарных элемента, причем первый, второй, третий входы i-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым, третьим входами i-го мажоритарного элемента, первый, третий входы третьего и первый, второй, третий входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, третьего, второго мажоритарных элементов, а первый, второй, третий входы j-го

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым, третьим входами i-го мажоритарного элемента, первый, третий входы третьего и первый, второй, третий входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, третьего, второго мажоритарных элементов, а первый, второй, третий входы j-го  второй вход третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход четвертого мажоритарного элемента соединены соответственно с (3 × j-2)-ым, (3 × j-1)-ым, (3 × j)-ым, седьмым входами и третьим выходом параллельного счетчика единиц, первый и второй выходы которого образованы соответственно выходами третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

второй вход третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход четвертого мажоритарного элемента соединены соответственно с (3 × j-2)-ым, (3 × j-1)-ым, (3 × j)-ым, седьмым входами и третьим выходом параллельного счетчика единиц, первый и второй выходы которого образованы соответственно выходами третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2013 |

|

RU2518641C1 |

Авторы

Даты

2021-12-03—Публикация

2020-09-24—Подача