Изобретение относится к области вычислительной техники и может быть применено в специализированных вычислителях систем цифровой обработки сигналов.

Применение микропроцессорной техники требует особого алгоритмического и программного обеспечения, с помощью которого осуществляется вычисление часто используемых нетривиальных функций, которые, как правило, осуществляются неаналитическими методами. К числу таких функций относится модуль комплексного числа, вычисление которого, как правило, в калькуляторах выполняется с использованием алгоритма Волдера, Этот алгоритм подробно описан в литературе (Цифровые радионавигационные устройства / В.В. Барашенков, А.Е. Лутченко, Е.М. Скороходов и др.; Под ред. В.Б. Смолова. М.: Сов. радио, 1980, 288 с., ил. - С.164 - 166; И.Н. Булатникова, Н.Н. Гершунина. Неаналитические методы вычислений для микропроцессоров. Журнал Фундаментальные исследования 2015. №7 - С. 526-529).

Известны устройства для вычисления модуля комплексного числа (Устройство для вычисления модуля комплексного числа: пат. №2562411 Рос. Федерация: МПК G06F 7/38 / Н.С. Анишин, И.Н. Булатникова и Н.Н. Гершунина; заявл. 10.12.2014; опубл. 10.09.2015 Бюл. №25. Устройство для вычисления модуля комплексного числа: пат. №2618188 Рос.Федерация: МПК G06F 7/38 / Н.Н. Гершунина и И.Н. Булатникова; заявл. 25.02.2016; опубл. 02.05.2017 Бюл. №13).

Недостатком этих устройств является невысокая точность или большое время вычисления, т.к. в основе алгоритма Волдера заложен итерационный метод последовательного приближения.

Наиболее близким по технической сущности является устройство для вычисления модуля комплексного числа (А.с. №1295387 СССР: МПК G06F 7/552 / A.M. Плигин и М.В. Шкадин; заявл. 04.10.1985; опубл. 07.03.1987 Бюл. №9).

Это устройство содержит первый и второй блоки памяти квадрата аргумента, сумматор, на который поступают сигналы с выходов первого и второго блоков памяти, и третий блок памяти радикала аргумента.

В этом устройстве модуль комплексного числа вычисляется вдоль аналитического выражения реализуемой функции с использованием постоянных запоминающих устройств (ПЗУ), в которых хранятся значения функций, а аргументом являются адреса определенных ячеек памяти. Таким образом, при обращении к определенному адресу мгновенно извлекается значение функции, которое хранится в ячейке памяти по данному адресу.

В данном случае модуль комплексного числа можно рассматривать как вектор на плоскости, абсолютное значение которого не зависит от его направления. Если это значение определяется N разрядами, то и каждая из его проекций не превышает N разрядов. Возведение аргументов в квадрат вдвое увеличивает разрядную сетку, тогда количество двоичных ячеек памяти в ПЗУ определяется произведением (2N-1)⋅2N. При этом сумма квадратов аргументов не увеличивает разрядную сетку, что следует из независимости модуля вектора от его направления. Поэтому значение корня квадратного из суммы квадратов определяется уже 2N разрядами, при этом количество двоичных ячеек памяти в ПЗУ определяется произведением (22N-1)⋅N.

Недостатком этого устройства является избыточное количество ячеек памяти, в которых хранятся значения функции радикала аргумента.

Целью изобретения является сокращение числа ячеек памяти за счет перераспределения разрядов из адресной колонки блока памяти радикала аргумента в строку данных.

Указанный технический результат достигается тем, что в устройство для вычисления модуля комплексного числа, содержащее первый и второй блоки памяти квадрата аргумента, сумматор, на который поступают сигналы с выходов первого и второго блоков памяти, и третий блок памяти радикала аргумента, дополнительно введены логический блок управления, коммутатор сдвига в сторону младших разрядов и коммутатор сдвига в сторону старших разрядов, при этом выход сумматора соединен с коммутатором сдвига в сторону младших разрядов и логическим блоком управления, выход которого соединен с управляющими входами коммутаторов сдвига в сторону младших разрядов и в сторону старших разрядов, выход коммутатора сдвига в сторону младших разрядов через третий блок памяти радикала аргумента соединен с входом коммутатора сдвига в сторону старших разрядов, выход которого является выходом устройства.

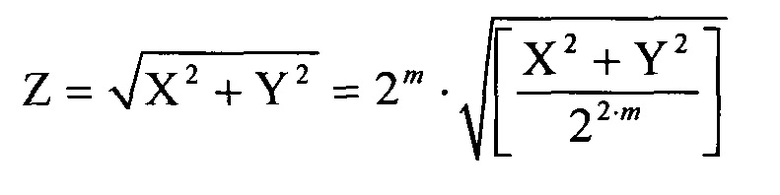

Поясним суть изобретения.

Известно, что количество двоичных ячеек памяти в большей степени определяется разрядами адресной колонки, чем разрядами в строке данных, поэтому их необходимо перераспределить. Для этого можно модифицировать выражение вычисления модуля комплексного числа.

В этом выражении значение под корнем в квадратных скобках означает 2m целую часть, которое предварительно поделили на 2m, что равносильно сдвигу на 2m разрядов в сторону младших. Результат корня квадратного из целой части извлекается с точностью m разрядов после запятой и умножается на 2m, что равносильно сдвигу на m разрядов в сторону старших. При этом параметр m изменяется от 0 до N/2, код которого зависит от превышения разрядной сетки на выходе сумматора выше N-го разряда, а количество двоичных ячеек памяти в этом случае для корня квадратного определяется произведением (2N-1)⋅3N/2. Таким образом, в предложенном варианте по сравнению с прототипом, при вычислении корня квадратного, количество двоичных ячеек памяти требуется в 2⋅(2N+1)/3 раза меньше, при этом ошибка вычисления не превышает цену младшего разряда.

Охарактеризованное указанным выше существенным признаком изобретение на дату подачи заявки не известно в Российской Федерации и за границей и отвечает требованиям критерия "новизна".

Заявителями не выявлены технические решения, имеющие признак, совпадающий с отличительным признаком заявляемого изобретения, обеспечивающий достижение заявляемого технического результата, в связи с чем, можно сделать вывод о соответствии изобретения условию патентоспособности "изобретательский уровень".

Изобретение может быть реализовано промышленным способом с использованием известных технических средств, технологий и материалов и соответствует требованиям условия патентоспособности "промышленная применимость".

Изобретение поясняются графическими материалами.

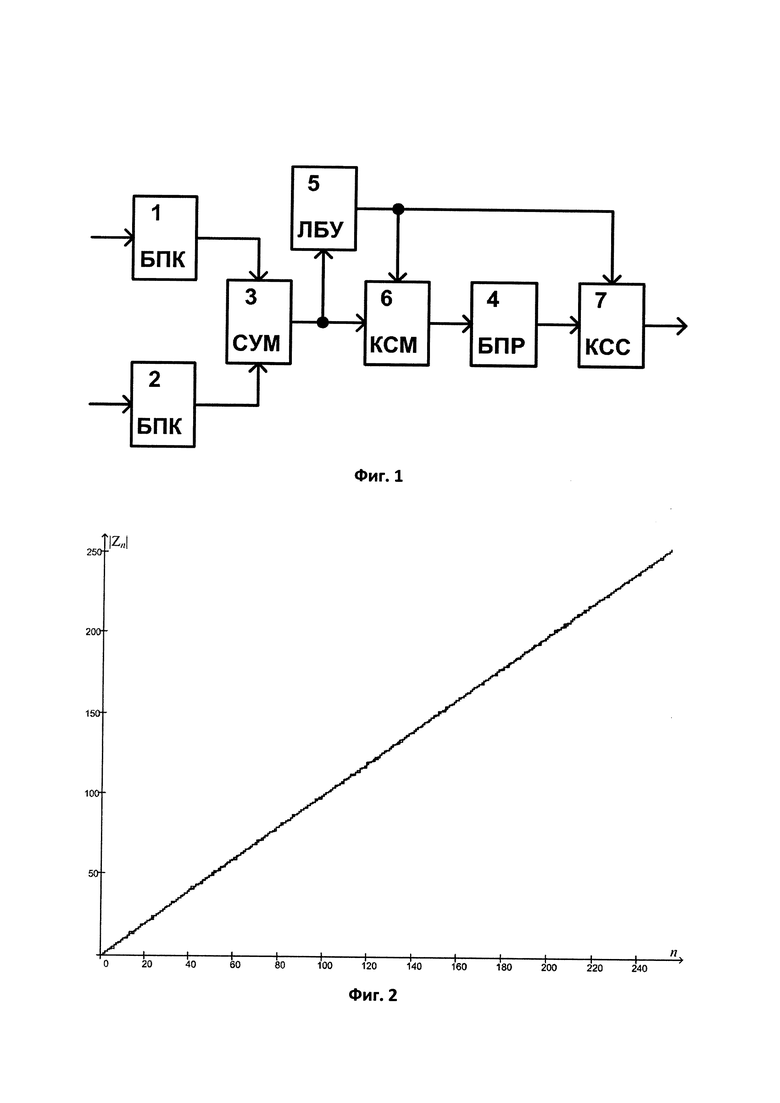

На фиг. 1 изображена структурная схема устройства для вычисления модуля комплексного числа. Заявленное устройство содержит первый 1 и второй 2 блоки памяти квадрата (БПК) аргумента, сумматор (СУМ) 3, третий блок памяти радикала (БПР) аргумента 4, логический блок управления (ЛБУ) 5, коммутатор сдвига в сторону младших разрядов (КСМ) 6, коммутатор сдвига в сторону старших разрядов (КСС) 7.

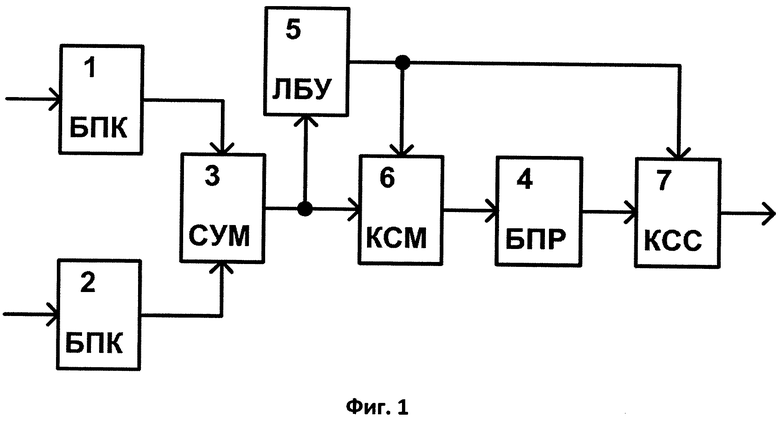

На фиг. 2 представлен результат вычисления модуля с фиксацией максимального и минимального значений. С учетом сокращения числа разрядов в адресной колонке и увеличения их в строке данных выполнялось моделирование вычисления модуля комплексного числа. При этом для каждого значения длины вектора входные сигналы (проекции вектора) задавались целыми числами для разных направлений вектора с шагом 2° и фиксировались максимальное и минимальное значения модуля, выраженные тоже целыми числами. Точность вычисления модуля комплексного числа представлена графически, где на оси абсцисс отложены идеальные значения модуля, а на оси ординат - вычисленные максимальные и минимальные значения модуля, отклонение которых от идеального значения не превышает цену деления младшего разряда.

Устройство работает следующим образом.

N разрядные коды значений действительной и мнимой частей комплексного числа поступают на адресные входы БПК аргумента 1 и 2. В СУМ 3 квадраты входных значений суммируются и с его выхода 2-N разрядов поступают на вход КСМ 6, а старшая половина разрядов N+1…2 N поступает также на вход ЛБУ 5. В зависимости от значащих разрядов N+1…2 N в ЛБУ формируется код. При этом если во всех разрядах нули, то и код управления равен нулю, а если хотя бы один разряд N+1 или N+2 отличен от нуля, но старшие равны нулю, то код равен единице. Также, если разряд N+3 или N+4 отличен от нуля, но старшие равны нулю, то код равен двум и т.д. Сформированный таким образом код m поступает на управляющие входы КСМ 6 и КСС 7. В КСМ 6 осуществляется сдвиг в сторону младших разрядов на 2 m позиции, а в КСС 7 в сторону старших разрядов на m позиций. При этом с выхода КСМ 6 поступает N разрядный код на адресный вход БПР 4, в котором по данному адресу извлекается значение корня квадратного с точностью m знаков после запятой, которое в двоичном коде содержит 3N/2 разряда. Таким образом, на выходах КСМ 6 и КСС 7, а также адресном входе БПР 4 число значащих разрядов не более N.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU957209A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Генератор функций Шаудера | 1987 |

|

SU1513433A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003081A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА | 2014 |

|

RU2562411C1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1295387A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислителях систем цифровой обработки сигналов. Техническим результатом является сокращение числа ячеек памяти за счет перераспределения разрядов из адресной колонки блока памяти радикала аргумента в строку данных. Устройство содержит первый и второй блоки памяти квадрата аргумента, сумматор, блок памяти радикала аргумента, логический блок управления, коммутатор сдвига в сторону младших разрядов и коммутатор сдвига в сторону старших разрядов. 2 ил.

Устройство для вычисления модуля комплексного числа, содержащее первый и второй блоки памяти квадрата аргумента, сумматор, на который поступают сигналы с выходов первого и второго блоков памяти, и третий блок памяти радикала аргумента, отличающееся тем, что в его состав введены логический блок управления, коммутатор сдвига в сторону младших разрядов и коммутатор сдвига в сторону старших разрядов, при этом выход сумматора соединен с коммутатором сдвига в сторону младших разрядов и логическим блоком управления, выход которого соединен с управляющими входами коммутаторов сдвига в сторону младших разрядов и в сторону старших разрядов, выход коммутатора сдвига в сторону младших разрядов через третий блок памяти радикала аргумента соединен с входом коммутатора сдвига в сторону старших разрядов, выход которого является выходом устройства.

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1295387A1 |

| Устройство для вычисления модуля комплексного числа | 2016 |

|

RU2618188C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА | 2014 |

|

RU2562411C1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| JP 9097299 A, 08.04.1997 | |||

| US 6999981 B2, 14.02.2006. | |||

Авторы

Даты

2022-03-16—Публикация

2021-04-13—Подача