Изобретение относится к области радиотехники и связи и может быть использовано в качестве элемента усиления и преобразования аналоговых сигналов, в структуре арсенид-галлиевых микросхем различного функционального назначения.

В микросхемах для систем связи, радиолокации и измерительной техники находят широкое применение различные модификации преобразователей «напряжение-ток» (ПНТ), которые реализуются на практике в виде классических [1-4] или каскодных [5-10] дифференциальных каскадов разных модификаций и на разных технологических процессах.

Особую актуальность имеют схемотехнические решения для GaAs технологии [11, 12]. Сегодня GaAs полевые транзисторы незаменимы в СВЧ дифференциальных каскадах и усилителях как общего, так и специального назначения, где особую роль играют малый уровень шумов и надежность.

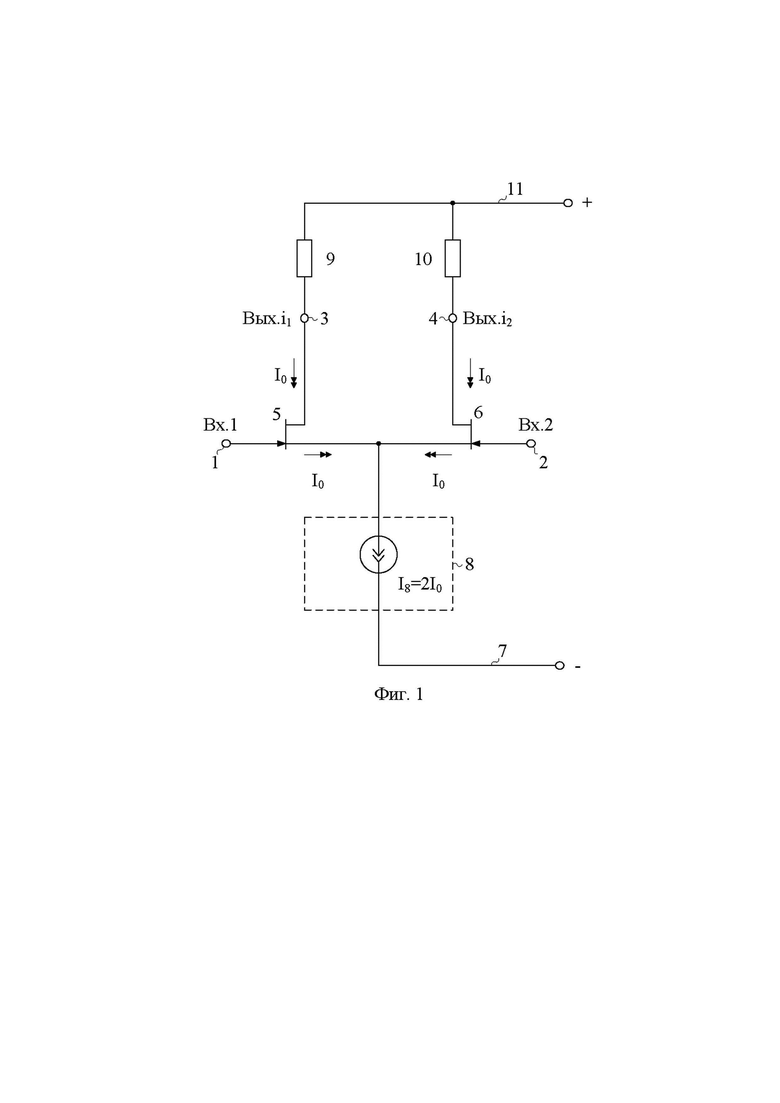

Ближайшим прототипом (фиг. 1) заявляемого устройства является схема дифференциального преобразователя «напряжение-ток» на основе дифференциального каскада по патенту US 5.291.149, fig.4, 1994 г., который также присутствует в патентах RU 284473, fig. 1, 2020 г. и US 3.873.933, fig. 2, 1975 г.. Известный ПНТ содержит первый 1 и второй 2 входы, а также первый 3 и второй 4 токовые выходы, первый 5 и второй 6 входные полевые транзисторы, объединенные истоки которых связаны с первой 7 шиной источника питания через первый 8 источник опорного тока, первый 9 и второй 10 вспомогательные резисторы, причем первый 3 и второй 4 токовые выходы согласованы со второй 11 шиной источника питания, затвор первого 5 входного полевого транзистора соединен с первым 1 входом устройства, затвор второго 6 входного полевого транзистора связан со вторым 2 входом устройства.

Существенный недостаток известного дифференциального преобразователя «напряжение-ток», архитектура которого представлена на чертеже фиг. 1, состоит в том, что при работе входных арсенид-галлиевых транзисторов 5 и 6 в режиме микротоков он имеет малое значения крутизны усиления, оказывающей существенное влияние на многие параметры аналоговых микросхем.

Основная задача предлагаемого изобретения состоит в увеличении крутизны усиления дифференциального преобразователя без существенного повышения общего статического токопотребления GaAs транзисторов.

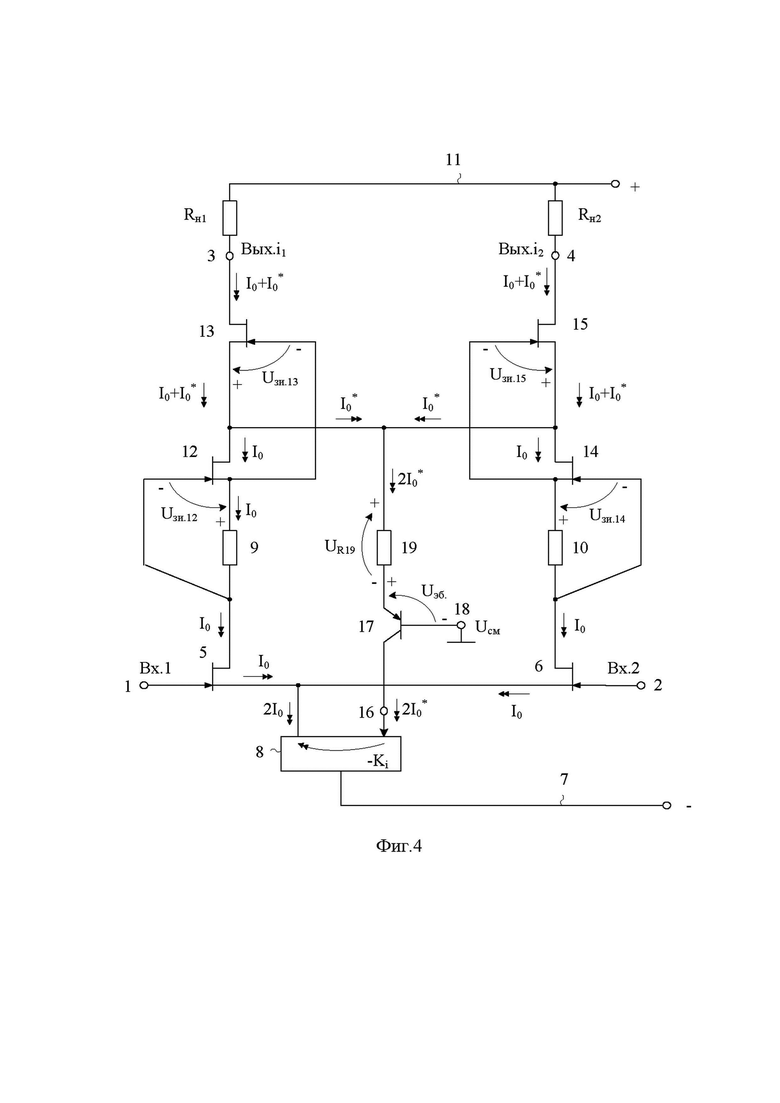

Поставленная задача решается тем, что в дифференциальном преобразователе «напряжение-ток» фиг. 1, содержащем первый 1 и второй 2 входы, а также первый 3 и второй 4 токовые выходы, первый 5 и второй 6 входные полевые транзисторы, объединенные истоки которых связаны с первой 7 шиной источника питания через первый 8 источник опорного тока, первый 9 и второй 10 вспомогательные резисторы, причем первый 3 и второй 4 токовые выходы согласованы со второй 11 шиной источника питания, затвор первого 5 входного полевого транзистора соединен с первым 1 входом устройства, затвор второго 6 входного полевого транзистора связан со вторым 2 входом устройства, предусмотрены новые элементы и связи - сток первого 5 входного полевого транзистора соединен с затвором первого 12 дополнительного полевого транзистора и связан с истоком первого 12 дополнительного полевого транзистора и затвором второго 13 дополнительного полевого транзистора через первый 9 вспомогательный резистор, сток второго 13 дополнительного полевого транзистора соединен с первым 3 токовым выходом устройства, исток второго 13 дополнительного полевого транзистора подключен к стоку первого 12 дополнительного полевого транзистора, сток второго 6 входного полевого транзистора соединен с затвором третьего 14 дополнительного полевого транзистора и связан с истоком третьего 14 дополнительного полевого транзистора и затвором четвертого 15 дополнительного полевого транзистора через второй 10 вспомогательный резистор, сток четвертого 15 дополнительного полевого транзистора подключен ко второму 4 токовому выходу устройства, а его исток связан со стоком третьего 14 дополнительного полевого транзистора, первый 8 источник опорного тока выполнен в виде управляемого по входу 16 инвертирующего источника опорного тока, истоки второго 13 и четвертого 15 дополнительных полевых транзисторов связаны с эмиттером дополнительного биполярного транзистора 17, база которого подключена к источнику напряжения смещения 18, а коллектор соединен с управляющим входом 16 источника опорного тока 8.

На чертеже фиг. 1 приведена схема дифференциального преобразователя - прототипа.

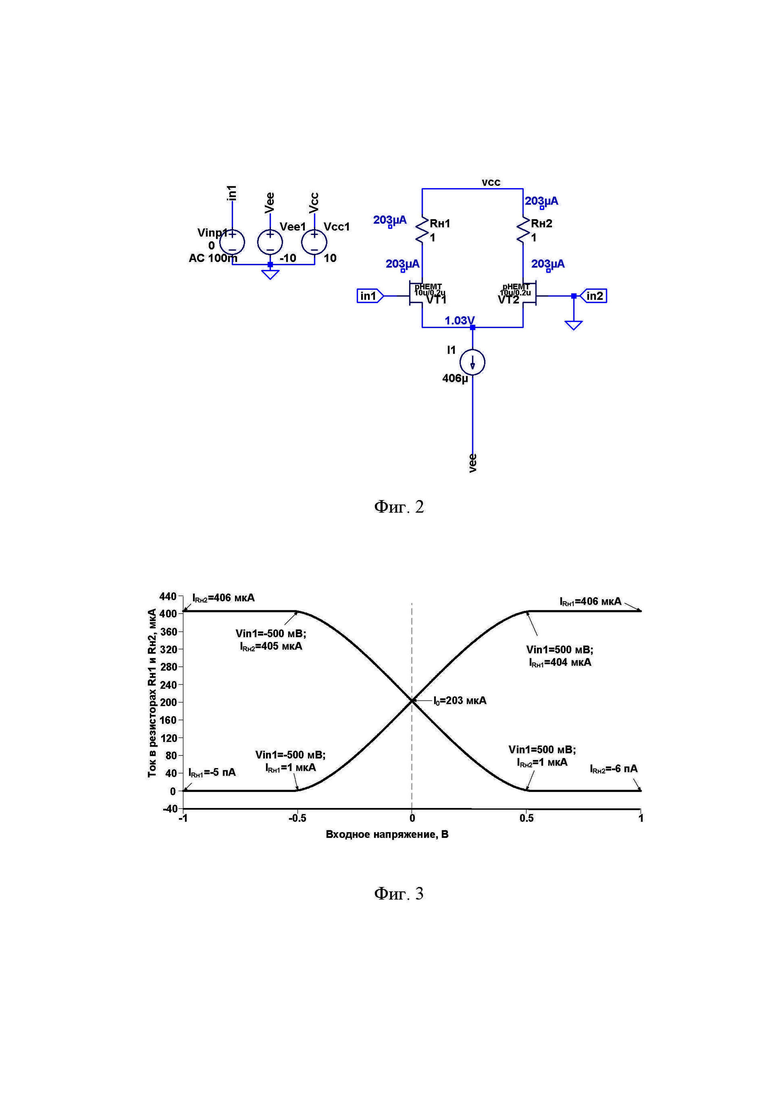

На чертеже фиг. 2 представлена схема дифференциального преобразователя - прототипа в среде LTspice на моделях арсенид-галлиевых транзисторов.

На чертеже фиг. 3 показаны проходные характеристики дифференциального преобразователя-прототипа фиг. 2.

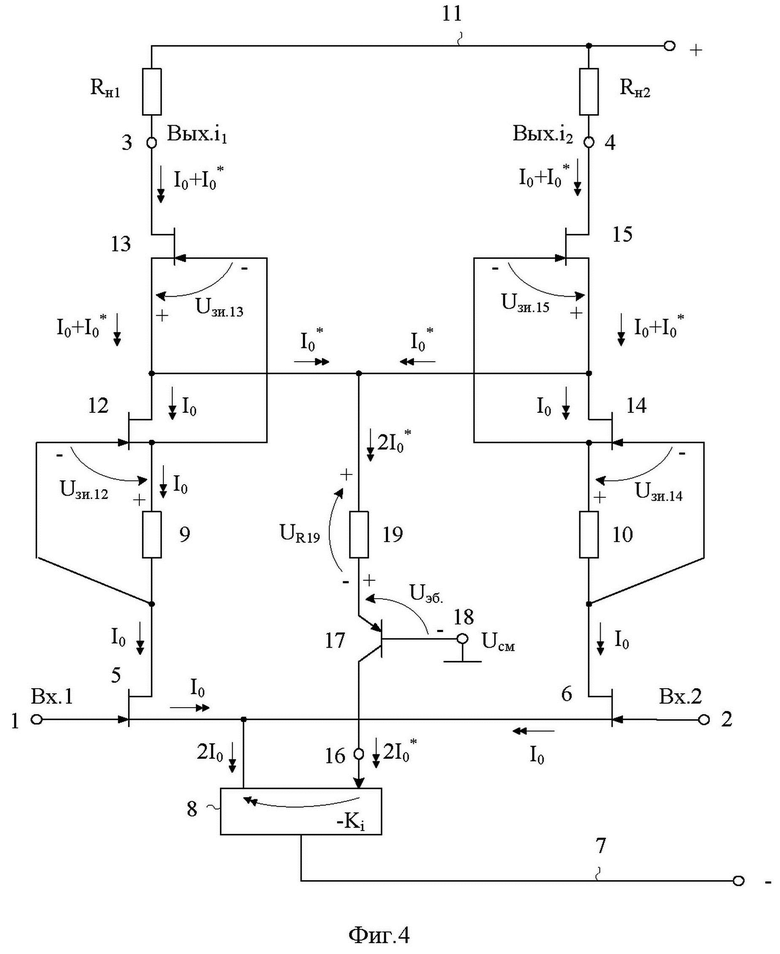

На чертеже фиг. 4 приведена схема заявляемого дифференциального преобразователя «напряжение-ток» в соответствии с п. 1 и п. 2 формулы изобретения.

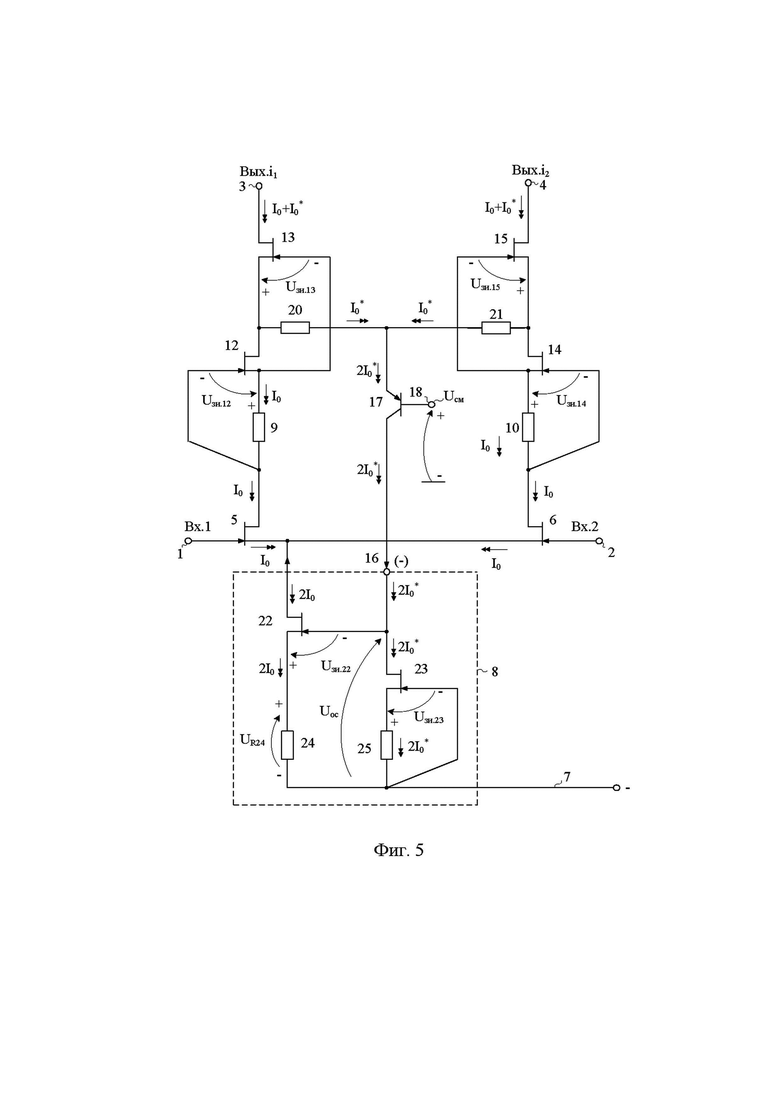

На чертеже фиг. 5 представлена схема заявляемого дифференциального преобразователя «напряжение-ток» в соответствии с п. 3 формулы изобретения.

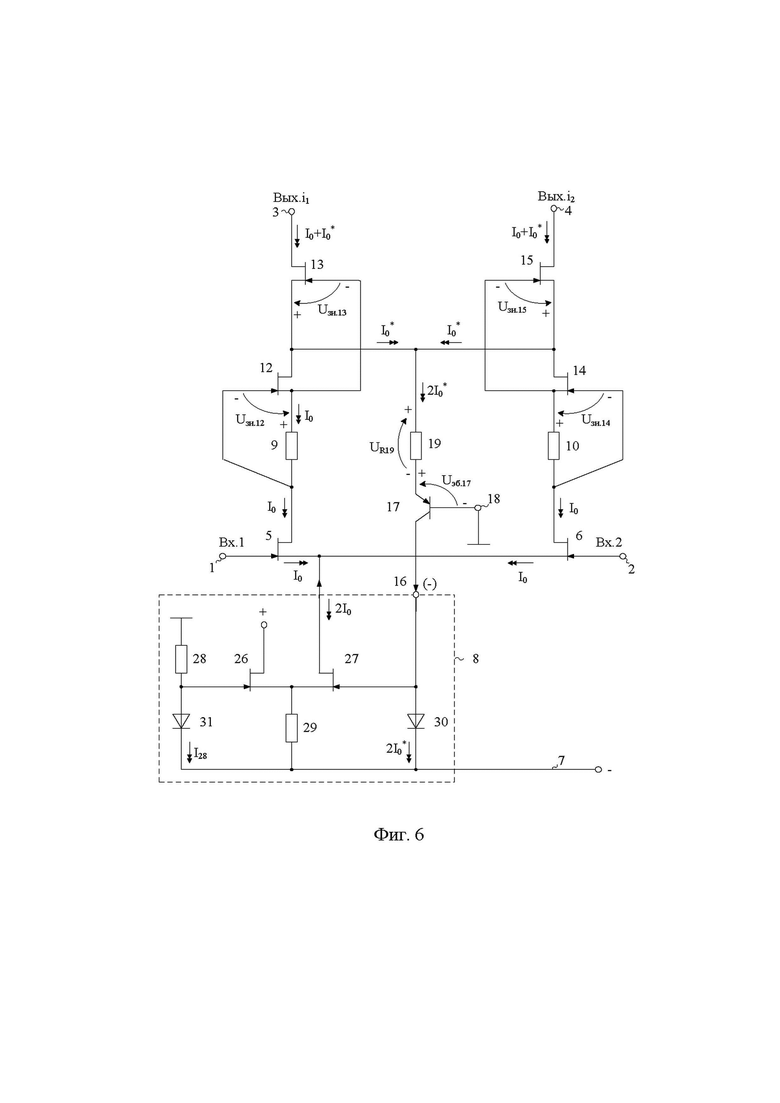

На чертеже фиг. 6 показана схема заявляемого дифференциального преобразователя «напряжение-ток» в соответствии с п. 2 формулы изобретения для случая, когда первый 8 источник опорного тока выполнен на основе дифференциального каскада на транзисторах 26, 27, резисторах 28, 29 и р-n переходах 30, 31.

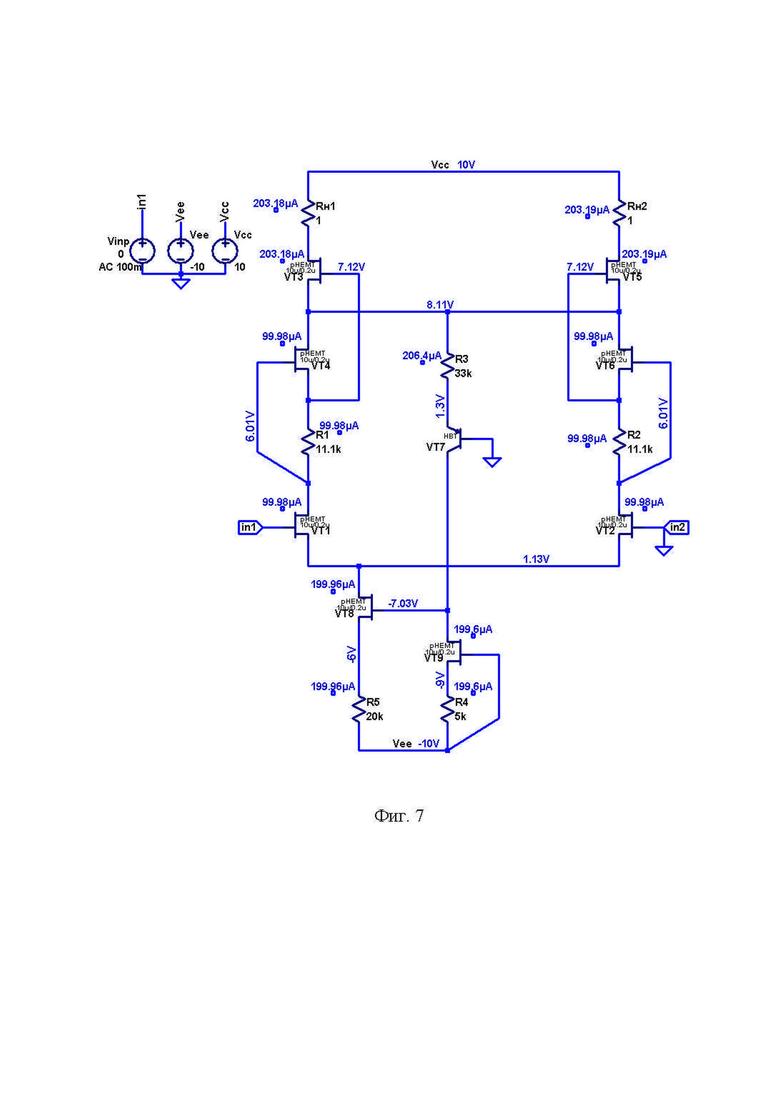

На чертеже фиг. 7 приведена схема заявляемого дифференциального преобразователя «напряжение-ток» фиг. 5 в среде моделирования LTspice.

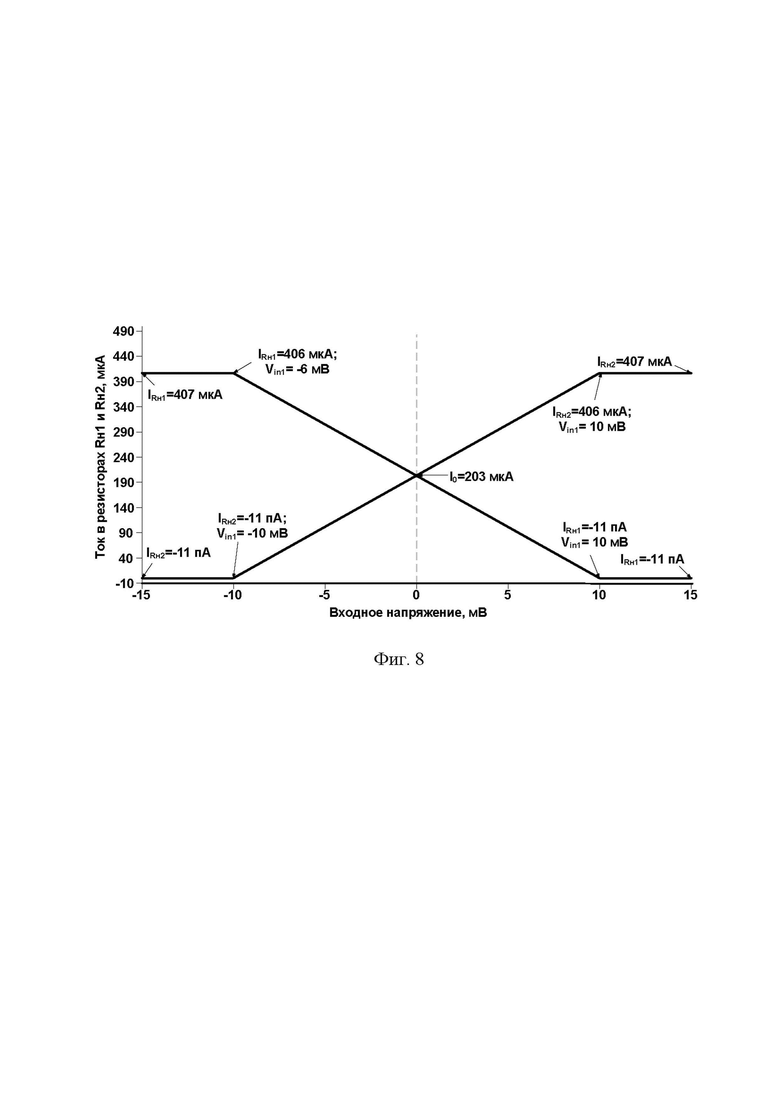

На чертеже фиг. 8 представлены проходные характеристики дифференциального преобразователя «напряжение-ток» фиг. 7.

Моделирование, представленное на чертежах фиг. 3, фиг. 7, фиг. 8, проводилось на моделях РНЕМТ полевых и pnp биполярных транзисторов (НТВ), изготовленных в Минском научно-исследовательском институте радиоматериалов (г. Минск).

Арсенид-галлиевый дифференциальный преобразователь «напряжение-ток» фиг. 2 содержит первый 1 и второй 2 входы, а так же первый 3 и второй 4 токовые выходы, первый 5 и второй 6 входные полевые транзисторы, объединенные истоки которых связаны с первой 7 шиной источника питания через первый 8 источник опорного тока, первый 9 и второй 10 вспомогательные резисторы, причем первый 3 и второй 4 токовые выходы согласованы со второй 11 шиной источника питания, затвор первого 5 входного полевого транзистора соединен с первым 1 входом устройства, затвор второго 6 входного полевого транзистора связан со вторым 2 входом устройства. Сток первого 5 входного полевого транзистора соединен с затвором первого 12 дополнительного полевого транзистора и связан с истоком первого 12 дополнительного полевого транзистора и затвором второго 13 дополнительного полевого транзистора через первый 9 вспомогательный резистор, сток второго 13 дополнительного полевого транзистора соединен с первым 3 токовым выходом устройства, исток второго 13 дополнительного полевого транзистора подключен к стоку первого 12 дополнительного полевого транзистора, сток второго 6 входного полевого транзистора соединен с затвором третьего 14 дополнительного полевого транзистора и связан с истоком третьего 14 дополнительного полевого транзистора и затвором четвертого 15 дополнительного полевого транзистора через второй 10 вспомогательный резистор, сток четвертого 15 дополнительного полевого транзистора подключен ко второму 4 токовому выходу устройства, а его исток связан со стоком третьего 14 дополнительного полевого транзистора, первый 8 источник опорного тока выполнен в виде управляемого по входу 16 инвертирующего источника опорного тока, истоки второго 13 и четвертого 15 дополнительных полевых транзисторов связаны с эмиттером дополнительного биполярного транзистора 17, база которого подключена к источнику напряжения смещения 18, а коллектор соединен с управляющим входом 16 источника опорного тока 8.

На чертеже фиг. 4, в соответствии с п. 2 формулы изобретения, истоки второго 13 и четвертого 15 дополнительных полевых транзисторов связаны с эмиттером дополнительного биполярного транзистора 17 через вспомогательный резистор 19.

На чертеже фиг. 5, в соответствии с п. 3 формулы изобретения, исток второго 13 дополнительного полевого транзистора связан с эмиттером дополнительного биполярного транзистора 17 через третий 20 дополнительный резистор, а исток четвертого 15 дополнительного полевого транзистора связан с эмиттером дополнительного биполярного транзистора 17 через четвертый 21 дополнительный резистор.

В схеме фиг. 4 резисторы Rн1 и Rн2 моделируют свойства нагрузки, которая подключается к токовым выходам 3 и 4.

В частном случае на чертеже фиг. 5 первый 8 управляемый источник опорного тока выполнен на полевых транзисторах 22, 23 и содержит резисторы 24 и 25.

На чертеже фиг. 6 первый 8 источник опорного тока выполнен на основе дифференциального каскада на транзисторах 26, 27, резисторах 28, 29 и р-n переходах 30, 31.

Рассмотрим работу заявляемого устройства фиг. 4.

Статический режим ПНТ фиг. 4 по напряжению на истоках второго 13 и четвертого 15 дополнительных полевых транзисторов определяется падением напряжения на вспомогательном резисторе 19, напряжением эмиттер-база дополнительного биполярного транзистора 17, а также источником напряжения смещения 18. При этом токи истоков первого 5 и второго 6 входных полевых транзисторов зависят от выбранных значений опорного тока I0*, который рекомендуется выбирать в диапазоне не более ддесятков микроампер, а также коэффициента передачи по току первого 8 управляемого источника опорного тока.

В схеме фиг. 4 стоки первого 5 и второго 6 входных полевых транзисторов являются высокоимпедансными узлами, что положительно сказывается на коэффициенте усиления по напряжению от первого 1 входа устройства на стоки первого 5 и второго 6 входных полевых транзисторов. Если на первый 1 вход подается положительное напряжение относительно второго 2 входа, то это вызывает уменьшение напряжения на стоке первого 5 входного полевого транзистора, которое передается в исток первого 12 дополнительного полевого транзистора и далее на затвор второго 13 дополнительного полевого транзистора. При этом напряжение на стоке второго 6 входного полевого транзистора, затворе третьего 14 дополнительного полевого транзистора, истоке третьего 14 дополнительного полевого транзистора, затворе четвертого 15 дополнительного полевого транзистора увеличивается. Таким образом, второй 13 и четвертый 15 дополнительные полевые транзисторы работают как дополнительный дифференциальный каскад усиления, что повышает общую эквивалентную крутизну ПНТ по первому 3 и второму 4 выходам. Данные выводы подтверждатся графиками фиг. 3 и фиг. 8. Так, в схеме ПНТ-прототипа фиг. 1 напряжение ограничения проходной характеристики превышает 500 мВ (фиг. 2). В заявляемом устройстве граничное напряжение ПНТ лежит в диапазоне 6-10 мВ при таких же выходных статическом токах (фиг. 8). Поэтому крутизна усиления схемы ПНТ фиг. 7 выше чем крутизна ПНТ-прототипа более чем в 50 раз, что положительно сказывается на параметрах арсенид-галлиевых микросхем с предлагаемым ПНТ.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ПНТ-прототипом по крутизне усиления.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.531.919, fig. 1, fig.4, 2003 г.

2. Патент US 5.083.046, 1992 г.

3. Патент US 5.367.271, 1994 г.

4. Патент US 5.648.743, fig. 23, 1997

5. Патент US 4.121.169, fig. 5, 1978 г.

6. Патент SU 437193, 1974 г.

7. Патент SU 1385225, 1988 г.

8. Патент US 5.210.505, fig. 4, 1993 г.

9. Патент US 9.167.327, 2015 г.

10. Патент US 9.888.315, 2018 г.

11. В. Bernhardt, М. LaMacchia, J. Abrokwah and others, «Complementary GaAs(CGaAs): a high performance BiCMOS alternative», GaAs IC Symposium IEEE Gallium Arsenide Integrated Circuit Symposium 17th Annual Technical Digest 1995, pp. 1-4, DOI: 10.1109/GAAS.1995.528953.

12. A. Bessemoulin, J. Dishong, G. Clark and others, «1 watt broad Ka-band ultra small high power amplifier MMICs using 0.25-/spl mu/m GaAs PHEMTs», 24th Annual Technical Digest Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, pp. 1-4, DOI: 10.1109/GAAS.2002.1049025.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| Арсенид-галлиевый дифференциальный каскад с умножителем крутизны усиления | 2022 |

|

RU2789756C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве элемента усиления и преобразования аналоговых сигналов, в структуре арсенид-галлиевых микросхем различного функционального назначения. Технический результат: увеличение крутизны усиления дифференциального преобразователя без существенного повышения общего статического токопотребления GaAs транзисторов. Арсенид-галлиевый дифференциальный преобразователь «напряжение-ток» содержит первый (1) и второй (2) входы, а также первый (3) и второй (4) токовые выходы, первый (5) и второй (6) входные полевые транзисторы, объединенные истоки которых связаны с первой (7) шиной источника питания через первый (8) источник опорного тока, первый (9) и второй (10) вспомогательные резисторы, причем первый (3) и второй (4) токовые выходы согласованы со второй (11) шиной источника питания, затвор первого (5) входного полевого транзистора соединен с первым (1) входом устройства, затвор второго (6) входного полевого транзистора связан со вторым (2) входом устройства. Сток первого (5) входного полевого транзистора соединен с затвором первого (12) дополнительного полевого транзистора и связан с истоком первого (12) дополнительного полевого транзистора и затвором второго (13) дополнительного полевого транзистора через первый (9) вспомогательный резистор, сток второго (13) дополнительного полевого транзистора соединен с первым (3) токовым выходом устройства, исток второго (13) дополнительного полевого транзистора подключен к стоку первого (12) дополнительного полевого транзистора, сток второго (6) входного полевого транзистора соединен с затвором третьего (14) дополнительного полевого транзистора и связан с истоком третьего (14) дополнительного полевого транзистора и затвором четвертого (15) дополнительного полевого транзистора через второй (10) вспомогательный резистор, сток четвертого (15) дополнительного полевого транзистора подключен ко второму (4) токовому выходу устройства, а его исток связан со стоком третьего (14) дополнительного полевого транзистора, первый (8) источник опорного тока выполнен в виде управляемого по входу (16) инвертирующего источника опорного тока, истоки второго (13) и четвертого (15) дополнительных полевых транзисторов связаны с эмиттером дополнительного биполярного транзистора (17), база которого подключена к источнику напряжения смещения (18), а коллектор соединен с управляющим входом (16) источника опорного тока (8). 2 з.п. ф-лы, 8 ил.

1. Арсенид-галлиевый дифференциальный преобразователь «напряжение-ток», содержащий первый (1) и второй (2) входы, а также первый (3) и второй (4) токовые выходы, первый (5) и второй (6) входные полевые транзисторы, объединенные истоки которых связаны с первой (7) шиной источника питания через первый (8) источник опорного тока, первый (9) и второй (10) вспомогательные резисторы, причем первый (3) и второй (4) токовые выходы согласованы со второй (11) шиной источника питания, затвор первого (5) входного полевого транзистора соединен с первым (1) входом устройства, затвор второго (6) входного полевого транзистора связан со вторым (2) входом устройства, отличающийся тем, что сток первого (5) входного полевого транзистора соединен с затвором первого (12) дополнительного полевого транзистора и связан с истоком первого (12) дополнительного полевого транзистора и затвором второго (13) дополнительного полевого транзистора через первый (9) вспомогательный резистор, сток второго (13) дополнительного полевого транзистора соединен с первым (3) токовым выходом устройства, исток второго (13) дополнительного полевого транзистора подключен к стоку первого (12) дополнительного полевого транзистора, сток второго (6) входного полевого транзистора соединен с затвором третьего (14) дополнительного полевого транзистора и связан с истоком третьего (14) дополнительного полевого транзистора и затвором четвертого (15) дополнительного полевого транзистора через второй (10) вспомогательный резистор, сток четвертого (15) дополнительного полевого транзистора подключен ко второму (4) токовому выходу устройства, а его исток связан со стоком третьего (14) дополнительного полевого транзистора, первый (8) источник опорного тока выполнен в виде управляемого по входу (16) инвертирующего источника опорного тока, истоки второго (13) и четвертого (15) дополнительных полевых транзисторов связаны с эмиттером дополнительного биполярного транзистора (17), база которого подключена к источнику напряжения смещения (18), а коллектор соединен с управляющим входом (16) источника опорного тока (8).

2. Арсенид-галлиевый дифференциальный преобразователь «напряжение-ток» по п. 1, отличающийся тем, что истоки второго (13) и четвертого (15) дополнительных полевых транзисторов связаны с эмиттером дополнительного биполярного транзистора (17) через вспомогательный резистор (19).

3. Арсенид-галлиевый дифференциальный преобразователь «напряжение-ток» по п. 1, отличающийся тем, что исток второго (13) дополнительного полевого транзистора связан с эмиттером дополнительного биполярного транзистора (17) через третий (20) дополнительный резистор, а исток четвертого (15) дополнительного полевого транзистора связан с эмиттером дополнительного биполярного транзистора (17) через четвертый (21) дополнительный резистор.

| ШИРОКОПОЛОСНЫЙ ПРЕОБРАЗОВАТЕЛЬ «НАПРЯЖЕНИЕ-ТОК» НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2739213C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388139C1 |

| US 6531919 B1, 11.03.2003 | |||

| US 5367271 A1, 22.11.1994 | |||

| US 9888315 B1, 06.02.2018. | |||

Авторы

Даты

2023-01-20—Публикация

2022-03-18—Подача