Изобретение относится к радиоэлектронике и может быть использовано в качестве операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1-2], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения ОУ, а также в драйверах быстродействующих аналого-цифровых преобразователей.

В современной радиоэлектронной аппаратуре находят применение быстродействующие операционные усилители с цепями так называемой нелинейной коррекции (НКЦ) переходных процессов в режиме большого сигнала [3-12]. При этом для уменьшения влияния НКЦ на параметры статического режима и ослабления входных синфазных сигналов многие из существующих НКЦ, например, по патенту US 6.831.515, 2004 г., имеют сравнительно большую зону нечувствительности (Uп) на проходной характеристике – зависимости выходных токов входного дифференциального каскада (ДК) от входного дифференциального напряжения ОУ, перезаряжающих интегрирующую емкость коррекции ОУ (Ск). В работах [8-12] показано, что такая зона нечувствительности (Uп) отрицательно влияет на время установления переходного процесса ОУ и максимальную скорость нарастания выходного напряжения (SR). Данный факт подтверждается также чертежом фиг. 2, представленном в описании серийной микросхемы США LM6142/44 [7], использующей патент US 6.831.515, 2004 г.

Таким образом, в рассматриваемом классе известных ОУ не решаются проблемы существенного уменьшения времени установления переходного процесса и повышения максимальной скорости нарастания выходного напряжения (SR), что обусловлено наличием зоны нечувствительности Uп у входного ДК.

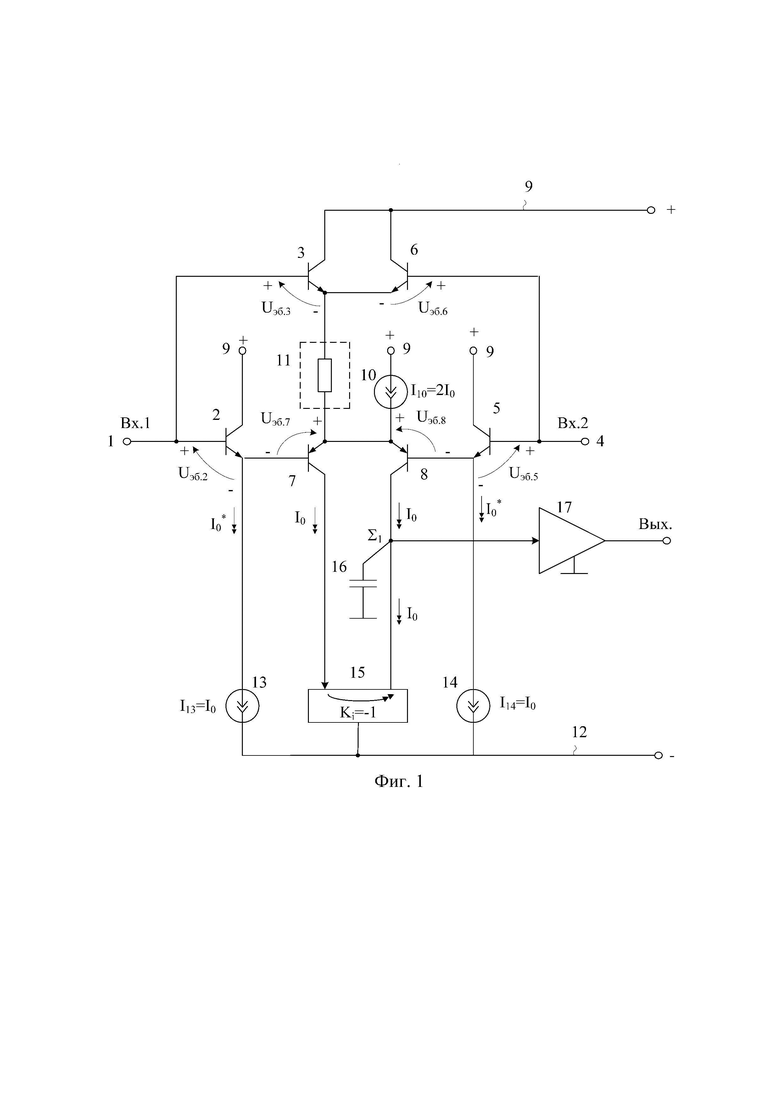

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по Авт. свид. СССР № 500574. ОУ-прототип содержит (фиг.1) первый 1 вход устройства, который соединен с первым 2 и вторым 3 входными транзисторами, второй 4 вход устройства, который связан с третьим 5 и четвертым 6 входными транзисторами, первый 7 и второй 8 транзисторы промежуточного каскада, эмиттеры которых объединены и связаны с первой 9 шиной источника питания через источник опорного тока 10, а также подключены к объединенным эмиттерам второго 3 и четвертого 6 входным транзисторам через корректирующий двухполюсник 11, эмиттеры первого 2 и третьего 5 входных транзисторов связаны связаны со второй 12 шиной источника питания через соответствующие первый 13 и второй 14 токостаблизирующие двухполюсники, коллекторы первого 2, второго 3, третьего 5 и четвертого 6 входных транзисторов согласованы с первой 9 шиной источника питания, коллектор первого 7 транзистора промежуточного каскада подключен ко входу токового зеркала 15, выход которого соединен с коллектором второго 8 транзистора промежуточного каскада, корректирующим конденсатором 16 и входом буферного усилителя 17.

Существенный недостаток известного ОУ фиг. 1 состоит в том, что из-за наличия зоны нечувствительности на проходной характеристике входного ДК, которая создает на переходном процессе «пологий» участок АВ (фиг. 6), время установления его переходного процесса и SR получаются небольшими.

Основная задача предлагаемого изобретения состоит в дальнейшем повышении максимальной скорости нарастания выходного напряжения известной схемы ОУ и уменьшении времени переходного процесса за счет исключения его «пологого» участка АВ (фиг. 6).

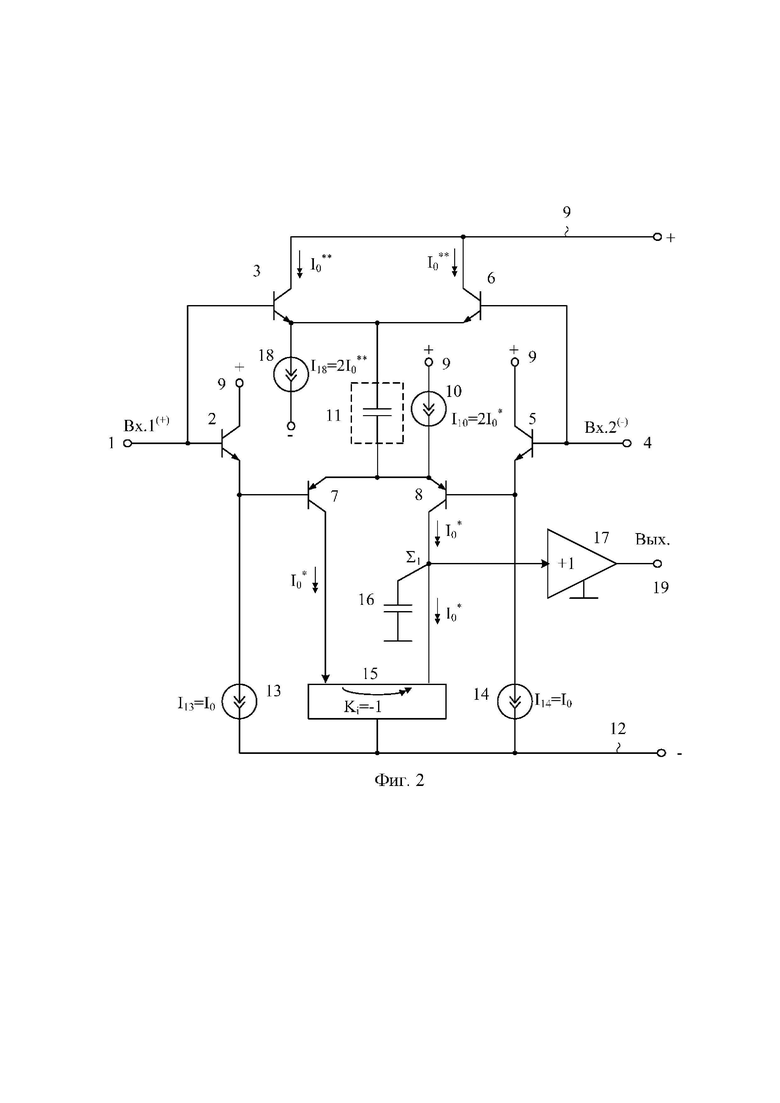

Поставленная задача решается тем, что в операционном усилителе фиг.1, содержащем первый 1 вход устройства, который соединен с первым 2 и вторым 3 входными транзисторами, второй 4 вход устройства, который связан с третьим 5 и четвертым 6 входными транзисторами, первый 7 и второй 8 транзисторы промежуточного каскада, эмиттеры которых объединены и связаны с первой 9 шиной источника питания через источник опорного тока 10, а также подключены к объединенным эмиттерам второго 3 и четвертого 6 входным транзисторам через корректирующий двухполюсник 11, эмиттеры первого 2 и третьего 5 входных транзисторов связаны связаны со второй 12 шиной источника питания через соответствующие первый 13 и второй 14 токостаблизирующие двухполюсники, коллекторы первого 2, второго 3, третьего 5 и четвертого 6 входных транзисторов согласованы с первой 9 шиной источника питания, коллектор первого 7 транзистора промежуточного каскада подключен ко входу токового зеркала 15, выход которого соединен с коллектором второго 8 транзистора промежуточного каскада, корректирующим конденсатором 16 и входом буферного усилителя 17, предусмотрены новые элементы и связи – в качестве корректирующего двухполюсника 11 используется корректирующий конденсатор, а эмиттеры второго 3 и четвертого 6 входных транзисторов связаны со второй 12 шиной источника питания через дополнительный токостабилизирующий двухполюсник 18.

На чертеже фиг. 1 приведена схема операционного усилителя – прототипа.

На чертеже фиг. 2 представлена схема заявляемого ОУ в соответствии с п. 1 формулы изобретения.

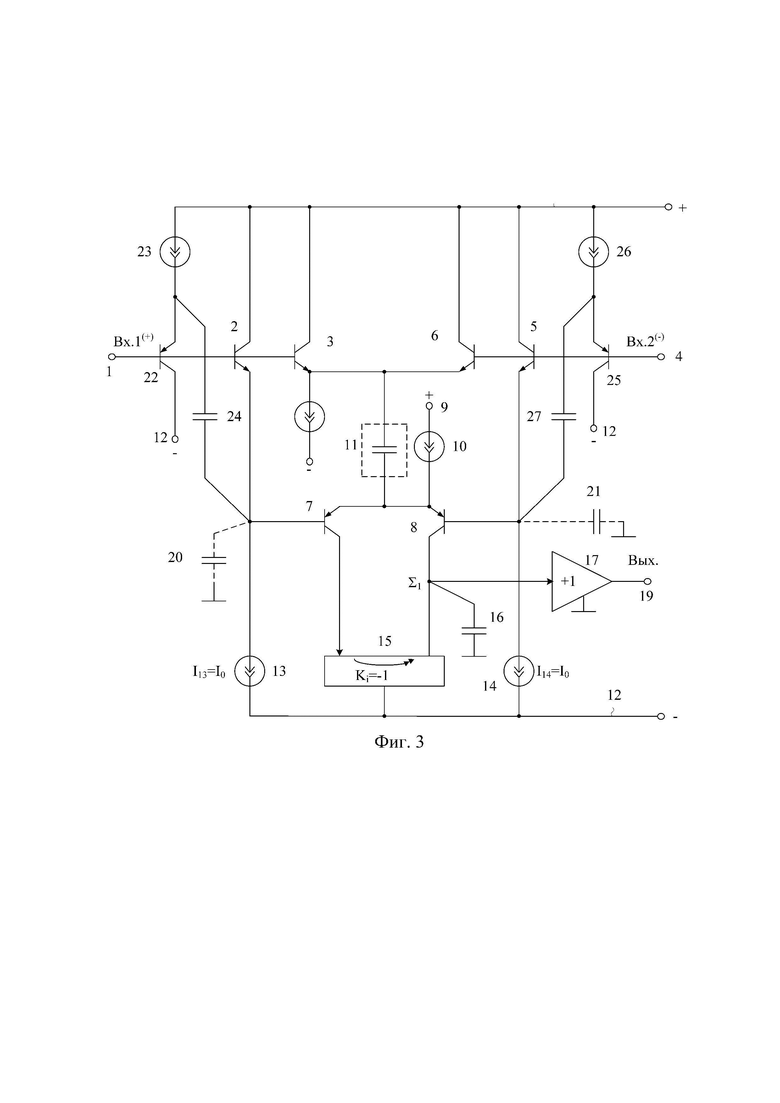

На чертеже фиг. 3 показана схема заявляемого ОУ в соответствии с п. 2 формулы изобретения.

На чертеже фиг. 4 приведен статический режим ОУ - прототипа фиг. 1 в среде LTspice на моделях транзисторов базового матричного кристалла ABMK-2_2-1.lib [13] при t= 27oC, С16=Ск=2пФ, R1=10Ом, I1=I2=100мкА, I3=200мкА, Vcc2= Vcc3=2.5В, Vсс= -Vee=5 В.

На чертеже фиг. 5 представлена логарифмическая амплитудно-частотная характеристика (ЛАЧХ) ОУ-прототипа фиг. 4 в среде LTspice при t= 27oC, С16=Ск=2пФ, R1=10Ом, I1=I2=100мкА, I3=200мкА, Vcc2= Vcc3=2.5В, Vсс= -Vee=5 В.

На чертеже фиг. 6 показан передний фронт переходного процесса ОУ-прототипа фиг. 4 в среде LTspice при t= 27oC, Ск=С16=2пФ, малом сопротивлении резистора R1=10Ом, I1=I2=100мкА, I3=200мкА, Vcc2= Vcc3=2.5В, Vсс= -Vee=5 В. Здесь участок АВ обусловлен наличием зоны нечувствительности Uп на проходной характеристике входного ДК [7,8,11].

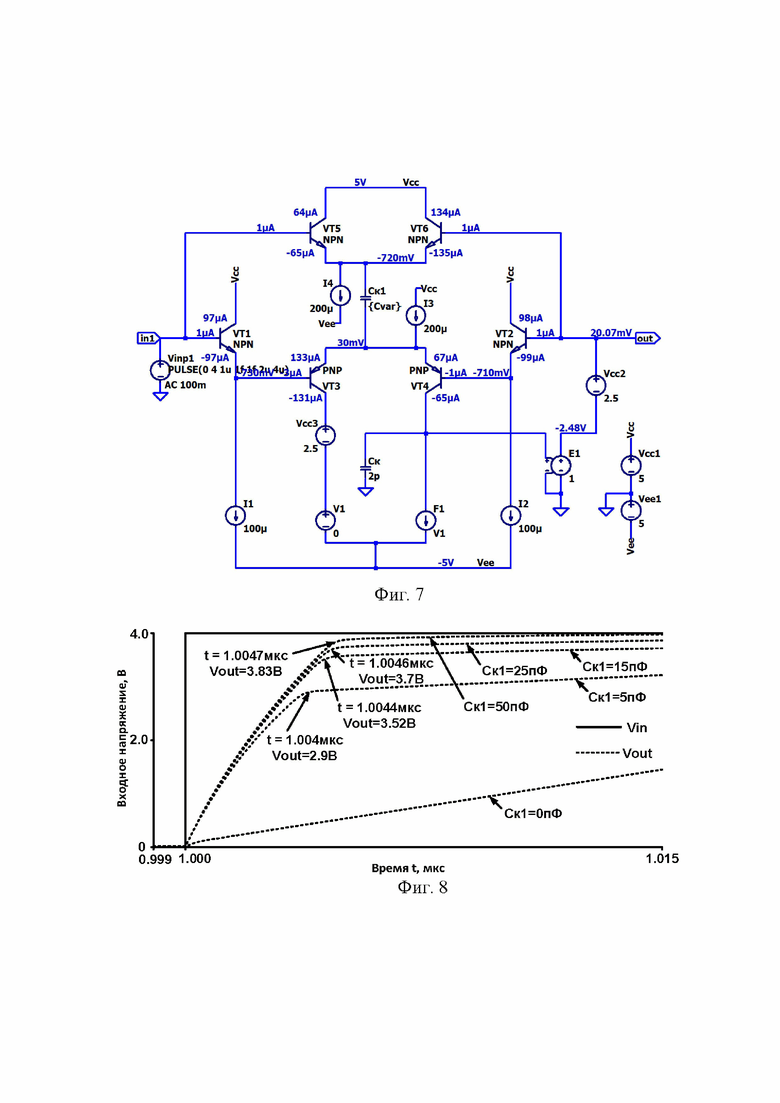

На чертеже фиг. 7 показана схема заявляемого ОУ фиг. 2 в среде LTspice при t=27oC, интегрирующем корректирующем конденсаторе С16=Ск=2пФ и разных значениях параметров корректирующего двухполюсника 11, в качестве которого (в соответствии с п. 1 формулы изобретения) используется конденсатор 11 (Ск1=С11=0пФ; 5пФ; 15пФ; 25пФ; 50пФ), I1=I2=100мкА, I3= I4=200мкА, Vcc2= Vcc3= 2.5В, Vсс= -Vee=5 В.

На чертеже фиг. 8 приведен передний фронт переходного процесса ОУ фиг. 7 (крупный масштаб) в среде LTspice при t= 27oC, С16=Ск=2пФ и разных значениях емкости корректирующего конденсатора 11 (Ск1=С11=0пФ; 5пФ; 15пФ; 25пФ; 50пФ), I1=I2=100мкА, I3= I4=200мкА, Vcc2= Vcc3= 2.5В, Vсс= -Vee=5 В.

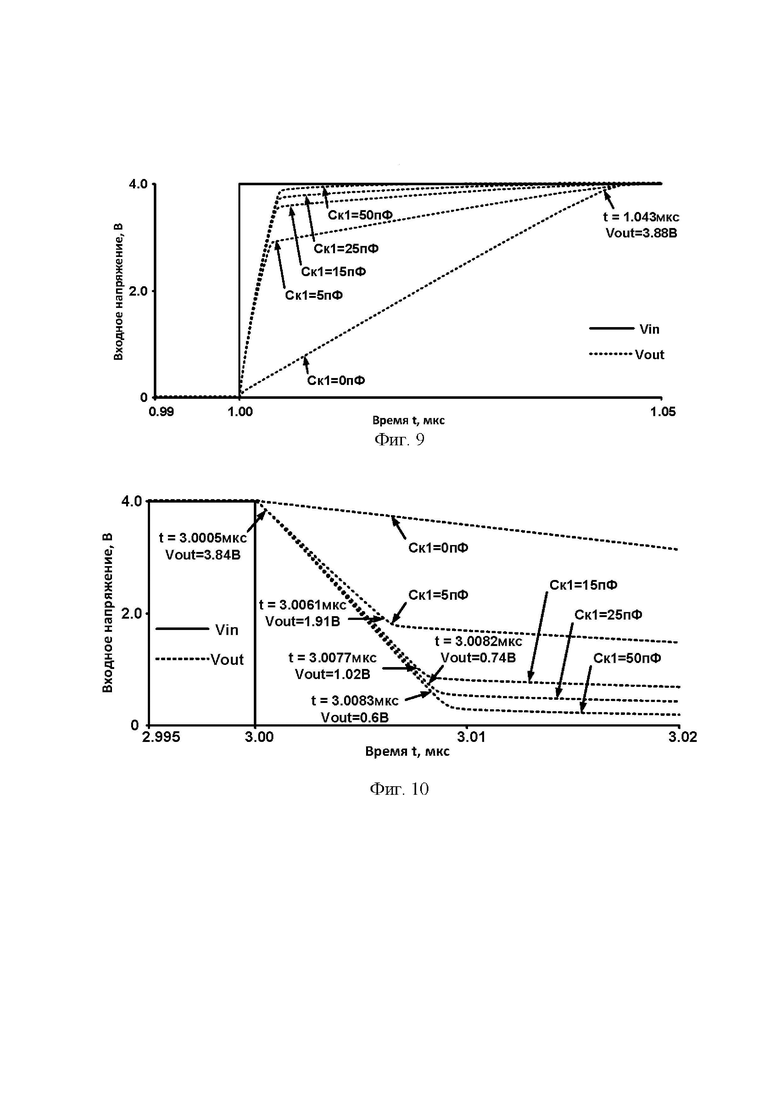

На чертеже фиг. 9 представлен передний фронт переходного процесса ОУ фиг. 7 (мелкий масштаб) в среде LTspice при t= 27oC, С16=Ск=2пФ и разных значениях емкости корректирующего конденсатора 11 (Ск1=С11=0пФ; 5пФ; 15пФ; 25пФ; 50пФ), I1=I2=100мкА, I3= I4=200мкА, Vcc2= Vcc3= 2.5В, Vсс= -Vee=5 В.

На чертеже фиг. 10 показан задний фронт переходного процесса ОУ фиг. 7 в среде LTspice при t= 27oC, С16=Ск=2пФ и разных значениях емкости корректирующего конденсатора 11 (Ск1=С11=0пФ; 5пФ; 15пФ; 25пФ; 50пФ), I1=I2=100мкА, I3= I4=200мкА, Vcc2= Vcc3= 2.5В, Vсс= -Vee=5 В (крупный масштаб).

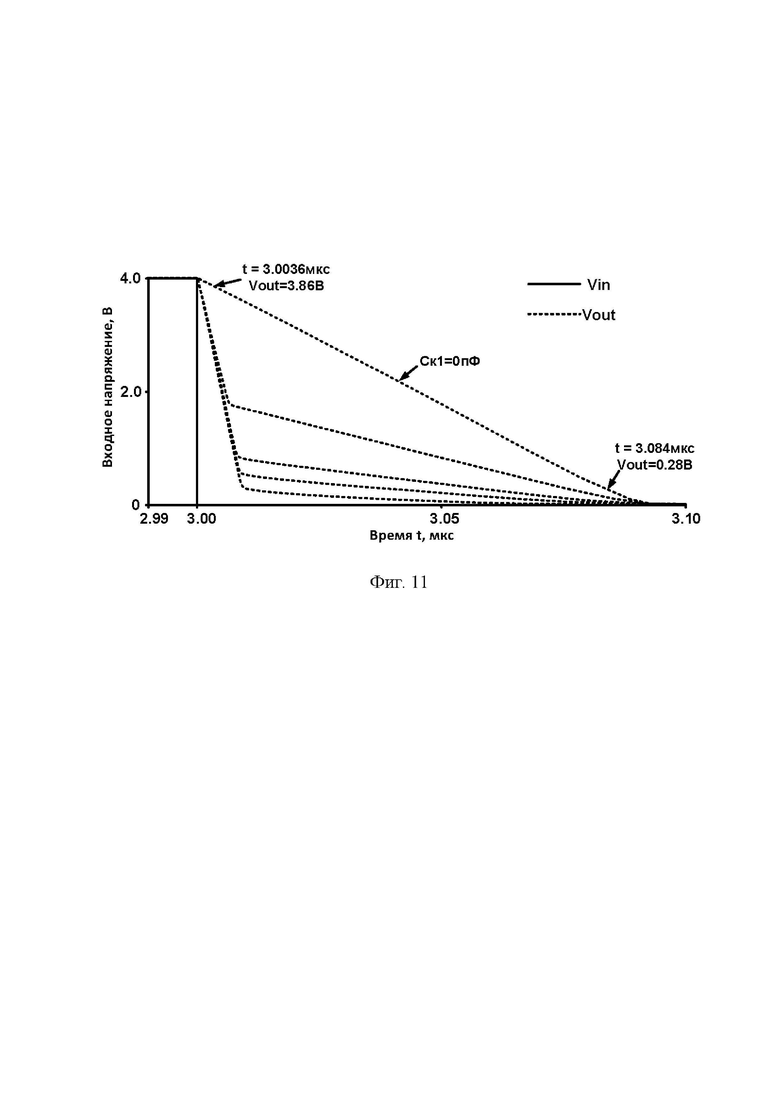

На чертеже фиг. 11 приведен задний фронт переходного процесса ОУ фиг. 7 в среде LTspice при t= 27oC, С16=Ск=2пФ и разных значениях емкости корректирующего конденсатора 11 (Ск1=С11=0пФ; 5пФ; 15пФ; 25пФ; 50пФ), I1=I2=100мкА, I3= I4=200мкА, Vcc2= Vcc3= 2.5В, Vсс= -Vee=5 В (мелкий масштаб).

На чертеже фиг. 12 показан статический режим ОУ фиг. 3 по п. 2 формулы изобретения в среде LTspice при t= 27oC, I1=I2= I5=I6=100мкА, I3= I4=200мкА, Vcc2= Vcc3= 2.5В, Vсс= -Vee=5В.

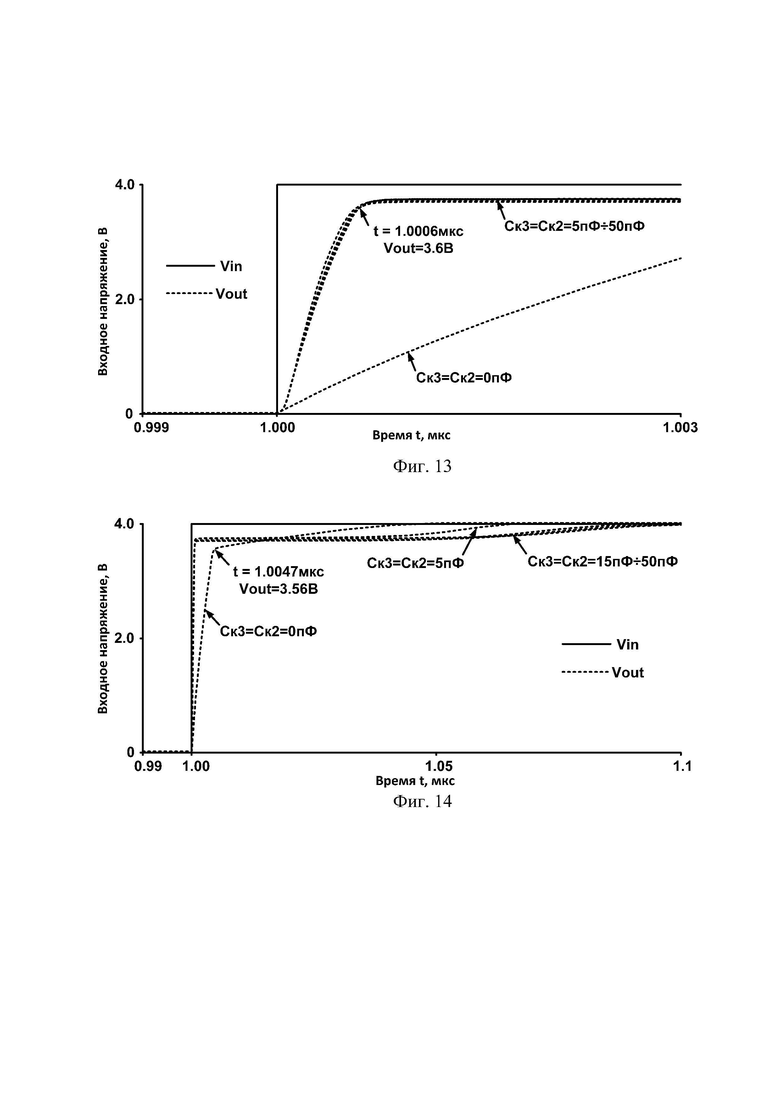

На чертеже фиг. 13 приведен в крупном масштабе передний фронт переходного процесса ОУ фиг. 12 в среде LTspice при t= 27oC, разных значениях емкости дополнительных корректирующих конденсаторов 24 и 27 (Ск3=С24=Ск2=С27=0пФ; 5пФ; 15пФ; 25пФ; 50пФ), С16=Ск=2пФ, С11=Ск1=15пФ, I1=I2= I5=I6=100мкА, I3= I4=200мкА, Vcc2=Vcc3=2.5В, Vсс=-Vee=5В.

На чертеже фиг. 14 представлен в более мелком масштабе передний фронт переходного процесса ОУ фиг. 12 в среде LTspice при t= 27oC, разных значениях емкости дополнительных корректирующих конденсаторов 24 и 27 (Ск3=С24=Ск2=С27= 0пФ; 5пФ; 15пФ; 25пФ; 50пФ), С16=Ск=2пФ, С11=Ск1=15пФ, I1=I2=I5=I6=100мкА, I3=I4=200мкА, Vcc2=Vcc3= 2.5В, Vсс= -Vee=5В.

Быстродействующий операционный усилитель с дифференцирующей цепью коррекции переходного процесса фиг. 2 содержит первый 1 вход устройства, который соединен с первым 2 и вторым 3 входными транзисторами, второй 4 вход устройства, который связан с третьим 5 и четвертым 6 входными транзисторами, первый 7 и второй 8 транзисторы промежуточного каскада, эмиттеры которых объединены и связаны с первой 9 шиной источника питания через источник опорного тока 10, а также подключены к объединенным эмиттерам второго 3 и четвертого 6 входным транзисторам через корректирующий двухполюсник 11, эмиттеры первого 2 и третьего 5 входных транзисторов связаны связаны со второй 12 шиной источника питания через соответствующие первый 13 и второй 14 токостаблизирующие двухполюсники, коллекторы первого 2, второго 3, третьего 5 и четвертого 6 входных транзисторов согласованы с первой 9 шиной источника питания, коллектор первого 7 транзистора промежуточного каскада подключен ко входу токового зеркала 15, выход которого соединен с коллектором второго 8 транзистора промежуточного каскада, корректирующим конденсатором 16 и входом буферного усилителя 17. В качестве корректирующего двухполюсника 11 используется корректирующий конденсатор, а эмиттеры второго 3 и четвертого 6 входных транзисторов связаны со второй 12 шиной источника питания через дополнительный токостабилизирующий двухполюсник 18.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, первый 1 вход устройства подключен к базе первого 22 дополнительного транзистора, эмиттер которого связан с первой 9 шиной источника питания через первый 23 токостабилизирующий двухполюсник и подключен к базе первого 7 транзистора промежуточного каскада через первый 24 дополнительный корректирующий конденсатор, второй 4 вход устройства подключен к базе второго 25 дополнительного транзистора, эмиттер которого связан с первой 9 шиной источника питания через второй 26 токостабилизирующий двухполюсник и связан с базой второго 8 транзистора промежуточного каскада через второй 27 дополнительный корректирующий конденсатор.

Рассмотрим вначале работу ОУ-прототипа фиг. 1 с учетом результатов его моделирования, представленных на чертеже фиг. 6.

Как следует из чертежа фиг. 6, переходный процесс ОУ фиг. 4 характеризуется двумя участками «А» и «В». Причем «пологий» участок «АВ» связан с зоной нечувствительности Uп на проходной характеристике входного каскада [8-12]. Из данного графика следует, что суммарное время установления переходного процесса, определяемое как сумма tA+tB получается сравнительно большим. Однако, известный ОУ имеет в целом более высокие значения SR (393 В/мкс), чем ОУ без цепей нелинейной коррекции (при отсутствии VT3, VT6 в схеме фиг. 1).

Рассмотрим работу предлагаемого ОУ фиг. 2. Схема для моделирования ОУ фиг. 2, соответствующая п. 1 формулы изобретения, представленная на чертеже фиг. 8, а также результаты ее компьютерного моделирования, представленные на чертежах фиг. 9, фиг. 10, фиг. 11, фиг. 12, показывают, что предлагаемый ОУ по п. 1 формулы изобретения обеспечивает увеличение почти на порядок SR (с 45 В/мкс до 415 В/мкс), а также уменьшает время установления переходного процесса.

Таблица 1: Значение SR при С16=Ск=2пФ, и разных значениях емкости корректирующего конденсатора 11 (С11=Ск1= 0пФ; 5пФ; 15пФ; 25пФ; 50пФ), Vcc2= Vcc3= 2.5В, Vсс= -Vee=5В

Дальнейшее повышение SR ОУ, предусмотренное п. 2 формулы изобретения, обеспечивается введением в схему ОУ по п. 1 дополнительных транзисторов 22, 23 и дополнительных корректирующих конденсаторов 24, 27. Соответствующее компьютерное моделирование влияния данных дополнительных элементов на переходные процессы представлено на чертежах фиг. 13, фиг. 14 и таблице 2. В частности, из таблицы 2 следует, что дополнительные элементы 22, 23, 24, 27 обеспечивают дальнейшее повышение SR с 394 В/мкс до 3266 В/мкс.

Таблица 2: Значение SR ОУ фиг. 3 (фиг. 12) при разных значениях емкостей дополнительных корректирующих конденсаторов 24 и 27 (Ск3=С24=Ск2=С27= 0пФ; 5пФ; 15пФ; 25пФ; 50пФ), С16=Ск= 2пФ, С11=Ск1= 15пФ

Таким образом, из таблицы 1 и таблицы 2 следует, что заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения замкнутого ОУ и времени установления переходного процесса.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. E. J. Wyers, "Accurate Geometric Programming-Compatible Slew Rate Modeling for Two-Stage Operational Amplifier Design Optimization," 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Shenzhen, China, 2022, pp. 185-189. doi: 10.1109/APCCAS55924.2022.10090335

2. J. Ramirez-Angulo and M. Holmes, "A simple technique to significantly enhance slew rate and bandwidth of one-stage CMOS operational amplifiers," 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 2002, pp. II-II. doi: 10.1109/ISCAS.2002.1011483

3. Авт.св. СССР № 500574, G06G 7/12

4. Прокопенко, Н.Н. Повышение быстродействия дифференциальных операционных усилителей с входными каскадами Дарлингтона // Известия ЛЭТИ им. В.И. Ульянова (Ленина). – Л., 1975. – Вып. 176. – С. 103–105.

5. Патент US 6.831.515, 2004 г.

6. Авт. св. СССР 469975, 1973 г.

7. Операционный усилитель фирмы National Semiconductor (США) LM6142/44. URL: https://www.promelec.ru/fs/sources/2a/82/6c/0f/4fb735e529e1edaee32cd021.pdf, fig.1, fig. 2

Публикации о влиянии зоны нечувствительности на проходной характеристике входного каскада ОУ на переходные процессы

8. N. Prokopenko, V. Chumakov, A. Bugakova and A. Gaiduk, "Overview of the Nonlinear Dynamic's Basic Equations of Op-Amps in Large Signal Mode," 2022 IEEE International Conference on Design & Test of Integrated Micro & Nano-Systems (DTS), 2022, June 6-9, 2022, Cairo, Egypt, pp. 01-06, doi: 10.1109/DTS55284.2022.9809859.

9. V. V. Ivanov, I. M. Filanovsky, “Operational Amplifier Speed and Accuracy Improvement,” Springer, Boston, 2004, 194 p. doi: 10.1007/b105872

10. N. Prokopenko, A. Bugakova, A. Gaiduk, “Research of Operational Amplifiers with Nonlinear Drivers of Correction Capacity,” IEEE 15th East-West Design & Test Symposium (EWDTS 2017), Novi Sad, Serbia, 2017, pp. 637-640. DOI: 10.1109/EWDTS.2017.8110044.

11. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

12. Входной каскад быстродействующего операционного усилителя с повышенным ослаблением синфазного сигнала / С.В.Крюков, Н.Н.Прокопенко, А.В. Хорунжий // Проблемы современной аналоговой микросхемотехники: Материалы VI Международного научно-практического семинара. Ч.1. / ЮРГУЭС.- Шахты: Изд-во ЮРГУЭС, 2007.- С.74-77.

13. Элементная база радиационно-стойких информационно-измерительных систем : монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский ; под общ. ред. д.т.н. проф. Н.Н. Прокопенко ; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». – Шахты : ФГБОУ ВПО «ЮРГУЭС», 2011. – 208 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2802049C1 |

| Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения | 2023 |

|

RU2810544C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| Быстродействующий операционный усилитель на основе комплементарного "перегнутого" каскода | 2023 |

|

RU2813280C1 |

| Быстродействующий операционный усилитель | 2024 |

|

RU2822112C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2023 |

|

RU2802051C1 |

| Быстродействующий операционный усилитель с повышенной скоростью нарастания выходного напряжения | 2018 |

|

RU2683160C1 |

Изобретение относится к радиоэлектронике. Технический результат: повышение максимальной скорости нарастания выходного напряжения быстродействующего ОУ и уменьшение времени переходного процесса. Для этого предложен быстродействующий операционный усилитель с дифференцирующей цепью коррекции переходного процесса, в котором в качестве корректирующего двухполюсника (11) используется корректирующий конденсатор, а эмиттеры второго (3) и четвертого (6) входных транзисторов связаны со второй (12) шиной источника питания через дополнительный токостабилизирующий двухполюсник (18). 1 з.п. ф-лы, 14 ил., 2 табл.

1. Быстродействующий операционный усилитель с дифференцирующей цепью коррекции переходного процесса, содержащий первый (1) вход устройства, который соединен с первым (2) и вторым (3) входными транзисторами, второй (4) вход устройства, который связан с третьим (5) и четвертым (6) входными транзисторами, первый (7) и второй (8) транзисторы промежуточного каскада, эмиттеры которых объединены и связаны с первой (9) шиной источника питания через источник опорного тока (10), а также подключены к объединенным эмиттерам второго (3) и четвертого (6) входным транзисторам через корректирующий двухполюсник (11), эмиттеры первого (2) и третьего (5) входных транзисторов связаны со второй (12) шиной источника питания через соответствующие первый (13) и второй (14) токостаблизирующие двухполюсники, коллекторы первого (2), второго (3), третьего (5) и четвертого (6) входных транзисторов согласованы с первой (9) шиной источника питания, коллектор первого (7) транзистора промежуточного каскада подключен ко входу токового зеркала (15), выход которого соединен с коллектором второго (8) транзистора промежуточного каскада, корректирующим конденсатором (16) и входом буферного усилителя (17), отличающийся тем, что в качестве корректирующего двухполюсника (11) используется корректирующий конденсатор, а эмиттеры второго (3) и четвертого (6) входных транзисторов связаны со второй (12) шиной источника питания через дополнительный токостабилизирующий двухполюсник (18).

2. Быстродействующий операционный усилитель с дифференцирующей цепью коррекции переходного процесса по п. 1, отличающийся тем, что первый (1) вход устройства подключен к базе первого (22) дополнительного транзистора, эмиттер которого связан с первой (9) шиной источника питания через первый (23) токостабилизирующий двухполюсник и подключен к базе первого (7) транзистора промежуточного каскада через первый (24) дополнительный корректирующий конденсатор, второй (4) вход устройства подключен к базе второго (25) дополнительного транзистора, эмиттер которого связан с первой (9) шиной источника питания через второй (26) токостабилизирующий двухполюсник и связан с базой второго (8) транзистора промежуточного каскада через второй (27) дополнительный корректирующий конденсатор.

| Операционный усилитель | 1974 |

|

SU500574A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| US 5455535 A1, 03.10.1995. | |||

Авторы

Даты

2024-01-11—Публикация

2023-10-09—Подача