Изобретение относится к радиоэлектронике и может быть использовано в структуре операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения (SR), а также в драйверах быстродействующих аналого-цифровых преобразователей.

К числу серийных ОУ со средними значениями максимальной скорости нарастания выходного напряжения (SR≈20 В/мкс) относят микросхему НА2700 и ее российский аналог 154УД1.

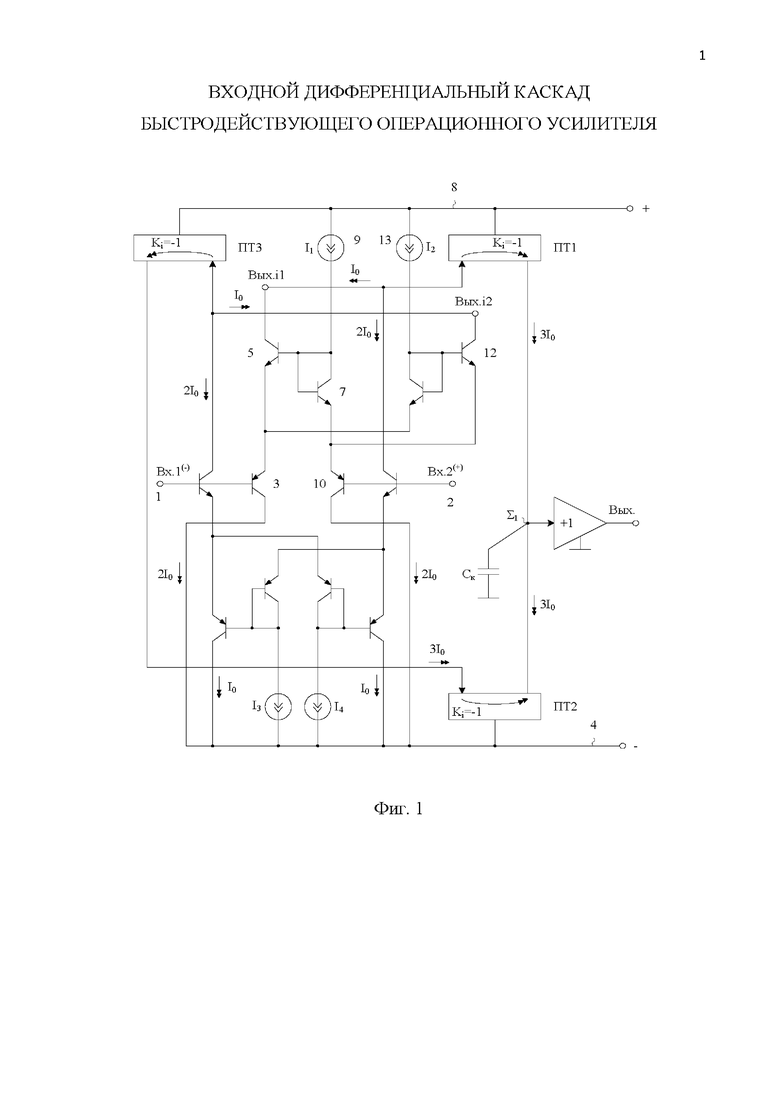

Ближайшим прототипом заявляемого устройства является входной дифференциальный каскад фиг. 1 в структуре микросхемы HA2700 «Матавкин В. Быстродействующие операционные усилители. - М: Радио и связь, 1989. - С. 91, рис. 5.18». Кроме этого структура микросхемы HA2700 представлена в справочнике компании Harris Semiconductor “Linear& Data Acquisition Products”, volume 1, стр. 2-59 (http://www.bitsavers.org/components/harris/1977_Harris_Linear_and_Data_Acquisition_Products_Volume_1.pdf).

Входной дифференциальный каскад-прототип фиг. 1 содержит первый дифференциальный каскад ДК1, включающий первый 1 и второй 2 входы устройства, первый 3 входной биполярный транзистор, база которого подключена к первому 1 входу устройства, коллектор связан с первой 4 шиной источника питания, а эмиттер соединен с эмиттером первого 5 выходного биполярного транзистора, коллектор первого 5 выходного биполярного транзистора связан с первым 6 основным токовым выходом устройства, согласованным со второй 8 шиной источника питания, база первого 5 выходного биполярного транзистора соединена с коллектором и базой первого 7 согласующего биполярного транзистора и связана со второй 8 шиной источника питания через первый 9 источник опорного тока, эмиттер первого 7 согласующего биполярного транзистора соединен с эмиттером второго 10 входного биполярного транзистора, коллектор которого связан с первой 4 шиной источника питания, а база соединена со вторым 2 входом устройства, второй 11 согласующий биполярный транзистор, коллектор которого соединен с его базой и подключен к базе второго 12 выходного биполярного транзистора и через второй 13 источник опорного тока соединен со второй 8 шиной источника питания.

Существенный недостаток известного дифференциального каскада фиг. 1 состоит в том, что при его практическом использовании в схеме ОУ он обеспечивает сравнительно малые значения SR (не более 20 В/мкс). Этот недостаток связан с отрицательным влиянием на фронт переходного процесса паразитных емкостей Ср9 и Ср13, которые определяются выходной емкостью источников опорного тока 9 и 13 и паразитными емкостями на подложку транзисторов 7 и 11.

Основная задача заявляемого схемотехнического решения состоит в создании входного дифференциального каскада и схемы его включения в быстродействующем ОУ, которое обеспечивает повышенный уровень SR (до 800 В/мкс) при использовании классических (не СВЧ) кремниевых технологических процессов, освоенных многими российскими предприятиями.

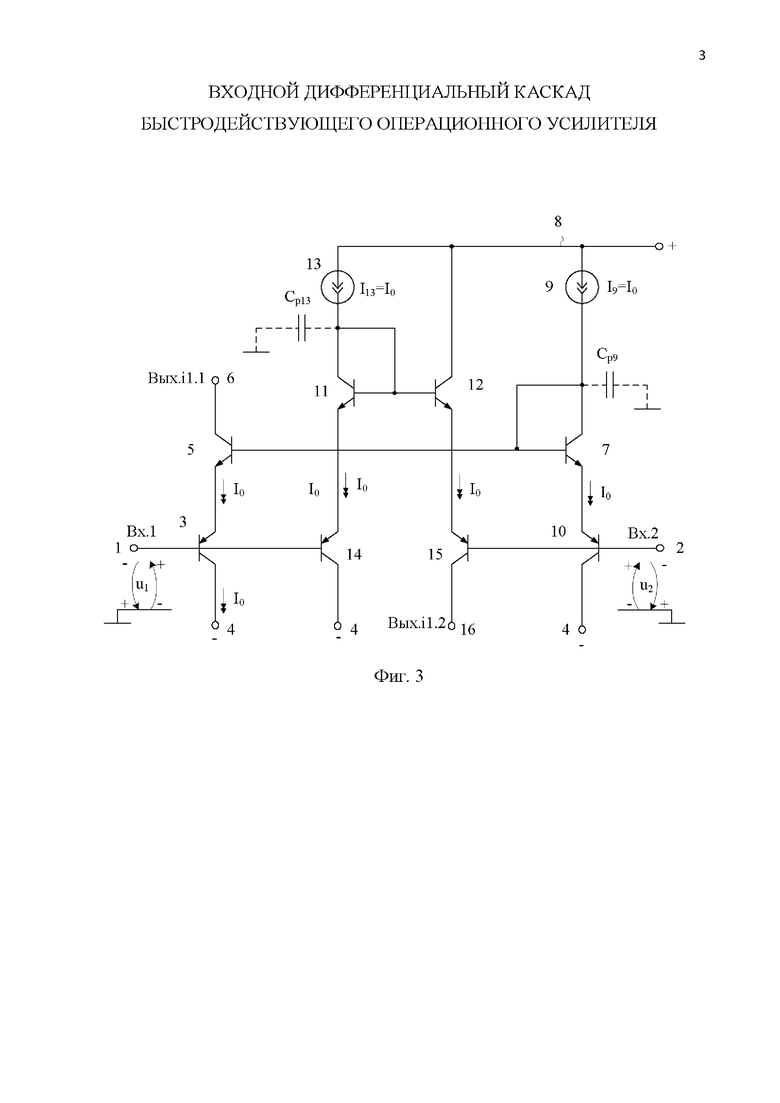

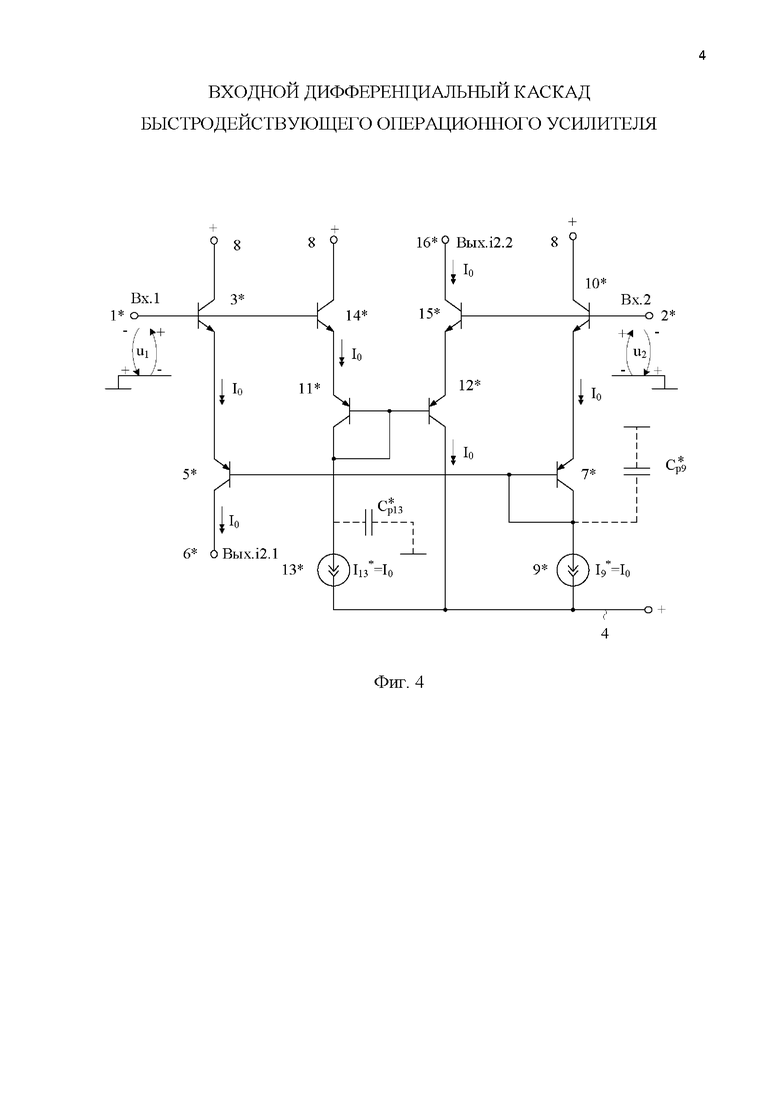

Поставленная задача достигается тем, что во входном дифференциальном каскаде быстродействующего операционного усилителя фиг.1, содержащем первый дифференциальный каскад ДК1, включающий первый 1 и второй 2 входы устройства, первый 3 входной биполярный транзистор, база которого подключена к первому 1 входу устройства, коллектор связан с первой 4 шиной источника питания, а эмиттер соединен с эмиттером первого 5 выходного биполярного транзистора, коллектор первого 5 выходного биполярного транзистора связан с первым 6 основным токовым выходом устройства, согласованным со второй 8 шиной источника питания, база первого 5 выходного биполярного транзистора соединена с коллектором и базой первого 7 согласующего биполярного транзистора и связана со второй 8 шиной источника питания через первый 9 источник опорного тока, эмиттер первого 7 согласующего биполярного транзистора соединен с эмиттером второго 10 входного биполярного транзистора, коллектор которого связан с первой 4 шиной источника питания, а база соединена со вторым 2 входом устройства, второй 11 согласующий биполярный транзистор, коллектор которого соединен с его базой и подключен к базе второго 12 выходного биполярного транзистора и через второй 13 источник опорного тока соединен со второй 8 шиной источника питания, предусмотрены новые элементы и связи - первый дифференциальный каскад ДК1 дополнительно включает первый 14 и второй 15 дополнительные биполярные транзисторы, причем база первого 14 дополнительного биполярного транзистора соединена с первым 1 входом устройства, коллектор - подключен к первой 4 шине источника питания, а эмиттер соединен с эмиттером второго 11 согласующего биполярного транзистора, база второго 15 дополнительного биполярного транзистора соединена со вторым 2 входом устройства, коллектор - подключен к дополнительному 16 токовому выходу ДК1, согласованному с первой 4 шиной источника питания, а эмиттер соединен с эмиттером второго 12 выходного биполярного транзистора, коллектор второго 12 выходного транзистора связан со второй 8 шиной источника питания, причем заявляемое устройство состоит из первого ДК1 и второго ДК2 дифференциальных каскадов, каждый из которых содержит первый 1, 1* и второй входы 2, 2* устройства, первый 3, 3* входной биполярный транзистор, база которого подключена к первому 1, 1* входу устройства, а эмиттер соединен с эмиттером первого 5, 5* выходного биполярного транзистора, коллектор первого 5, 5* выходного биполярного транзистора связан с основным (первым 6 и вторым 6*) токовым выходом устройства, база первого 5, 5* выходного биполярного транзистора соединена с коллектором и базой первого 7, 7* согласующего биполярного транзистора, эмиттер первого 7, 7* согласующего биполярного транзистора соединен с эмиттером второго 10, 10* входного биполярного транзистора, база которого соединена со вторым 2, 2* входом устройства, второй 11, 11* согласующий биполярный транзистор, коллектор которого соединен с его базой и подключен к базе второго 12, 12* выходного биполярного транзистора, а также первый 14, 14* и второй 15, 15* дополнительные биполярные транзисторы, причем база первого 14, 14* дополнительного биполярного транзистора соединена с первым 1, 1* входом устройства, а эмиттер соединен с эмиттером второго 11, 11* согласующего биполярного транзистора, база второго 15, 15* дополнительного биполярного транзистора соединена со вторым 2, 2* входом устройства, коллектор подключен к дополнительному 16, 16* токовому выходу, а эмиттер соединен с эмиттером второго 12, 12* выходного биполярного транзистора, при этом в первом ДК1 первый 3 входной, второй 10 входной, первый 14 и второй 15 дополнительные биполярные транзисторы имеют p-n-p структуру, а первый 5 выходной, первый 7 и второй 11 согласующие, второй 12 выходной биполярные транзисторы имеют n-p-n структуру, причем во втором ДК2 первый 3* входной, второй 10* входной, первый 14* и второй 15* дополнительные биполярные транзисторы имеют n-p-n структуру, а первый 5* выходной, первый 7* и второй 11* согласующие, второй 12* выходной биполярные транзисторы имеют p-n-p структуру, а во втором ДК2 дополнительный 16* токовый выход согласован со второй 8 шиной источника питания, коллектор первого 7* согласующего биполярного транзистора соединен с первой 4 шиной источника питания через первый 9* источник опорного тока, коллектор второго 11* согласующего биполярного транзистора соединен с первой 4 шиной источника питания через второй 13* источник опорного тока, коллекторы первого 3* входного биполярного транзистора, первого 14* дополнительного биполярного транзистора и второго 10* входного биполярного транзистора связаны со второй 8 шиной источника питания, причем первая 4 шина источника питания обеспечивает отрицательное напряжение, а вторая 8 шина источника питания обеспечивает положительное напряжение, при этом первый 1 вход первого ДК1 соединен с первым 1* входом второго ДК2, второй 2 вход первого ДК1 соединен со вторым 2* входом второго ДК2, а первый 6 основной токовый выход устройства соединен с дополнительным 16* токовым выходом второго ДК2, а дополнительный 16 токовый выход первого ДК1 соединен со вторым 6* основным токовым выходом устройства.

На чертеже фиг. 1 приведена схема входного дифференциального каскада-прототипа в структуре операционного усилителя HA2700 и его российского аналога 154УД1.

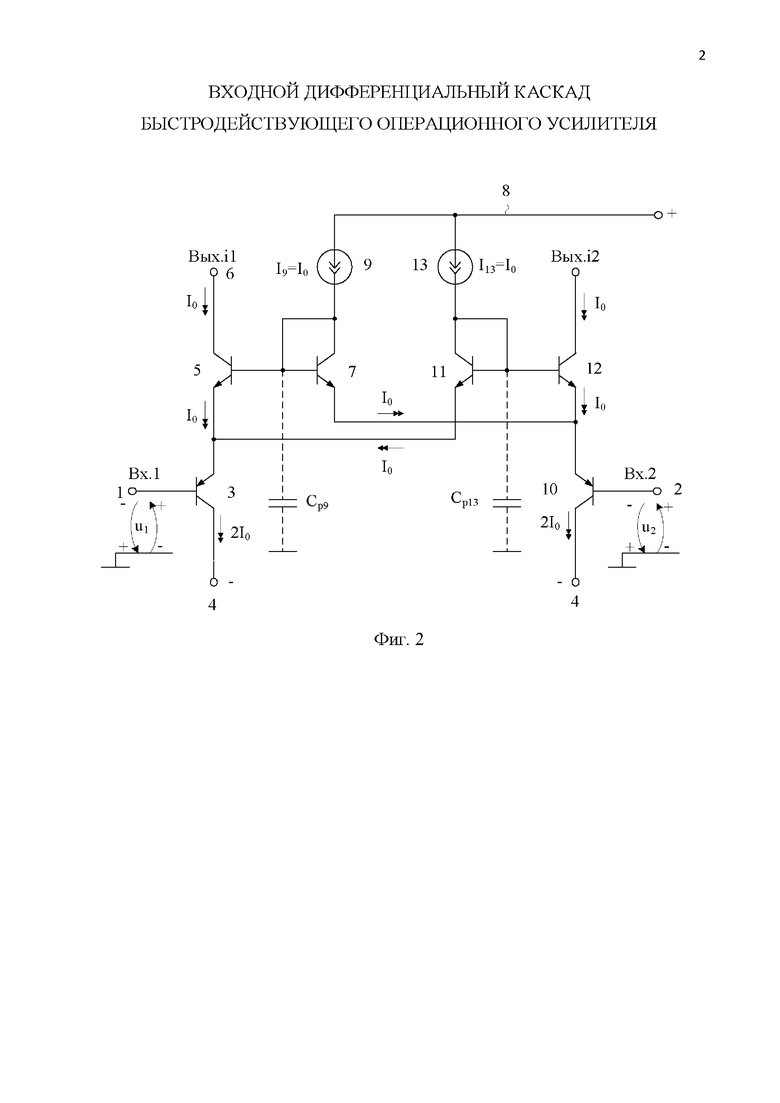

На чертеже фиг. 2 показана схема заявляемого входного дифференциального каскада быстродействующего ОУ в соответствии с формулой изобретения.

На чертеже фиг. 3 представлена схема первого ДК1 в заявляемом устройстве, которое содержит ДК1 и ДК2.

На чертеже фиг. 4 приведена схема второго дифференциального каскада (ДК2).

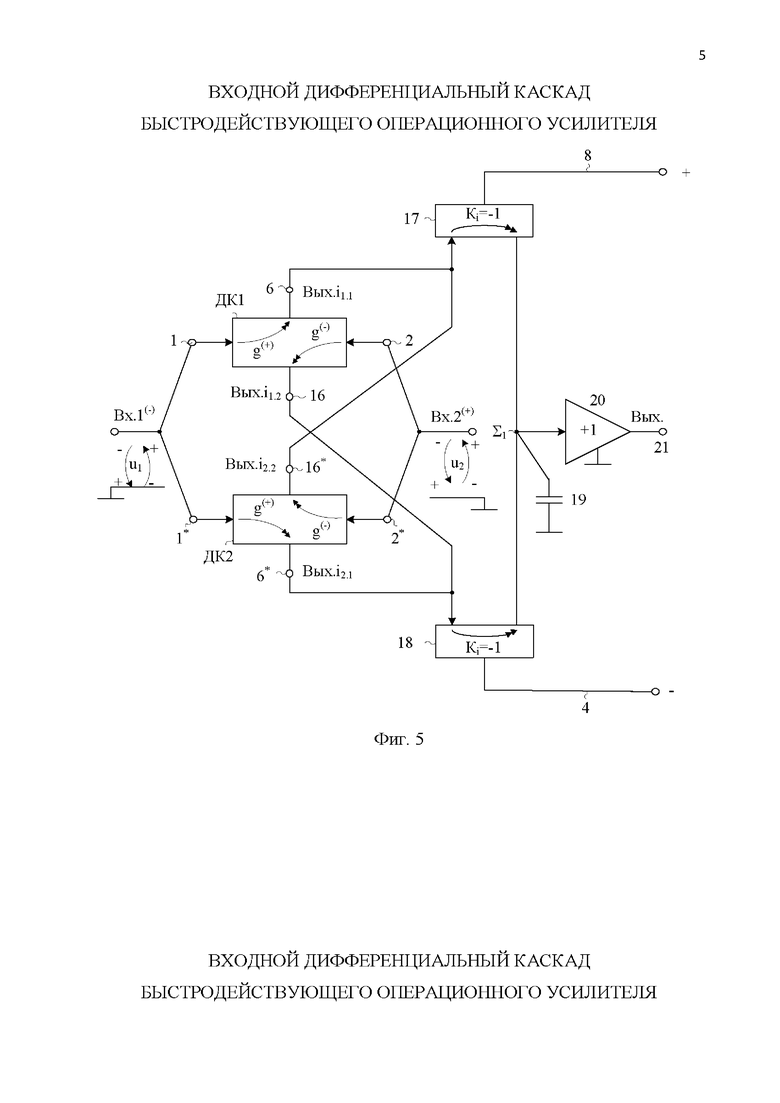

На чертеже фиг. 5 показана функциональная схема включения заявляемого устройства с ДК1 и ДК2 (фиг. 2) в структуре быстродействующего ОУ с двумя токовыми зеркалами 17 и 18, интегрирующим корректирующим конденсатором 19, буферным усилителем 20, выход которого 21 является потенциальным выходом ОУ.

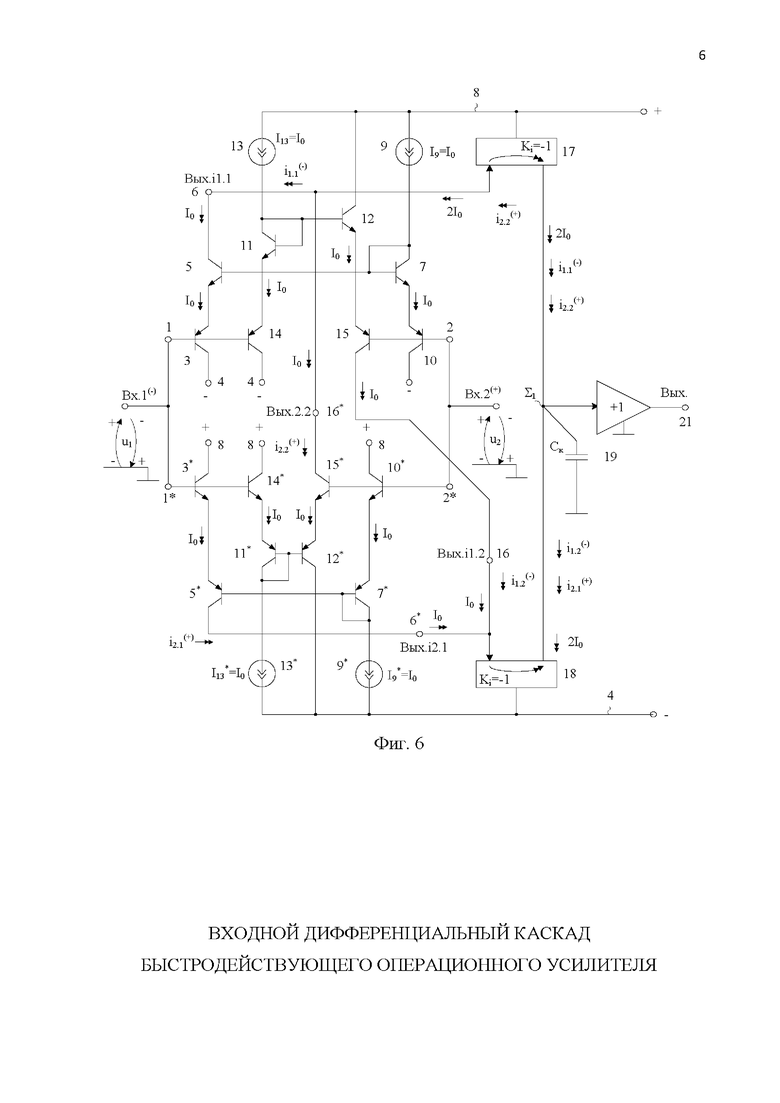

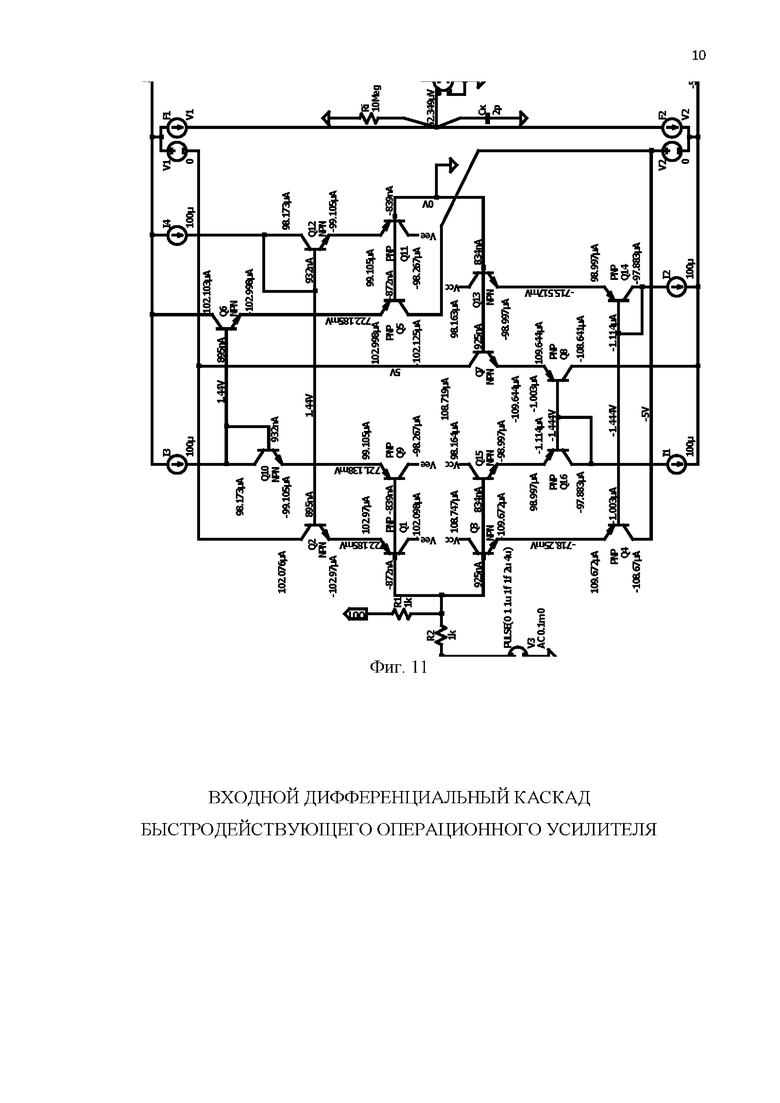

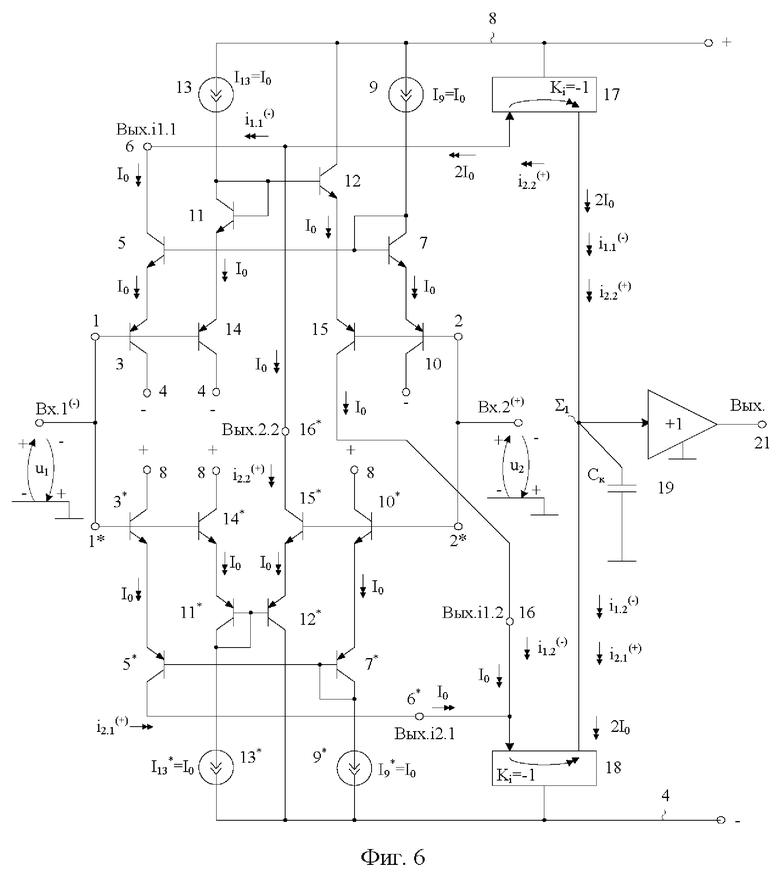

На чертеже фиг. 6 представлена схема включения заявляемого входного каскада в структуре быстродействующего ОУ с двумя токовыми зеркалами 17 и 18, соответствующая функциональной схеме фиг. 5.

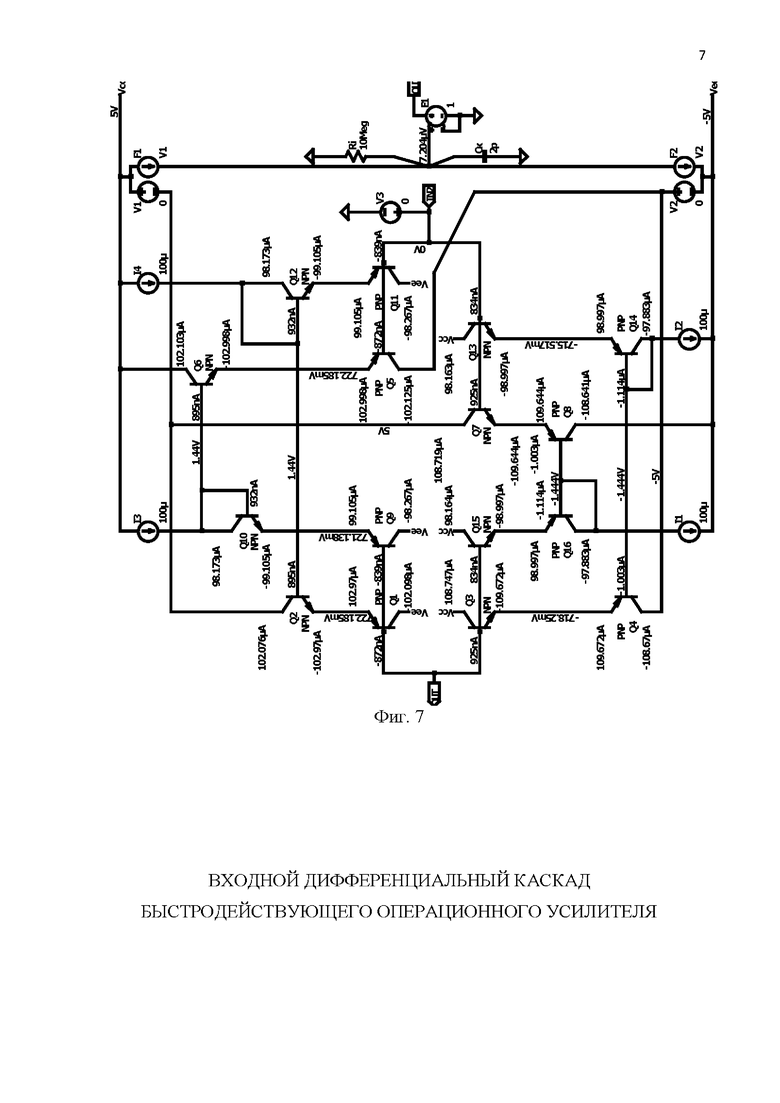

На чертеже фиг. 7 приведен статический режим быстродействующего ОУ фиг. 6 в среде LTspice при t=27°C, Vcc=5В, Vee=-5В, I1÷I4=100мкА, Ск=2пФ на моделях биполярных транзисторов [4].

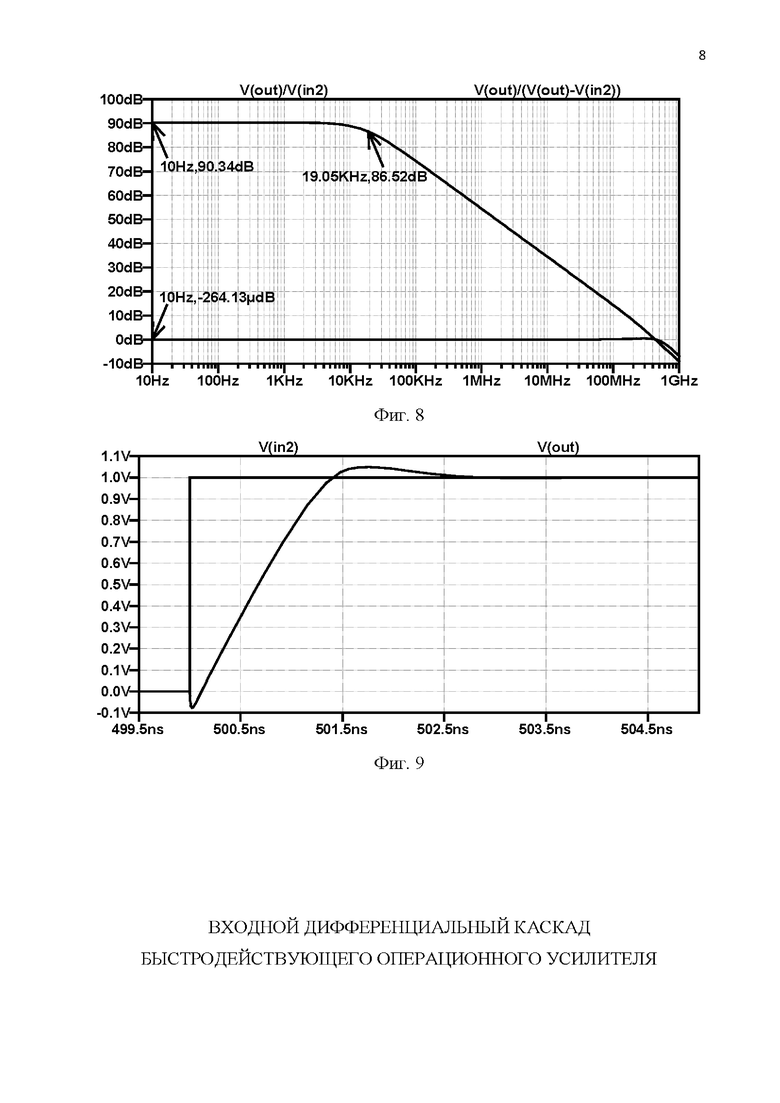

На чертеже фиг. 8 показана логарифмическая амплитудно-частотная характеристика быстродействующего ОУ фиг. 7 в среде LTspice.

На чертеже фиг. 9 представлен передний фронт переходного процесса быстродействующего ОУ фиг. 7 в неинвертирующем включении.

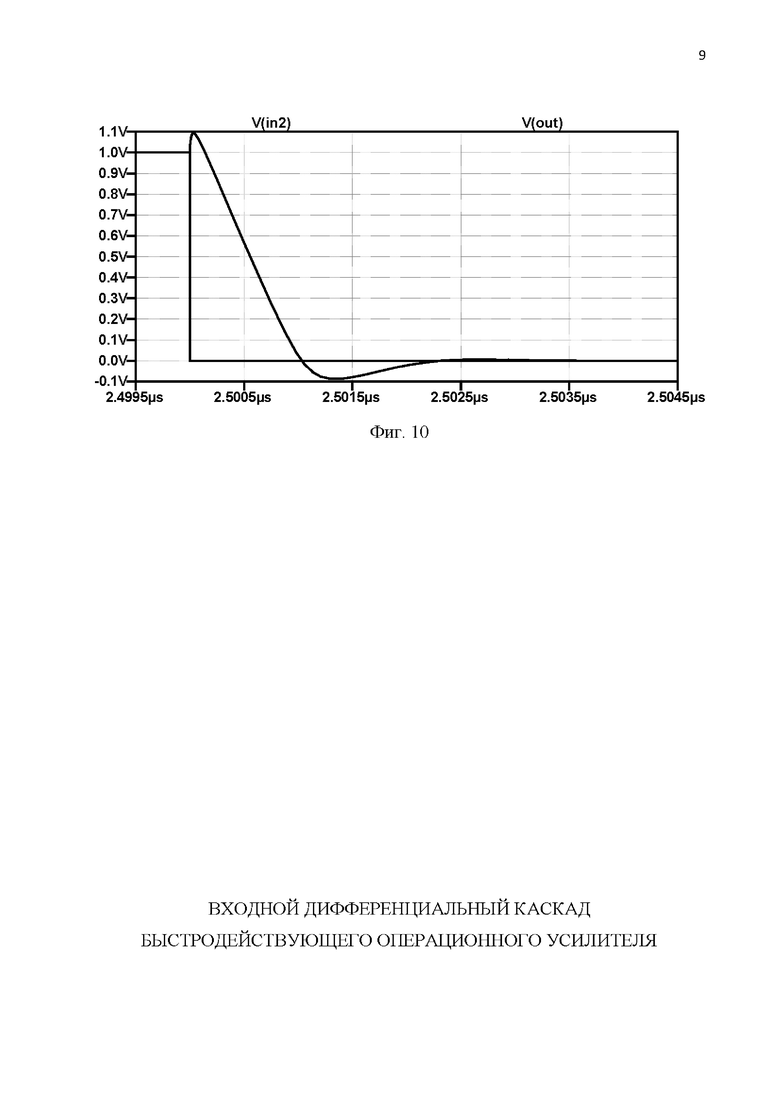

На чертеже фиг. 10 приведен задний фронт переходного процесса быстродействующего ОУ фиг. 7 в неинвертирующем включении в среде LTspice.

На чертеже фиг. 11 показан статический режим быстродействующего ОУ фиг. 6 в инвертирующем включении в среде LTspice при резисторах обратной связи R1=R2=1кОм.

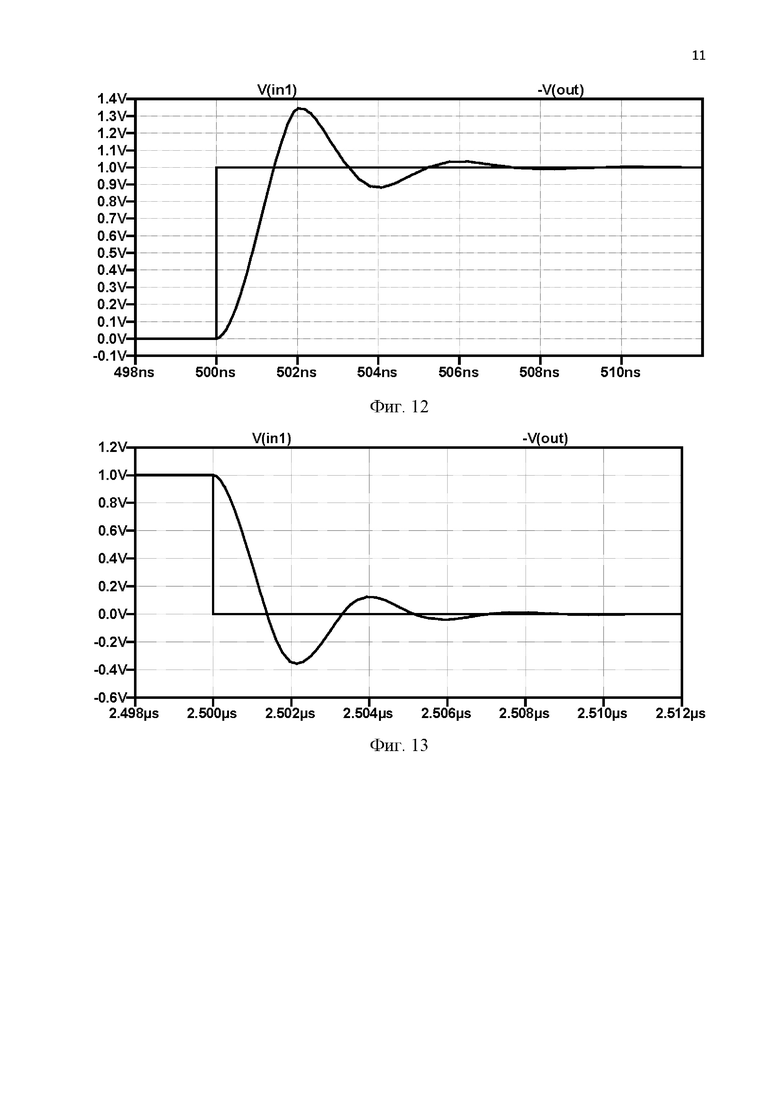

На чертеже фиг. 12 представлен передний фронт переходного процесса быстродействующего ОУ фиг. 11 при инвертирующем включении в среде LTspice.

На чертеже фиг. 13 приведен задний фронт переходного процесса быстродействующего ОУ фиг. 11 при инвертирующем включении в среде LTspice.

Входной дифференциальный каскад быстродействующего операционного усилителя фиг. 2 содержит первый дифференциальный каскад ДК1, включающий первый 1 и второй 2 входы устройства, первый 3 входной биполярный транзистор, база которого подключена к первому 1 входу устройства, коллектор связан с первой 4 шиной источника питания, а эмиттер соединен с эмиттером первого 5 выходного биполярного транзистора, коллектор первого 5 выходного биполярного транзистора связан с первым 6 основным токовым выходом устройства, согласованным со второй 8 шиной источника питания, база первого 5 выходного биполярного транзистора соединена с коллектором и базой первого 7 согласующего биполярного транзистора и связана со второй 8 шиной источника питания через первый 9 источник опорного тока, эмиттер первого 7 согласующего биполярного транзистора соединен с эмиттером второго 10 входного биполярного транзистора, коллектор которого связан с первой 4 шиной источника питания, а база соединена со вторым 2 входом устройства, второй 11 согласующий биполярный транзистор, коллектор которого соединен с его базой и подключен к базе второго 12 выходного биполярного транзистора и через второй 13 источник опорного тока соединен со второй 8 шиной источника питания. Первый дифференциальный каскад ДК1 дополнительно включает первый 14 и второй 15 дополнительные биполярные транзисторы, причем база первого 14 дополнительного биполярного транзистора соединена с первым 1 входом устройства, коллектор - подключен к первой 4 шине источника питания, а эмиттер соединен с эмиттером второго 11 согласующего биполярного транзистора, база второго 15 дополнительного биполярного транзистора соединена со вторым 2 входом устройства, коллектор - подключен к дополнительному 16 токовому выходу ДК1, согласованному с первой 4 шиной источника питания, а эмиттер соединен с эмиттером второго 12 выходного биполярного транзистора, коллектор второго 12 выходного транзистора связан со второй 8 шиной источника питания, причем заявляемое устройство состоит из первого ДК1 и второго ДК2 дифференциальных каскадов, каждый из которых содержит первый 1, 1* и второй входы 2, 2* устройства, первый 3, 3* входной биполярный транзистор, база которого подключена к первому 1, 1* входу устройства, а эмиттер соединен с эмиттером первого 5, 5* выходного биполярного транзистора, коллектор первого 5, 5* выходного биполярного транзистора связан с основным (первым 6 и вторым 6*) токовым выходом устройства, база первого 5, 5* выходного биполярного транзистора соединена с коллектором и базой первого 7, 7* согласующего биполярного транзистора, эмиттер первого 7, 7* согласующего биполярного транзистора соединен с эмиттером второго 10, 10* входного биполярного транзистора, база которого соединена со вторым 2, 2* входом устройства, второй 11, 11* согласующий биполярный транзистор, коллектор которого соединен с его базой и подключен к базе второго 12, 12* выходного биполярного транзистора, а также первый 14, 14* и второй 15, 15* дополнительные биполярные транзисторы, причем база первого 14, 14* дополнительного биполярного транзистора соединена с первым 1, 1* входом устройства, а эмиттер соединен с эмиттером второго 11, 11* согласующего биполярного транзистора, база второго 15, 15* дополнительного биполярного транзистора соединена со вторым 2, 2* входом устройства, коллектор подключен к дополнительному 16, 16* токовому выходу, а эмиттер соединен с эмиттером второго 12, 12* выходного биполярного транзистора, при этом в первом ДК1 первый 3 входной, второй 10 входной, первый 14 и второй 15 дополнительные биполярные транзисторы имеют p-n-p структуру, а первый 5 выходной, первый 7 и второй 11 согласующие, второй 12 выходной биполярные транзисторы имеют n-p-n структуру, причем во втором ДК2 первый 3* входной, второй 10* входной, первый 14* и второй 15* дополнительные биполярные транзисторы имеют n-p-n структуру, а первый 5* выходной, первый 7* и второй 11* согласующие, второй 12* выходной биполярные транзисторы имеют p-n-p структуру, а во втором ДК2 дополнительный 16* токовый выход согласован со второй 8 шиной источника питания, коллектор первого 7* согласующего биполярного транзистора соединен с первой 4 шиной источника питания через первый 9* источник опорного тока, коллектор второго 11* согласующего биполярного транзистора соединен с первой 4 шиной источника питания через второй 13* источник опорного тока, коллекторы первого 3* входного биполярного транзистора, первого 14* дополнительного биполярного транзистора и второго 10* входного биполярного транзистора связаны со второй 8 шиной источника питания, причем первая 4 шина источника питания обеспечивает отрицательное напряжение, а вторая 8 шина источника питания обеспечивает положительное напряжение, при этом первый 1 вход первого ДК1 соединен с первым 1* входом второго ДК2, второй 2 вход первого ДК1 соединен со вторым 2* входом второго ДК2, а первый 6 основной токовый выход устройства соединен с дополнительным 16* токовым выходом второго ДК2, а дополнительный 16 токовый выход первого ДК1 соединен со вторым 6* основным токовым выходом устройства.

В схемах фиг. 5 и фиг. 6 используется два токовых зеркала 17 и 18, согласованные соответственно с первой 4 и второй 8 шинами источников питания, а также интегрирующий корректирующий конденсатора 19, обеспечивающий устойчивость ОУ, выходной буферный усилитель 20, выход которого 21 является потенциальным выходом ОУ.

Рассмотрим работу предлагаемого входного дифференциального каскада на чертеже фиг. 2 со схемой его включения в ОУ на чертежах фиг. 5 и фиг. 6.

Максимальная скорость нарастания выходного напряжения классических ОУ с трехкаскадной архитектурой (фиг. 5) для режима большого сигнала может быть получена только в том случае, если входной дифференциальный каскад ОУ обеспечивает безынерционную передачу импульсного приращения входного напряжения u1(+) на инвертирующем входе Вх.1(-) на вход безынерционного токового зеркала 17, причем этот максимальный выходной ток ДК должен значительно превышать статический ток данного выхода. То есть входной ДК должен работать в режиме класса АВ.

Аналогичное требование накладывается и на второй вход Вх.2(+) дифференциального каскада, который также должен работать в режиме класса АВ относительно выхода 6* (Вых.i2.1).

Высокое быстродействие в схеме ОУ фиг. 5 с предлагаемым входным каскадом для его неинвертирующего включения будет реализовано в том случае, если импульсное приращение напряжения u2(+) на неинвертирующем входе Вх.2(+) будет передаваться (без существенных задержек и ограничений на проходной характеристике) на соответствующие входы токовых зеркал 17-18 через дополнительные токовые выходы 16* и 16 первого ДК1 и второго ДК2. Важно отметить, в рассматриваемой структуре ОУ на чертеже фиг. 5 другие инерционности схем ДК1 и ДК2 на чертежах фиг. 3 и фиг. 4 в каналах передачи сигналов со входов Вх.1(-) и Вх.2(+) (наличие паразитных емкостей Ср9, Ср13, Ср9*, Ср13*) не оказывают существенного влияния на SR. Это позволяет выполнять ОУ фиг. 5 с заявляемым входным дифференциальным каскадом по классическим кремниевым технологическим процессам, имеющим сравнительно большие микронные топологические нормы и тем не менее получить SR в диапазоне 800-850 В/мкс.

Предлагаемый входной дифференциальный каскад (фиг. 2) имеет только два «качественных» (с точки зрения увеличения SR) токовых выхода - выход 6 (Вых.i1.1) и дополнительный выход 16 (Вых.i1.2), а также токовый выход 6* (Вых.i2.1) и дополнительный токовый выход 16* (Вых.i2.2), которые обеспечивают во время фронта переходного процесса большие импульсные выходные токи (с минимальной задержкой по времени). Соединение «хороших» токовых выходов в ДК фиг. 2, как это сделано на чертеже фиг. 5, создает основу для проектирования на микронных техпроцессах быстродействующих ОУ с малым статическим токопотреблением.

Замечательная особенность предлагаемых схемотехнических решений состоит в том, что они обеспечивают повышение SR как в неинвертирующем, так и в инвертирующем включениях ОУ.

Компьютерное моделирование ОУ фиг. 7 в неинвертирующем включении с предлагаемым входным каскадом фиг. 2 показывает (фиг. 9, фиг. 10), что максимальная скорость нарастания выходного напряжения SR(+) ОУ фиг. 7 для переднего фронта 811,008 В/мкс, а SR(-) для заднего

фронта 1156,74 В/мкс, что значительно лучше, чем SR в ОУ с дифференциальным каскадом-прототипом (20 В/мкс).

Для инвертирующего включения ОУ фиг. 11 максимальная скорость нарастания выходного напряжения SR(+) (фиг. 12, фиг. 13) для переднего фронта 825,932 В/мкс, а SR(-) для заднего фронта 841,053 В/мкс.

Таким образом, выполненное компьютерное моделирование показывает, что заявляемое устройства имеет существенные преимущества в сравнении с прототипом по уровню максимальной скорости нарастания выходного напряжения при его использовании в структуре классических операционных усилителей с двумя токовыми зеркалами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Naderi M. H., Prakash S., Silva-Martinez J. Operational transconductance amplifier with class-B slew-rate boosting for fast high-performance switched-capacitor circuits //IEEE Transactions on Circuits and Systems I: Regular Papers. - 2018. - Т. 65. - №. 11. - С. 3769-3779.

2. Матавкин В. Быстродействующие операционные усилители. - М: Радио и связь, 1989. - С. 91, рис. 5.18.

3. Операционный усилитель HA2700. Справочник Harris Semiconductor “Linear& Data Acquisition Products”, volume 1, стр. 2-59 (http://www.bitsavers.org/components/harris/1977_Harris_Linear_and_Data_Acquisition_Products_Volume_1.pdf).

4. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография, серия «Библиотека студента» / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. - М.: СОЛОН-Пресс, 2021. - 200 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий дифференциальный операционный усилитель на комплементарных биполярных транзисторах | 2024 |

|

RU2827743C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Быстродействующий операционный усилитель | 2024 |

|

RU2822112C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797043C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2616573C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786507C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

Изобретение относится к радиоэлектронике и может быть использовано в структуре операционных усилителей (ОУ). Технический результат: обеспечение повышения уровня скорости нарастания выходного напряжения (SR) при использовании классических (не СВЧ) кремниевых технологических процессов. Такой результат обеспечивается за счет того, что входной дифференциальный каскад ОУ состоит из двух дифференциальных каскадов ДК1 и ДК2, каждый из которых состоит из шести биполярных транзисторов и двух источников напряжения, при этом в ДК1 первый (3) входной, второй (10) выходной, первый (14) и второй (15) дополнительные биполярные транзисторы имеют n-p-n структуру, а первый (5) выходной, первый (7) и второй (11) согласующие, второй (12) выходной биполярные транзисторы имеют p-n-p структуру, а в ДК2 первый (3*) входной, второй (10*) выходной, первый (14*) и второй (15*) дополнительные биполярные транзисторы имеют p-n-p структуру, а первый (5*) выходной, первый (7*) и второй (11*) согласующие, второй (12*) выходной биполярные транзисторы имеют n-p-n структуру. 13 ил.

Входной дифференциальный каскад быстродействующего операционного усилителя, содержащий первый дифференциальный каскад (ДК1), включающий первый (1) и второй (2) входы устройства, первый (3) входной биполярный транзистор, база которого подключена к первому (1) входу устройства, коллектор связан с первой (4) шиной источника питания, а эмиттер соединен с эмиттером первого (5) выходного биполярного транзистора, коллектор первого (5) выходного биполярного транзистора связан с первым (6) основным токовым выходом устройства, согласованным со второй (8) шиной источника питания, база первого (5) выходного биполярного транзистора соединена с коллектором и базой первого (7) согласующего биполярного транзистора и связана со второй (8) шиной источника питания через первый (9) источник опорного тока, эмиттер первого (7) согласующего биполярного транзистора соединен с эмиттером второго (10) входного биполярного транзистора, коллектор которого связан с первой (4) шиной источника питания, а база соединена со вторым (2) входом устройства, второй (11) согласующий биполярный транзистор, коллектор которого соединен с его базой и подключен к базе второго (12) выходного биполярного транзистора и через второй (13) источник опорного тока соединен со второй (8) шиной источника питания, отличающийся тем, что первый дифференциальный каскад (ДК1) дополнительно включает первый (14) и второй (15) дополнительные биполярные транзисторы, причем база первого (14) дополнительного биполярного транзистора соединена с первым (1) входом устройства, коллектор подключен к первой (4) шине источника питания, а эмиттер соединен с эмиттером второго (11) согласующего биполярного транзистора, база второго (15) дополнительного биполярного транзистора соединена со вторым (2) входом устройства, коллектор подключен к дополнительному (16) токовому выходу ДК1, согласованному с первой (4) шиной источника питания, а эмиттер соединен с эмиттером второго (12) выходного биполярного транзистора, коллектор второго (12) выходного транзистора связан со второй (8) шиной источника питания, причем заявляемое устройство состоит из первого (ДК1) и второго (ДК2) дифференциальных каскадов, каждый из которых содержит первый (1, 1*) и второй входы (2, 2*) устройства, первый (3, 3*) входной биполярный транзистор, база которого подключена к первому (1, 1*) входу устройства, а эмиттер соединен с эмиттером первого (5, 5*) выходного биполярного транзистора, коллектор первого (5, 5*) выходного биполярного транзистора связан с основным (первым (6) и вторым (6*)) токовым выходом устройства, база первого (5, 5*) выходного биполярного транзистора соединена с коллектором и базой первого (7, 7*) согласующего биполярного транзистора, эмиттер первого (7, 7*) согласующего биполярного транзистора соединен с эмиттером второго (10, 10*) входного биполярного транзистора, база которого соединена со вторым (2, 2*) входом устройства, второй (11, 11*) согласующий биполярный транзистор, коллектор которого соединен с его базой и подключен к базе второго (12, 12*) выходного биполярного транзистора, а также первый (14, 14*) и второй (15, 15*) дополнительные биполярные транзисторы, причем база первого (14, 14*) дополнительного биполярного транзистора соединена с первым (1, 1*) входом устройства, а эмиттер соединен с эмиттером второго (11, 11*) согласующего биполярного транзистора, база второго (15, 15*) дополнительного биполярного транзистора соединена со вторым (2, 2*) входом устройства, коллектор подключен к дополнительному (16, 16*) токовому выходу, а эмиттер соединен с эмиттером второго (12, 12*) выходного биполярного транзистора, при этом в первом ДК1 первый (3) входной, второй (10) входной, первый (14) и второй (15) дополнительные биполярные транзисторы имеют p-n-p структуру, а первый (5) выходной, первый (7) и второй (11) согласующие, второй (12) выходной биполярные транзисторы имеют n-p-n структуру, причем во втором ДК2 первый (3*) входной, второй (10*) входной, первый (14*) и второй (15*) дополнительные биполярные транзисторы имеют n-p-n структуру, а первый (5*) выходной, первый (7*) и второй (11*) согласующие, второй (12*) выходной биполярные транзисторы имеют p-n-p структуру, а во втором ДК2 дополнительный (16*) токовый выход согласован со второй (8) шиной источника питания, коллектор первого (7*) согласующего биполярного транзистора соединен с первой (4) шиной источника питания через первый (9*) источник опорного тока, коллектор второго (11*) согласующего биполярного транзистора соединен с первой (4) шиной источника питания через второй (13*) источник опорного тока, коллекторы первого (3*) входного биполярного транзистора, первого (14*) дополнительного биполярного транзистора и второго (10*) входного биполярного транзистора связаны со второй (8) шиной источника питания, причем первая (4) шина источника питания обеспечивает отрицательное напряжение, а вторая (8) шина источника питания обеспечивает положительное напряжение, при этом первый (1) вход первого ДК1 соединен с первым (1*) входом второго ДК2, второй (2) вход первого ДК1 соединен со вторым (2*) входом второго ДК2, а первый (6) основной токовый выход устройства соединен с дополнительным (16*) токовым выходом второго ДК2, а дополнительный (16) токовый выход первого ДК1 соединен со вторым (6*) основным токовым выходом устройства.

| КАСКОДНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797566C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797043C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С «ПЕРЕГНУТЫМ» КАСКОДОМ КЛАССА АВ | 2022 |

|

RU2786512C1 |

| US 20040232968 A1, 25.11.2004 | |||

| US 6429744 B2, 06.08.2002. | |||

Авторы

Даты

2024-09-16—Публикация

2024-02-01—Подача