Предполагаемое изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах (активных RC-фильтрах, нормирующих преобразователях и т.п.), работающих в условиях низких температур и воздействия радиации.

В современной микроэлектронике достаточно перспективны архитектуры ОУ, содержащие так называемый «плавающий» входной дифференциальный каскад [1], который реализуется как по JFET [2-6], так и по CJFET технологиям [7-9] и не содержит классических источников опорного тока для установления статического режима входных транзисторов.

Ближайшим прототипом заявляемого устройства является операционный усилитель [1] с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом, представленный в статье фирмы Linear Integrated System (микросхемы LSK489/LSJ689; Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17.). Он содержит первый 1 и второй 2 входы устройства, выход 3 устройства, связанный с выходом буферного усилителя 4, первый 5, второй 6, третий 7 и четвертый 8 входные полевые транзисторы, образующие «плавающий» входной дифференциальный каскад с элементом стабилизации статического режима 9 входных полевых транзисторов, причем затворы первого 5 и третьего 7 входных полевых транзисторов подключены ко входу 1 устройства, а затворы второго 6 и четвертого 8 входных полевых транзисторов соединены со входом 2 устройства, первый 10 и второй 11 выходные полевые транзисторы, затворы которых подключены соответственно к первому 12 и второму 13 вспомогательным источникам напряжения, стоки объединены и подключены ко входу буферного усилителя 4, причем исток первого 10 выходного полевого транзистора соединен со стоком второго 6 входного полевого транзистора и связан с первой 14 шиной источника питания через первый 15 токостабилизирующий элемент, а исток второго 11 выходного полевого транзистора подключен к стоку четвертого 8 входного полевого транзистора и связан со второй 16 шиной источника питания через второй 17 токостабилизирующий элемент, кроме этого сток первого 5 входного полевого транзистора согласован с первой 14 шиной источника питания, а сток третьего 7 входного полевого транзистора согласован со второй 16 шиной источника питания.

Существенный недостаток ОУ-прототипа состоит в том, что в нем не обеспечиваются малые значения систематической составляющей напряжения смещения нуля (Uсм), а также повышенные значения коэффициента усиления по напряжению (К0) и коэффициента ослабления входного синфазного сигнала (Кос.сф).

Основная задача предполагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного JFet операционного усилителя, который обеспечивает малый уровень систематической составляющей напряжения смещения нуля, а также повышенные значения коэффициента усиления по напряжению и коэффициента ослабления входных синфазных сигналов.

Поставленная задача достигается тем, что в ОУ фиг. 1, содержащем первый 1 и второй 2 входы устройства, выход 3 устройства, связанный с выходом буферного усилителя 4, первый 5, второй 6, третий 7 и четвертый 8 входные полевые транзисторы (далее – полевые транзисторы с управляющим p-n переходом), образующие «плавающий» входной дифференциальный каскад с элементом стабилизации статического режима 9 входных полевых транзисторов, причем затворы первого 5 и третьего 7 входных полевых транзисторов подключены ко входу 1 устройства, а затворы второго 6 и четвертого 8 входных полевых транзисторов соединены со входом 2 устройства, первый 10 и второй 11 выходные полевые транзисторы, затворы которых подключены соответственно к первому 12 и второму 13 вспомогательным источникам напряжения, стоки объединены и подключены ко входу буферного усилителя 4, причем исток первого 10 выходного полевого транзистора соединен со стоком второго 6 входного полевого транзистора и связан с первой 14 шиной источника питания через первый 15 токостабилизирующий элемент, а исток второго 11 выходного полевого транзистора подключен к стоку четвертого 8 входного полевого транзистора и связан со второй 16 шиной источника питания через второй 17 токостабилизирующий элемент, кроме этого сток первого 5 входного полевого транзистора согласован с первой 14 шиной источника питания, а сток третьего 7 входного полевого транзистора согласован со второй 16 шиной источника питания, предусмотрены новые элементы и связи – между объединенными истоками первого 5 и второго 6 входных полевых транзисторов и объединенными истоками третьего 7 и четвертого 8 входных полевых транзисторов включен элемент стабилизации статического режима 9 входных полевых транзисторов на основе первого 18 дополнительного полевого транзистора и первого 19 дополнительного резистора, причем сток первого 18 дополнительного полевого транзистора подключен к объединенным истокам первого 5 и второго 6 входных полевых транзисторов, затвор первого 18 дополнительного полевого транзистора соединен с объединенными истоками третьего 7 и четвертого 8 входных полевых транзисторов, а исток первого 18 дополнительного полевого транзистора связан с объединенными истоками третьего 7 и четвертого 8 входных полевых транзисторов через первый 19 дополнительный резистор, первый 15 токостабилизирующий элемент выполнен на основе второго 20 дополнительного полевого транзистора и второго 21 дополнительного резистора, причем сток второго 20 дополнительного полевого транзистора подключен к первой 14 шине источника питания, затвор второго 20 дополнительного полевого транзистора соединен с истоком первого 10 выходного полевого транзистора, а исток второго 20 дополнительного полевого транзистора соединен с истоком первого 10 выходного полевого транзистора через второй 21 дополнительный резистор, второй 17 токостабилизирующий элемент выполнен на основе третьего 22 дополнительного полевого транзистора и третьего 23 дополнительного резистора, причем сток третьего 22 дополнительного полевого транзистора соединен с истоком второго 11 выходного полевого транзистора, затвор второго 20 дополнительного полевого транзистора подключен ко второй 16 шине источника питания, а исток третьего 22 дополнительного полевого транзистора связан со второй 16 шиной источника питания через третий 23 дополнительный резистор.

На чертеже фиг. 1 представлена схема ОУ-прототипа, опубликованного в [1], а на чертеже фиг. 2 – схема заявляемого ОУ в соответствии с п. 1 и п. 2 формулы изобретения.

На чертеже фиг. 3 показана схема заявляемого ОУ фиг. 2 в соответствии с п. 3 и п. 4 формулы изобретения.

На чертеже фиг. 4 приведена схема заявляемого ОУ фиг. 2 в среде LTSpice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск) при

t=-197°С, R1=R2=R3=10кОм, V3=V4=3В, V5=3.7В, V6=3.5В.

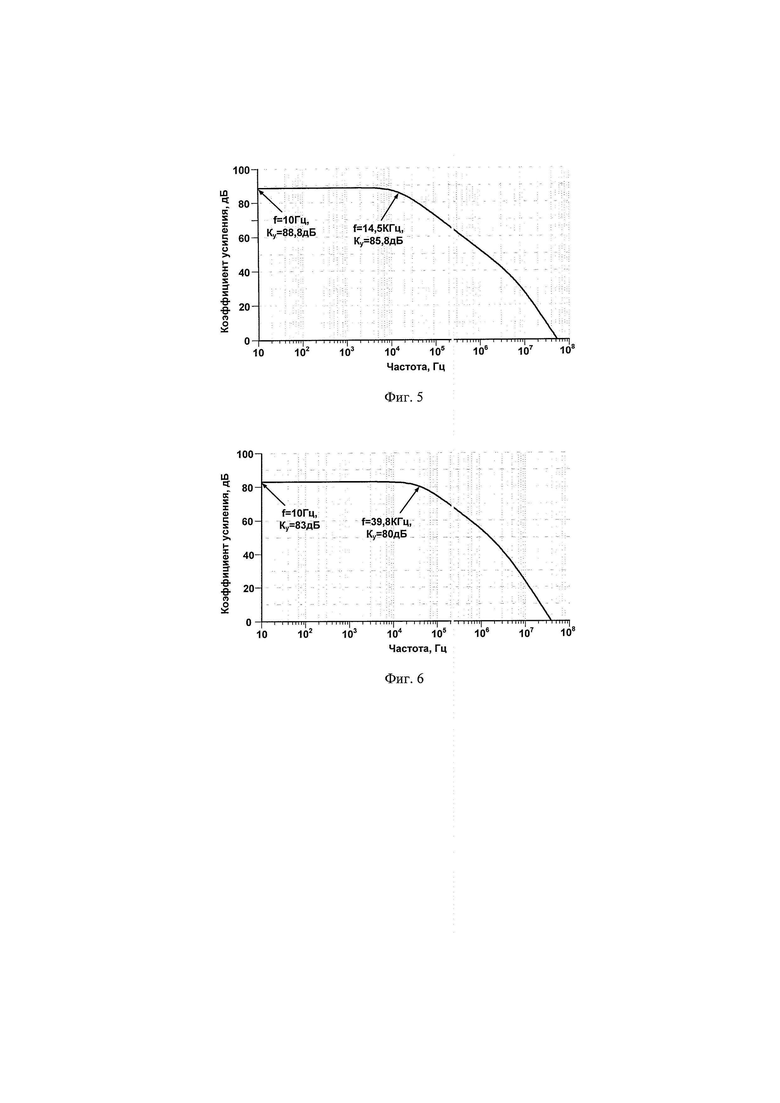

На чертеже фиг. 5 показаны амплитудно-частотные характеристики ОУ фиг. 4 при t=27°С.

На чертеже фиг. 6 представлены амплитудно-частотные характеристики ОУ фиг. 4 при t=-197°С.

На чертеже фиг. 7 приведена схема заявляемого ОУ фиг. 3, оптимизированного для температуры t=27 °С, при температуре моделирования t=27 °С, R1÷R5=4 кОм, V1=1.66, V2=2.14 В, в среде LTSpice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск).

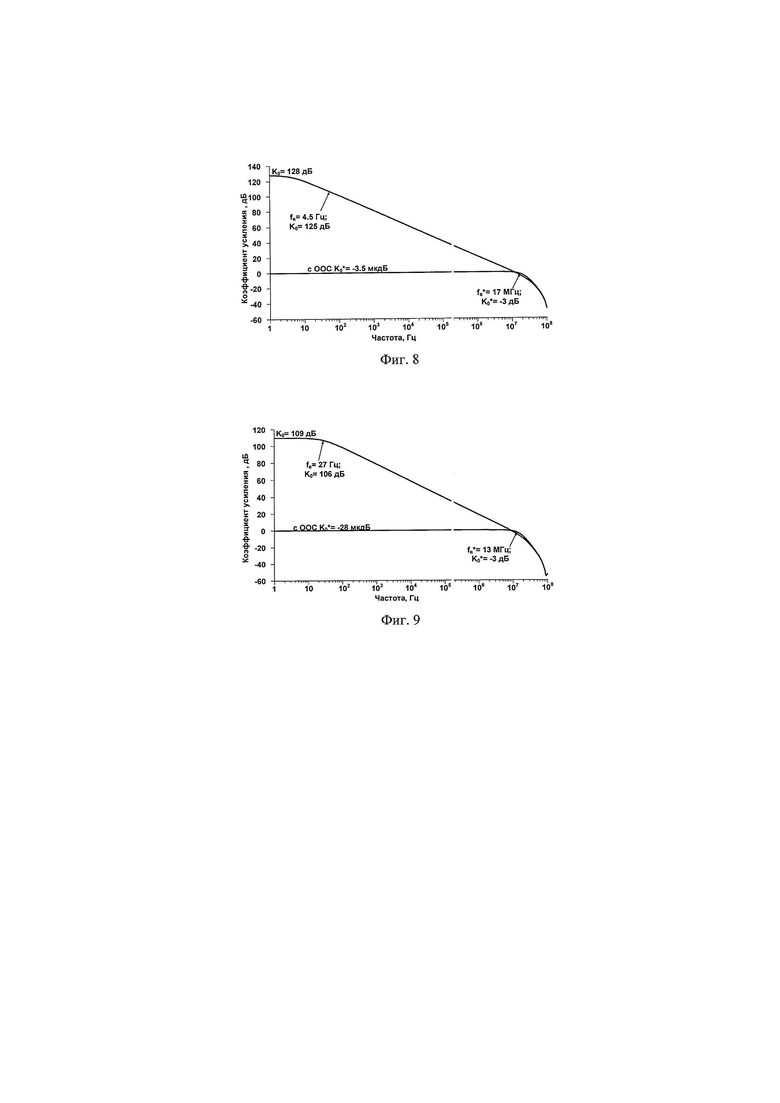

На чертеже фиг. 8 показаны амплитудно-частотные характеристики ОУ фиг. 7 при t=27 °С, R1÷R5=4 кОм, V1=1.66, V2=2.14 В, С1=10 пФ.

На чертеже фиг. 9 представлены амплитудно-частотные характеристики ОУ фиг. 7, оптимизированного для температуры t=27 °С при температуре моделирования t=-197°С, R1÷R5=4 кОм, V1=1.66, V2=2.14 В, С1=10 пФ.

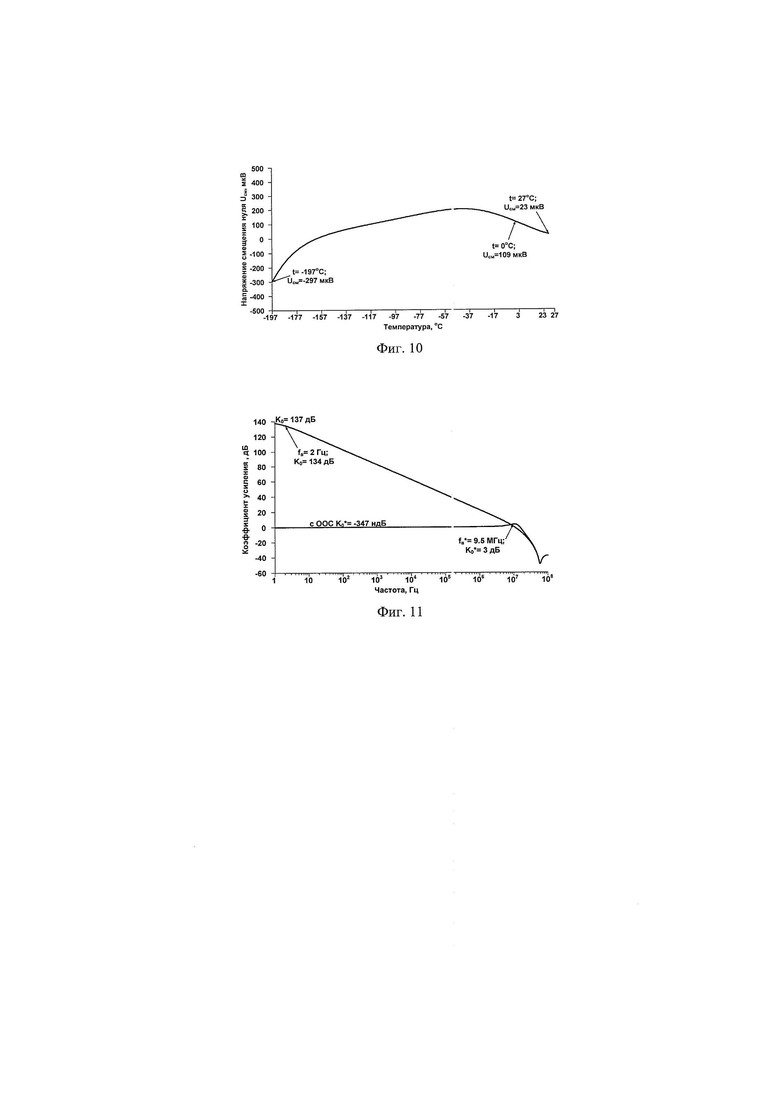

На чертеже фиг. 10 приведена зависимость систематической составляющей напряжения смещения нуля Uсм от температуры JFet ОУ фиг. 7, оптимизированного для температуры t=27°С при R1÷R5=4 кОм, V1=1.66, V2=2.14 В, С1=10 пФ.

На чертеже фиг. 11 показаны амплитудно-частотные характеристики ОУ фиг. 7, при t=27 °С, R1÷R5=20 кОм, V1=1.34, V2=1.26 В, С1=5 пФ.

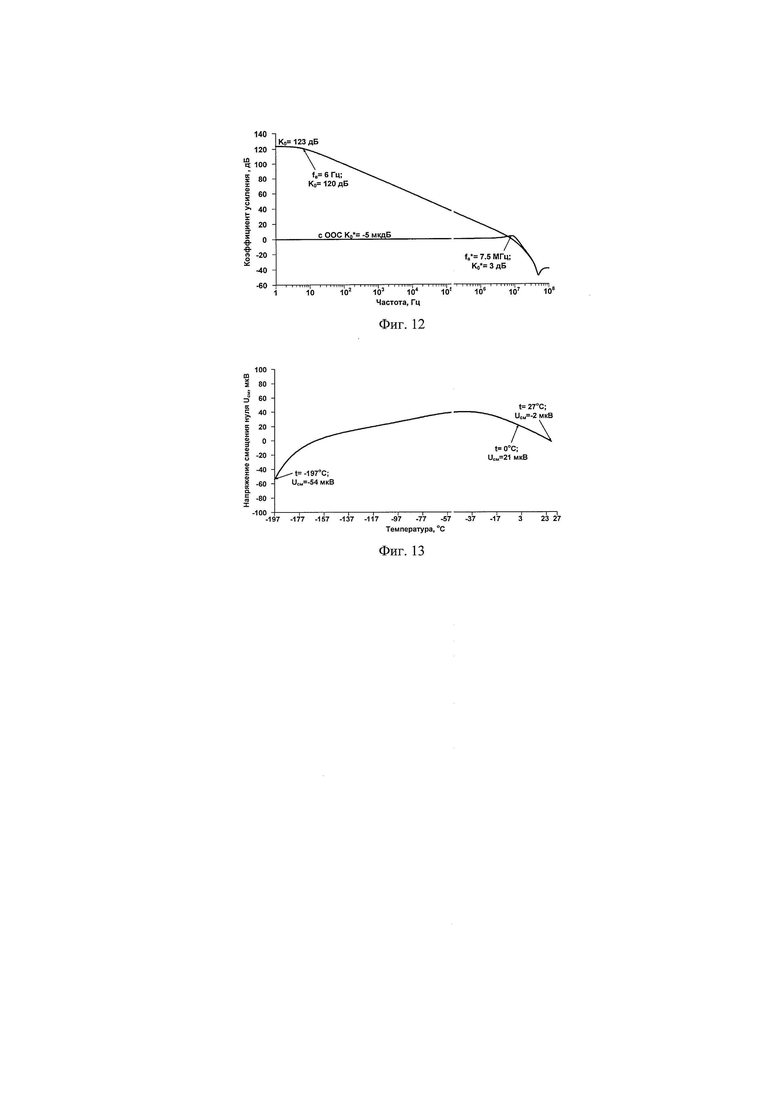

На чертеже фиг. 12 показаны амплитудно-частотные характеристики ОУ фиг. 7, при температуре моделирования t=-197 °С, R1÷R5=20 кОм, V1=1.34, V2=1.26 В, С1=5 пФ.

На чертеже фиг. 13 представлена зависимость систематической составляющей напряжения смещения нуля Uсм от температуры JFet ОУ фиг. 7, оптимизированного для температуры t=27 °С при R1÷R5=20 кОм, V1=1.34, V2=1.26 В, С1=5 пФ.

Операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 входы устройства, выход 3 устройства, связанный с выходом буферного усилителя 4, первый 5, второй 6, третий 7 и четвертый 8 входные полевые транзисторы, образующие «плавающий» входной дифференциальный каскад с элементом стабилизации статического режима 9 входных полевых транзисторов, причем затворы первого 5 и третьего 7 входных полевых транзисторов подключены ко входу 1 устройства, а затворы второго 6 и четвертого 8 входных полевых транзисторов соединены со входом 2 устройства, первый 10 и второй 11 выходные полевые транзисторы, затворы которых подключены соответственно к первому 12 и второму 13 вспомогательным источникам напряжения, стоки объединены и подключены ко входу буферного усилителя 4, причем исток первого 10 выходного полевого транзистора соединен со стоком второго 6 входного полевого транзистора и связан с первой 14 шиной источника питания через первый 15 токостабилизирующий элемент, а исток второго 11 выходного полевого транзистора подключен к стоку четвертого 8 входного полевого транзистора и связан со второй 16 шиной источника питания через второй 17 токостабилизирующий элемент, кроме этого сток первого 5 входного полевого транзистора согласован с первой 14 шиной источника питания, а сток третьего 7 входного полевого транзистора согласован со второй 16 шиной источника питания. Между объединенными истоками первого 5 и второго 6 входных полевых транзисторов и объединенными истоками третьего 7 и четвертого 8 входных полевых транзисторов включен элемент стабилизации статического режима 9 входных полевых транзисторов на основе первого 18 дополнительного полевого транзистора и первого 19 дополнительного резистора, причем сток первого 18 дополнительного полевого транзистора подключен к объединенным истокам первого 5 и второго 6 входных полевых транзисторов, затвор первого 18 дополнительного полевого транзистора соединен с объединенными истоками третьего 7 и четвертого 8 входных полевых транзисторов, а исток первого 18 дополнительного полевого транзистора связан с объединенными истоками третьего 7 и четвертого 8 входных полевых транзисторов через первый 19 дополнительный резистор, первый 15 токостабилизирующий элемент выполнен на основе второго 20 дополнительного полевого транзистора и второго 21 дополнительного резистора, причем сток второго 20 дополнительного полевого транзистора подключен к первой 14 шине источника питания, затвор второго 20 дополнительного полевого транзистора соединен с истоком первого 10 выходного полевого транзистора, а исток второго 20 дополнительного полевого транзистора соединен с истоком первого 10 выходного полевого транзистора через второй 21 дополнительный резистор, второй 17 токостабилизирующий элемент выполнен на основе третьего 22 дополнительного полевого транзистора и третьего 23 дополнительного резистора, причем сток третьего 22 дополнительного полевого транзистора соединен с истоком второго 11 выходного полевого транзистора, затвор второго 20 дополнительного полевого транзистора подключен ко второй 16 шине источника питания, а исток третьего 22 дополнительного полевого транзистора связан со второй 16 шиной источника питания через третий 23 дополнительный резистор.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, сток первого 5 входного полевого транзистора связан с первой 14 шиной источника питания через первую 24 цепь согласования потенциалов, а исток третьего 7 входного полевого транзистора связан со второй 16 шиной источника питания через вторую 25 цепь согласования потенциалов.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, первый 10 выходной полевой транзистор выполнен по каскодной схеме и содержит первый 26 и второй 27 вспомогательные полевые транзисторы, причем затвор первого 26 вспомогательного полевого транзистора подключен к первому 12 вспомогательному источнику напряжения, а его исток соединен со стоком второго 6 входного полевого транзистора и затвором второго 27 вспомогательного полевого транзистора, сток первого 26 вспомогательного полевого транзистора подключен к истоку второго 27 вспомогательного полевого транзистора, сток которого связан со входом буферного усилителя 4, второй 11 выходной полевой транзистор выполнен по каскодной схеме и содержит третий 28 и четвертый 29 вспомогательные полевые транзисторы, причем затвор третьего 28 вспомогательного полевого транзистора подключен ко второму 13 вспомогательному источнику напряжения, а его исток соединен со стоком четвертого 8 входного полевого транзистора и затвором четвертого 29 вспомогательного полевого транзистора, сток третьего 28 вспомогательного полевого транзистора подключен к истоку четвертого 29 вспомогательного полевого транзистора, сток которого связан со входом буферного усилителя 4.

Кроме того, на чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, первая 24 цепь согласования потенциалов (Е01) содержит первый 30 и второй 31 согласующие полевые транзисторы, причем сток первого 30 согласующего полевого транзистора подключен к первой 14 шиной источника питания, затвор первого 30 согласующего полевого транзистора соединен со стоком первого 5 входного полевого транзистора и истоком второго 31 согласующего полевого транзистора, исток первого 30 согласующего полевого транзистора связан с истоком второго 31 согласующего полевого транзистора через первый 32 согласующий резистор, а затвор второго 31 согласующего полевого транзистора подключен к первому 12 вспомогательному источнику напряжения (Ес12), вторая 25 цепь согласования потенциалов содержит третий 33 и четвертый 34 согласующие полевые транзисторы, причем исток третьего 33 согласующего полевого транзистора соединен со стоком третьего 7 входного полевого транзистора и подключен к стоку четвертого 34 согласующего полевого транзистора, затвор третьего 33 согласующего полевого транзистора соединён со вторым 13 вспомогательным источником напряжения (Ес13), затвор четвертого 34 согласующего полевого транзистора подключен ко второй 16 шине источника питания, а его исток связан со второй 16 шиной источника питания через второй 35 согласующий резистор, кроме этого стоки второго 31 и третьего 33 согласующих полевые транзисторы подключены к общей шине источника питания 36.

На чертежах фиг. 1 - фиг. 3 конденсатор Ск обеспечивает коррекцию амплитудно-частотной характеристики ОУ.

Рассмотрим работу предлагаемого ОУ фиг. 2 в сравнении с ОУ-прототипом фиг. 1.

Для достижения заявляемого эффекта в схеме фиг. 2 предусмотрено применение специального элемента стабилизации статического режима 9 «плавающего» входного дифференциального каскада на первом 18 дополнительном полевом транзисторе и первом 19 дополнительном резисторе, а также реализация первого 15 и второго 17 токостабилизирующих элементов на идентичных первому 18 JFET на дополнительных втором 20 и третьем 22 полевых транзисторах, работающих таки же идентичных статических напряжениях между затвором и истоком. Данные режимы устанавливаются за счет оптимального выбора первого 12 и второго 13 вспомогательных источников напряжения, которые из-за разных напряжений отсечки первого 10 и второго 11 выходных полевых транзисторов с p- и n- каналами соответственно, должны быть неодинаковыми (Eс12≠Eс13). Таким образом, в заявляемой схеме фиг. 2 реализуется высокая идентичность токов в элементе стабилизации статического режима 9 «плавающего» входного дифференциального каскада, а также токов первого 15 и второго 17 токостабилизирующих элементов. Это является важным условием получения малых значений систематической составляющей напряжения смещения нуля (Uсм) ОУ. Данный вывод подтверждается результатами компьютерного моделирования на чертеже фиг.10, который показывает, что Uсм в заявляемой модификации ОУ лежит в диапазоне десятков микровольт, что недостижимо в ОУ-прототипе фиг. 1 без технологической балансировки Uсм.

Кроме этого, реализация первого 15 и второго 17 токостабилизирующих элементов на одинаковых втором 20 и третьем 22 дополнительных полевых транзисторах существенно повышает коэффициент усиления (К0) по напряжению ОУ фиг.2, так как

, (1)

, (1)

где RΣ1– эквивалентное сопротивление высокоимпедансного узла Σ1,  – эквивалентная крутизна преобразования входного дифференциального напряжения uвх ОУ фиг.2 в выходной ток iΣ1 высокоимпендасного узла Σ1:

– эквивалентная крутизна преобразования входного дифференциального напряжения uвх ОУ фиг.2 в выходной ток iΣ1 высокоимпендасного узла Σ1:

(2)

(2)

Причем проводимость, обратная сопротивлению RΣ1 определяется формулой:

, (3)

, (3)

, (4)

, (4)

, (5)

, (5)

, (6)

, (6)

, (7)

, (7)

, (8)

, (8)

. (9)

. (9)

В формулах (4)÷(9) принято, что параметр μi – это коэффициент внутренней обратной связи JFet транзисторов, характеризующий влияние изменений напряжения сток-затвор на напряжение затвор-исток (эффект модуляции длинны канала) при постоянном токе истока.

Из последних уравнений (3)÷(9) следует, что в предлагаемой схеме ОУ коэффициент К0 существенно возрастает за счет увеличения второго сомножителя в формуле (1) – эквивалентного сопротивления RΣ1. Данный вывод подтверждается результатами моделирования на чертеже фиг.11, который показывает, что заявляемый ОУ, имеющий один высокоимпедансный узел Σ1, характеризуется экстремально высокими значениями К0=123÷137 дБ, что достаточно для многих применений.

Дальнейшая минимизация основных составляющих Uсм ОУ фиг.2 связана с введением первой 24 и второй 25 цепей согласования потенциалов, которые предназначены для симметрирования статических напряжений затвор-исток первого 5 и второго 6 входных полевых транзисторов, а так же соответственно третьего 7 и четвертого 8 входных полевых транзисторов. Данное схемотехническое решение позволяет уменьшить влияние эффекта модуляции длины канала первого 5 и второго 6 входных полевых транзисторов (третьего 7 и четвертого 8 входных полевых транзисторов) на смещение их стоко-затворных характеристик и, в конечном итоге, уменьшает вторую составляющую Uсм, обусловленную влиянием коэффициента внутренней обратной связи μ. Причем, в предлагаемых схемах ОУ, из-за разных напряжений затвор-исток JFet с p-каналом (первый 10 выходной полевой транзистор) и n-каналом (второй 11 выходной полевой транзистор) должно соблюдаться неравенство Eс12≠ Eс13.

Предлагаемый в соответствии с п.3 формулы изобретения схемотехнический прием (конкретное выполнение первой 24 и второй 25 цепей согласования потенциалов) обеспечивает «автоматическое» симметрирование статических режимов первого 5 и второго 6 входных полевых транзисторов, (а также третьего 7 и четвертого 8 входных полевых транзисторов) по напряжению затвор-сток в широком диапазоне температур и радиационных воздействий. Поэтому данную схему следует использовать для получения экстремально малых значений Uсм в тяжелых условиях эксплуатации ОУ.

На дальнейшее повышение коэффициента усиления по напряжению ОУ фиг.3 направлен п.4 формулы изобретения, при котором обеспечивается К0 порядка 120÷137 дБ (от одного миллиона до десятков миллионов). Это позволяет создавать на основе заявляемого ОУ, усиление которого, формируется только одним каскадом («перегнутым» каскодом, обладающим широкой полосой пропускания и расширенным диапазоном изменения выходного напряжения) различные частные варианты построения аналоговых устройств.

Таким образом, заявляемое устройство имеет (в сравнении с ОУ-прототипом [1] на известных серийных микросхемах LSJ689, LSK489 фирмы Linear Integrated Systems, США [10,11]) более высокие обобщенные показатели качества: улучшенные Uсм, К0, и

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17. URL: http://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluation_Board.pdf

2. RU 2523124, 2013 г.

3. RU 2615066, 2015 г.

4. RU 2517699, 2012 г.

5. RU 2621287, 2017 г.

6. RU 2627094, 2017 г.

7. RU 2684473, 2019 г.

8. RU 2679970, 2019 г.

9. RU 2712414, 2019 г.

10. Bob Cordell, "Linear Systems LSJ689 Application Note", URL: http://www.linearsystems.com/lsdata/appnotes/LSJ689_P-Channel%20Dual%20JFETs.pdf

11.Bob Cordell, "LSK489 Application Note", URL: http://www.linearsystems.com/lsdata/others/LSK489_Application_Note.pdf.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРСЕНИД-ГАЛЛИЕВЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784666C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770916C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2739577C1 |

Предполагаемое изобретение относится к области радиотехники. Технический результат: создание радиационно-стойкого и низкотемпературного JFet операционного усилителя. Для этого предложен операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом, в котором в отличие от прототипа между объединенными истоками первого (5) и второго (6) входных полевых транзисторов и объединенными истоками третьего (7) и четвертого (8) входных полевых транзисторов включен элемент стабилизации статического режима (9) входных полевых транзисторов на основе первого (18) дополнительного полевого транзистора и первого (19) дополнительного резистора, причем сток первого (18) дополнительного полевого транзистора подключен к объединенным истокам первого (5) и второго (6) входных полевых транзисторов, затвор первого (18) дополнительного полевого транзистора соединен с объединенными истоками третьего (7) и четвертого (8) входных полевых транзисторов, а также предложены другие элементы и связи. 3 з.п. ф-лы, 13 ил.

1. Операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом, содержащий первый (1) и второй (2) входы устройства, выход (3) устройства, связанный с выходом буферного усилителя (4), первый (5), второй (6), третий (7) и четвертый (8) входные полевые транзисторы, образующие «плавающий» входной дифференциальный каскад с элементом стабилизации статического режима (9) входных полевых транзисторов, причем затворы первого (5) и третьего (7) входных полевых транзисторов подключены к входу (1) устройства, а затворы второго (6) и четвертого (8) входных полевых транзисторов соединены со входом (2) устройства, первый (10) и второй (11) выходные полевые транзисторы, затворы которых подключены соответственно к первому (12) и второму (13) вспомогательным источникам напряжения, стоки объединены и подключены к входу буферного усилителя (4), причем исток первого (10) выходного полевого транзистора соединен со стоком второго (6) входного полевого транзистора и связан с первой (14) шиной источника питания через первый (15) токостабилизирующий элемент, а исток второго (11) выходного полевого транзистора подключен к стоку четвертого (8) входного полевого транзистора и связан со второй (16) шиной источника питания через второй (17) токостабилизирующий элемент, кроме этого сток первого (5) входного полевого транзистора согласован с первой (14) шиной источника питания, а сток третьего (7) входного полевого транзистора согласован со второй (16) шиной источника питания, отличающийся тем, что между объединенными истоками первого (5) и второго (6) входных полевых транзисторов и объединенными истоками третьего (7) и четвертого (8) входных полевых транзисторов включен элемент стабилизации статического режима (9) входных полевых транзисторов на основе первого (18) дополнительного полевого транзистора и первого (19) дополнительного резистора, причем сток первого (18) дополнительного полевого транзистора подключен к объединенным истокам первого (5) и второго (6) входных полевых транзисторов, затвор первого (18) дополнительного полевого транзистора соединен с объединенными истоками третьего (7) и четвертого (8) входных полевых транзисторов, а исток первого (18) дополнительного полевого транзистора связан с объединенными истоками третьего (7) и четвертого (8) входных полевых транзисторов через первый (19) дополнительный резистор, первый (15) токостабилизирующий элемент выполнен на основе второго (20) дополнительного полевого транзистора и второго (21) дополнительного резистора, причем сток второго (20) дополнительного полевого транзистора подключен к первой (14) шине источника питания, затвор второго (20) дополнительного полевого транзистора соединен с истоком первого (10) выходного полевого транзистора, а исток второго (20) дополнительного полевого транзистора соединен с истоком первого (10) выходного полевого транзистора через второй (21) дополнительный резистор, второй (17) токостабилизирующий элемент выполнен на основе третьего (22) дополнительного полевого транзистора и третьего (23) дополнительного резистора, причем сток третьего (22) дополнительного полевого транзистора соединен с истоком второго (11) выходного полевого транзистора, затвор второго (20) дополнительного полевого транзистора подключен ко второй (16) шине источника питания, а исток третьего (22) дополнительного полевого транзистора связан со второй (16) шиной источника питания через третий (23) дополнительный резистор.

2. Операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом по п. 1, отличающийся тем, что сток первого (5) входного полевого транзистора связан с первой (14) шиной источника питания через первую (24) цепь согласования потенциалов, а исток третьего (7) входного полевого транзистора связан со второй (16) шиной источника питания через вторую (25) цепь согласования потенциалов.

3. Операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом по п. 1, отличающийся тем, что первый (10) выходной полевой транзистор выполнен по каскодной схеме и содержит первый (26) и второй (27) вспомогательные полевые транзисторы, причем затвор первого (26) вспомогательного полевого транзистора подключен к первому (12) вспомогательному источнику напряжения, а его исток соединен со стоком второго (6) входного полевого транзистора и затвором второго (27) вспомогательного полевого транзистора, сток первого (26) вспомогательного полевого транзистора подключен к истоку второго (27) вспомогательного полевого транзистора, сток которого связан с входом буферного усилителя (4), второй (11) выходной полевой транзистор выполнен по каскодной схеме и содержит третий (28) и четвертый (29) вспомогательные полевые транзисторы, причем затвор третьего (28) вспомогательного полевого транзистора подключен ко второму (13) вспомогательному источнику напряжения, а его исток соединен со стоком четвертого (8) входного полевого транзистора и затвором четвертого (29) вспомогательного полевого транзистора, сток третьего (28) вспомогательного полевого транзистора подключен к истоку четвертого (29) вспомогательного полевого транзистора, сток которого связан со входом буферного усилителя (4).

4. Операционный усилитель с «плавающим» входным дифференциальным каскадом на комплементарных полевых транзисторах с управляющим p-n переходом по п. 1, отличающийся тем, что первая (24) цепь согласования потенциалов содержит первый (30) и второй (31) согласующие полевые транзисторы, причем сток первого (30) согласующего полевого транзистора подключен к первой (14) шине источника питания, затвор первого (30) согласующего полевого транзистора соединен со стоком первого (5) входного полевого транзистора и истоком второго (31) согласующего полевого транзистора, исток первого (30) согласующего полевого транзистора связан с истоком второго (31) согласующего полевого транзистора через первый (32) согласующий резистор, а затвор второго (31) согласующего полевого транзистора подключен к первому (12) вспомогательному источнику напряжения, вторая (25) цепь согласования потенциалов содержит третий (33) и четвертый (34) согласующие полевые транзисторы, причем исток третьего (33) согласующего полевого транзистора соединен со стоком третьего (7) входного полевого транзистора и подключен к стоку четвертого (34) согласующего полевого транзистора, затвор третьего (33) согласующего полевого транзистора соединён со вторым (13) вспомогательным источником напряжения, затвор четвертого (34) согласующего полевого транзистора подключен ко второй (16) шине источника питания, а его исток связан со второй (16) шиной источника питания через второй (35) согласующий резистор, кроме этого стоки второго (31) и третьего (33) согласующих полевых транзисторов подключены к общей шине источника питания (36).

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2013 |

|

RU2523124C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2391769C1 |

| US 20180248524 A1, 30.08.2018 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2652504C1 |

Авторы

Даты

2021-01-22—Публикация

2020-09-02—Подача