Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих входных регистров цифровых ИМС, адресных регистров запоминающих устройств и входных регистров микропроцессорных систем.

Известно электронное устройство - Входной регистровый элемент [1]. Указанное устройство предназначено для передачи на выход OUT Входного регистрового элемента входного сигнала, поступающего на вход D величиной, соответствующей устойчивым значениям уровней рабочих напряжений стандартных цифровых КМОП ИМС.

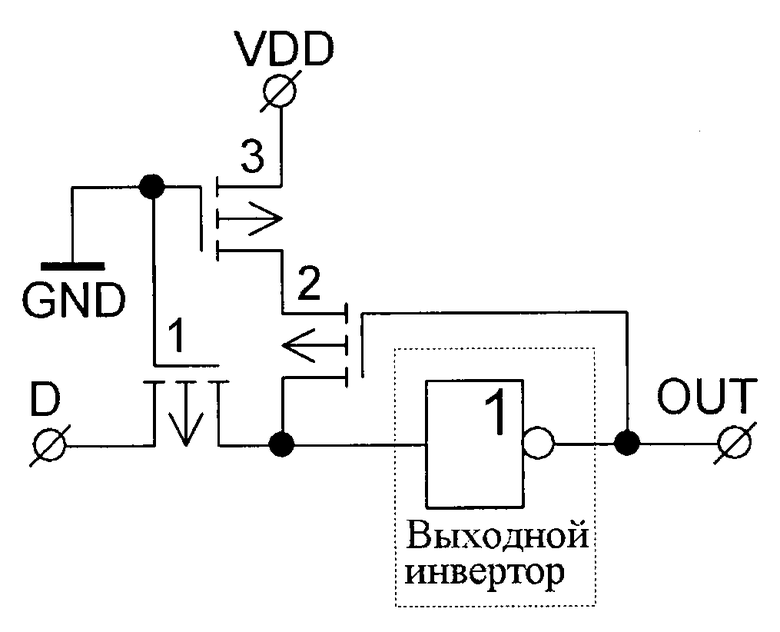

Данная схема Входного регистрового элемента содержит два МОП транзистора Р-типа, выходной инвертор, вход D и выход OUT, шину источника питания высокого уровня напряжения VDD (обозначенную в первоисточнике UИП) и шину источника питания низкого уровня напряжения GND. [1].

Недостатком известного устройства Входного регистрового элемента [1] является низкое быстродействие переключения сигнала, поступающего на его вход D, при изменении высокого уровня напряжения VDD на низкое GND. Одной из причин снижения быстродействия Входного регистрового элемента является задержка переходного процесса на входе выходного инвертора, вызванная противодействием высокого напряжения VDD на стоке открытого второго транзистора поступающему низкому напряжению GND.

Задачей предлагаемого изобретения является повышение быстродействия Входного регистрового элемента.

Поставленная задача достигается тем, что в схему Входного регистрового элемента [1], содержащую первый и второй МОП транзисторы Р-типа, выходной инвертор, вход которого соединен со стоками первого и второго МОП транзисторов, а выход - с затвором второго МОП транзистора и является выходом OUT Входного регистрового элемента, вход D Входного регистрового элемента, соединенный с истоком первого МОП транзистора, шину источника питания высокого уровня напряжения VDD, шину источника питания низкого уровня напряжения GND, соединенную с затвором первого МОП транзистора, введен третий МОП транзистор Р-типа, исток которого соединен с шиной источника питания высокого уровня напряжения VDD, затвор - с шиной источника питания низкого уровня напряжения GND, а сток - с истоком второго МОП транзистора.

В предлагаемый Входной регистровый элемент, введен третий МОП транзистор Р-типа, который включен последовательно между источником питания высокого уровня напряжения VDD и истоком второго МОП транзистора. Данное изменение схемы Входного регистрового элемента, образованное включением третьего транзистора в цепь подтяжки узла входа выходного инвертора к полному высокому уровню напряжения, позволяет уменьшить проводимость этой цепи до необходимого уровня. Уменьшение проводимости цепи подтяжки до полного высокого уровня напряжения узла входа выходного инвертора, позволяет уменьшить время переходного процесса перезарядки указанного узла при переключении на нем сигнала высокого уровня напряжения на низкий, что повышает быстродействие срабатывания этого узла и, соответственно, общее быстродействие схемы Входного регистрового элемента.

На Рисунке приведена схема предлагаемого Входного регистрового элемента.

Предлагаемый Входной регистровый элемент содержит МОП транзисторы Р-типа с первый (1), второй (2) и третий (3), выходной инвертор, вход которого соединен со стоками первого и второго МОП транзисторов, а выход - с затвором второго МОП транзистора и является выходом Входного регистрового элемента OUT, вход D Входного регистрового элемента, соединенный с истоком первого (1) МОП транзистора, шину источника питания высокого уровня напряжения VDD, соединенную с истоком третьего (3) МОП транзистора, сток которого соединен с истоком второго (2) МОП транзистора, шину источника питания низкого уровня напряжения GND, соединенную с затворами первого (1) и третьего (3) МОП транзисторов.

Предлагаемая схема Входного регистрового элемента представляет собой цифровую схему и предназначена для формирования выходного сигнала OUT на выходе схемы в зависимости от логического уровня сигнала данных на входе D и работает следующим образом.

Исходное состояние. Так как затворы МОП транзисторов Р-типа -первого (1) и третьего (3) подсоединены к источнику питания низкого уровня напряжения GND (соответствующему логическому «0»), то они постоянно открыты. Если при этом на вход данных D подано напряжение высокого уровня VDD (соответствующиее логической единице «1»), то напряжение логической единицы «1» подается на вход выходного инвертора через открытый первый (1) МОП транзистор. Поэтому на выходе выходного инвертора установлено напряжение логического «0», инверсное своему входному напряжению, которое поступает на затвор второго (2) МОП транзистора и на выход OUT Входного регистрового элемента. При этом на входе выходного инвертора удерживается высокое напряжение логической «1» через открытые МОП транзисторы Р-типа второй (2) и третий (3).

При изменении на входе данных D Входного регистрового элемента входного сигнала с высокого логического уровеня «1» на низкий «0», на вход выходного инвертора через открытый первый (1) МОП транзистор Р-типа поступает напряжение логического «0». Это напряжение ограниченно пороговым напряжением первого (1) МОП транзистора и достигает низкого уровеня напряжения равного приблизительно величине этого порогового напряжения ~VПOP. Однако этого напряжения достаточно для того, чтобы полностью переключить выходной инвертор и сформировать на его выходе OUT полноценный высокий логический уровень напряжения «1». Кроме того, напряжение высокого уровня «1» с выхода Входного регистрового элемента OUT поступает на затвор второго (2) МОП транзистора Р-типа в результате чего второй (2) МОП транзистор закрывается.

При переходе схемы Входного регистрового элемента в исходное состояние на вход данных D поступает напряжение высокого логического уровня «1», которое через открытый первый (1) МОП транзистор передается на вход выходного инвертора и перезаряжает емкостную нагрузку этого узла. Согласно своему функциональному назначению, выходной инвертор инвертирует входное напряжение высокого уровня «1» в напряжение низкого уровня «0», которое поступает на затвор второго (2) МОП транзистора Р-типа и на выход OUT Входного регистрового элемента. Поэтому второй (2) МОП транзистор открывается напряжением низкого уровня «0» и через два последовательно включенных открытых МОП транзистора Р-типа первый (3) и второй (2) напряжение высокого уровня VDD поступает на вход выходного инвертора, тем самым удерживая на его выходе OUT напряжение низкого уровня GND, соответствующее исходному состоянию Входного регистрового элемента.

В предлагаемый Входной регистровый элемент, введен третий МОП транзистор Р-типа, который включен последовательно между источником питания высокого уровня напряжения VDD и истоком второго МОП транзистора. Данное изменение схемы Входного регистрового элемента, образованное включением третьего транзистора в цепь подтяжки узла входа выходного инвертора к полному высокому уровню напряжения, позволяет уменьшить проводимость этой цепи до необходимого уровня. Уменьшение проводимости цепи подтяжки до полного высокого уровня напряжения узла входа выходного инвертора, позволяет уменьшить время переходного процесса перезарядки указанного узла при переключении на нем сигнала с высокого уровня напряжения на низкий, что повышает быстродействие срабатывания этого узла и, соответственно, общее быстродействие схемы Входного регистрового элемента.

Таким образом, в предлагаемой схеме Входного регистрового элемента быстродействие повышено.

Литература

1. Кармазинский А.М. Синтез принципиальных схем цифровых элементов на МДП-транзисторах. - М.: Радио и связь, 1983. Рис. 3.18в, стр. 137.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2814896C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2802665C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2021 |

|

RU2756445C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2020 |

|

RU2739487C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2642416C1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении быстродействующих входных регистров цифровых ИМС, адресных регистров запоминающих устройств и входных регистров микропроцессорных систем. Технический результат заключается в повышении быстродействия входного регистрового элемента. Технический результат достигается за счет того, что схема входного регистрового элемента содержит три МОП-транзистора Р-типа, выходной инвертор, вход D и выход OUT, шину источника питания высокого уровня напряжения VDD и шину источника питания низкого уровня напряжения GND. 1 ил.

Входной регистровый элемент, содержащий первый и второй МОП-транзисторы Р-типа, выходной инвертор, вход которого соединен со стоками первого и второго МОП-транзисторов, а выход - с затвором второго МОП-транзистора и является выходом OUT входного регистрового элемента, вход D входного регистрового элемента, соединенный с истоком первого МОП-транзистора, шину источника питания высокого уровня напряжения VDD, шину источника питания низкого уровня напряжения GND, соединенную с затвором первого МОП-транзистора, отличающийся тем, что в него введен третий МОП-транзистор Р-типа, исток которого соединен с шиной источника питания высокого уровня напряжения VDD, затвор - с шиной источника питания низкого уровня напряжения GND, а сток - с истоком второго МОП-транзистора.

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| СХЕМА ФОРМИРОВАТЕЛЯ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2017 |

|

RU2664014C1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| KR 102122304 B1, 12.06.2020 | |||

| US 6777981 B2, 17.08.2004. | |||

Авторы

Даты

2025-03-17—Публикация

2024-07-09—Подача