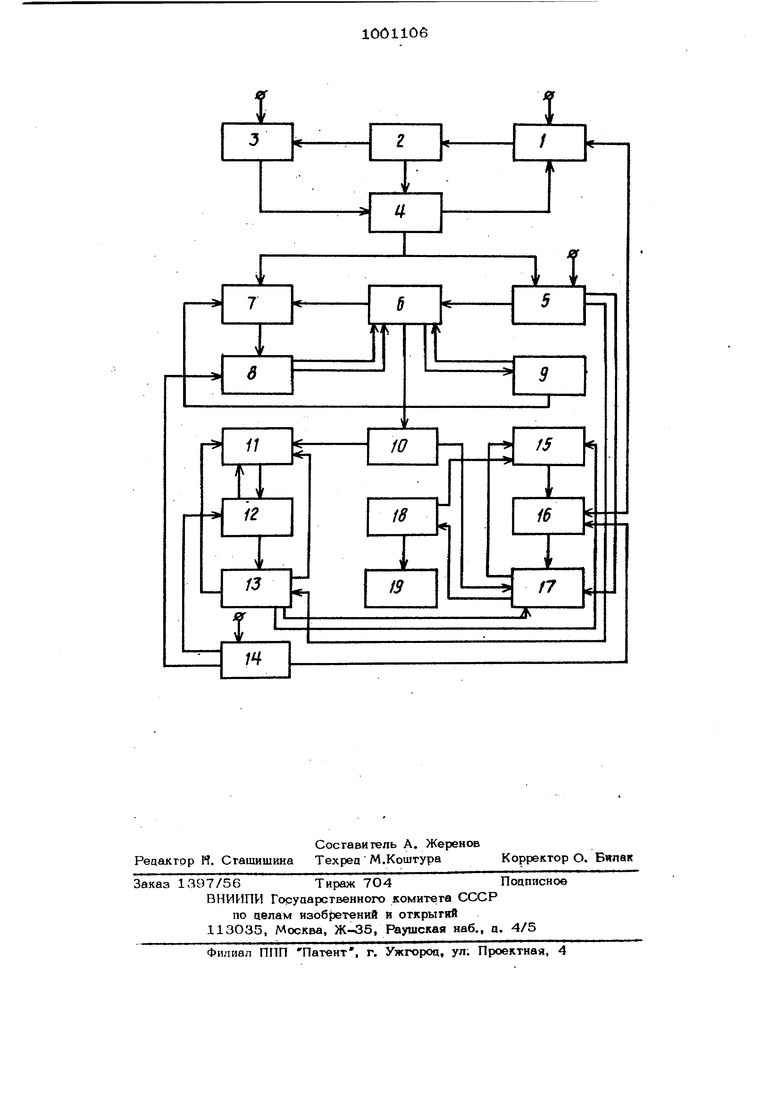

Изобретение относится к вычислителе ной технике и может быть использовано аля решения планирования экспериментов, проводимых при исслецовании сложных систем. Известно решение поцобных зацач на универсальных цифровых вычислительных машинах. При этом планирование экспериментов основано на использовании логических алгоритмов перебора различных значений исходных параметров, а также на решение оптимизационных задач 111 Использование универсальных цифровы машин не всегда в:озможно из-за их высокой стоимости. Кроме того, решение , поцобных 1 задач на универсальных ЭВМ требует значительных затрат времени и оперативной памяти, что не позволяет использовать их для решения зааач поцыгрыша исходной информацид.при. провецеНИИ испытаний различных систем в реаль ном масштабе времени. Наиболее близким к предлагаемому по технической сушности является устрой ство, содержашее генератор импульсов, счетчик, блок памяти, блок вычитания, два блока деления, причем первый вхоц генератора импульсов является одним из входов устройства, выход генератора импульсов соединен с входом первого счет чика 12 . Известное устройство не позволяет получить кодирование значения факторов и обладает недостаточней производительнос тью. Цель изобретения - повьш1ение прои . вод ительности. Поставленная цель достигается тем, что в устройство для решения задач планирования экспериментов, сопержашее генератор прямоугольных импульсов, первый счетчик и первый блок памяти, блок индикации, причем первый вход генератора прямоугольных импульсов является первым входом устрсЛства, выход соединен с входом первого счетчика, введены три сумматора, пять схем сравнения, буфе1 ный регистр, вторые, третьи н четвертые , 3100 счетчики и блоки памяти, причем первые входы первого, второго и четвертого 6nok©B памяти являются соответственно вторым, третьим и четвертым входами устройства, первый выход первого счетчи ка соединен с вторым..входом первого блока памяти, второй выход первого счет чика соединен с первым входом первой схемы бравнения, второй вход которой соединен с вькодом первого блока памяти первый выхЬд первой схемы сравнения соединен с вторым входом генератора прямоугольных импульсов, второй выход 1 ервой схемы сравнения соединен с первым входом второго счетчика и с вторым входом второго блока памяти, первый вь ход которого соединен с первым входом третьего блока памяти, первый выход которогосоединен с вторым входом второго счетчика, выход которого соединен с первым входом второй схемы сравнения, третий вход второго счетчика соединен с первым выходом третьей схемы сравнения, второй выход которой соединен с вторым входом третьего блока памяти, второй выход которого соединен с входом третьей схемы сравнения. Третий ВХОД третьего блока памяти соединен с первым выходом второй схемы сравнения, второй выход которой соединен с четвертым входом третьего блока памяти третий вьосод которого соединен с входом первого сумматора, второй выход второго блока памяти соединен с первым входом второго сумматора, третий выход второго блока памяти соединен с первым вхоаом третьего сумматора, вькод перового сумматора соединен с первым входом третьего счетчика, второй вход третьего счетчика и первьй вход четвертого счетчика соединены соответственно с выходами второго и третьего сумматоров, второй вход четвертого счетчика соединен с выходом второго сумматора, третий вход третьего счетчика соединен с выходом второго сумматора, четвертый вхоа третьего счетчика соединен с первым выходом четвертой схемы сравнения, первый вход которой соединен с выходом третьего счетчика, второй вход четвертой схемы сравнения соединен с первым выходом четвертого блока памяти, второй выход которого соединен с вторым входом второй схемы сравнения, второй выход четвертой схемы сравнения соединен с вторым входом второго сумматора, выход которого соединен с вторым входом треть его сумматора, третий вход которого соединен с выходом первого сумматора. 64 третий вьсхоц четвертого блока памяти соединен с первым вхоаом пятой схемы сравнения, второй вхоц которой соединен с выходом четвертого счегчика, первый выход пятой схемы сравнения соединен с четвертым входом третьего сумматора, выход которого соединен с входом буферного регистра, первый выход которого соединен с третьим входом четвертого „рой выход буферного регист соединен с входом блока индикации, второй выход пятой схемы сравнения подключен к третьему входу генератора прямоугольных импульсов. На чертеже представлена функаиональ ная схема устройства. Устройство содержит генератор 1 прямоугольных импульсов, счетчик 2, блок 3 памяти, схему 4 сравнения, блоки 5 и б памяти, счетчик 7, схемы 8 . и 9 сравнения, сумматор 10, счетчик 11, схему 12 сравнения, сумматор 13, блок 14 памяти, счетчик 15, схему 16 с.равненй1я сумматор 17, буферный регистр g Q индикации. Генератор импульсов выполнен на интегральных схемах. Блоки 3 и 14 памяти представляют собой регистровую память выполненную на интегральных схемах. Блок 5 памяти выполнен в виде матрицы, в строках которой натуральные значения факторов. Количество строк в матрице соответствует количеству опытов в эксперименте. Количество cjOH6uoB соответствует количеству факторов в опыте. Для повышения быстродействия при расчете коэффициентов регрессии необходимо производить кодирование факторов, т,е, значение независимой переменной в натуральном масштабе заменять на кодированное. Кодирование факторов производится по следующему алгоритму: li 1,n) где И - количество опытов в эксперименте-, m - количество факторов в опыте; X,-: - натуральные значения факторов;Xf. - кодированные значения факто ров .( 1 1,п j l,m ). Устройство работает следующим о&разом. Перец началом работы в блок 3 памяти заносится значениеtn , в блок 14 памяти заносится значение t . В бло 5памяти заносятся значения элементов матрицы II X ij If . Состояние счетчиков 2, 7, 11 и 15 устанавливается равным нулю. . Сигнал П/ск поступает на вход генератора 1, с которого поступает на вхо счетчика 2. При этом содержимое счет-чика 2 устанавливается равным единице. На схеме 4 сравнения происходит сра&нение содержимого блока 3 памяти и результата счегчика 2 (). При сигналом со схемы 4 сравнения прекращается работа генератора 1. При j m по сигналу схемы 4 сравнения к содерж мому счетчика 7 добавляется единица, а из блока 5 памяти считываются в бло 6памяти элементы j -го столбца матри цы . В схеме 9 сравнения производится сравнение содержимого первой и второй ячеек блока 6 памяти. Если содержимое первой ячейки блока 6 памяти меньше или равно содержимом второй ячейки, то к содержимому счетчи ка 7 прибавляется единица. При этом в схеме 8 сравнения производится сравнени содержимого второго счетчика 7 с содер жимым блока 14 памяти. Если содержимое счетчика 7 меньше содержимого блока 14 памяти, то из блока 6 памяти на схему 9 сравнения считывается содержимое второй и третьей ячеек. Если содержимое первой ячейки блока 6 памя ти больше содержимого второй ячейки блр ка 6 памяти, то в первую ячейку блока в памяти заносится содержимое второй ячейки, а во вторую - содержимое ячейки. Одновременно к содержимому счетчика 7 добавляется единица и т.д. до гех пор, пока содержимое счетчика 7 станет равным содержимому блока 14 памяти. Тогда на сумматор 10 поступае содержимое первой и последней ячеек блока 6 памяти. В результате работы блоков 6 - 9 в первой ячейке блока 6 памяти находится минимальное значение из элементов j -го столбца матрицы, т.е. mi. Л , а в последней ячейке второго блока 6 памяти находится максимальное значение из элементов j-го столбца матрицы, т.е. . В сумматоре 1О производится действ iTicixrx..1-ntinrx.-l i 1j i I MJ Затем к содержимо мому счетчика 11 добавляется единица. На схеме 12 сравнения производится сравнение содержимого счетчика 11с содержимым блока 14 памяти. При i п на сумматоре 13 производится накоплеПх.. При t П состо- ние суммы 1 яние счетчика 11 устанавливается равным нулю. Сигналом с сумматора 13 к счетчику 15 прибавляется единица. На схеме 16 сравнения производится сравнение результата счетчика 15 и содержимого блока 14 памяти. При п в сумматоре 17 ,вроизво Г 1дится действие -4:-- , где Лу - элемент первого (j -го} столбца матрицы It , находящейся в блоке 5 памяти, Р| - результат сумматора 13, J; - результат сумматора 1О. Результат сумматора 17 записывается в буферном {эегистре 18. При состояние счетчика 15 устанавливается равным нулю, а генератор 1 выдает второй импульс, по которому содержимое счетчика 2 становится равным двум и устройство продолжает работу по алгоритму, описанному выше. Генератор 1 прекрашает работу, когда значение счетчика 2 станет равным tn . Тогда на блоке 19 индикации высвечиваются значения результата - кодированные значения факторов (матрица ). Оценка предложения проводилась методом математического моделирования, которым была подтверждена работоспособность предлагаемого устройства и его более высокая производительность по сравнению с известными устройствами. Результаты математического моделирования показали, что изобретение повьш1ает быстродействие вычислительных машин на 20-26%. Кроме того, использование предлагаемого изобретения позволяет расширить класс решаемых задач за счет возможности вычисления кодированных значений факторов, что значительно повьпиает быстродействие при решении задач планирования экспериментов. Формула изобретения Устройство для решения задач плани-. рования экспериментов, содержашее генератор прямоугольных импульсов, первый счегчик и первый блок памяти, блок индикации, причем первый вход генератора прямоугольных импульсов является вхоцом устройства, выход соеаинен с вхоцом первого счетчика, о т л и ч а ю ш е е с я тем, что, с целью повышения производительности, в него введены три сумматора, пять схем сравнения,

буферный регистр, вторые, третьи и четвертые счетчики и блоки памяти, причем первые входы первого, второго и четверг того блоков памяти являются соответственно вторым, третьим и четвертым входам и устройства, первый выход первого счетчика соединен с вторым входом первого блока памяти, второй выход первог счетчика соединен с первым входом первой схемы сравнения,второй вхоа которой .

соединен с выходом первого блока памяти первый выход первой схемы сравнения соединен с вторым входом генератора прямоугольных импульсов, второй выход первой схемы сравнения соединен с первым входом второго счетчучса и с вторым входом второго блока памяти, первый выход которого соединен с первым входом третьего блока памяти, первый выход которого соединен с вторым входом вто- ,рого счетчика, выход которого соединен с первым входом второй схемы сравнения третий вход второго счетчика соединен с первым выходом третьей схемы сравнения, второй выход которой соединен с вторым входом третьего блока памяти, второй выход которого соединен с входом третьей схемы сравнения, третий вход третьего блока памяти соединен .с первым выходом второй схемЬ сравнения, второй выход которой соединен с четвертым входом третьего блока памяти, третий выход которого соединен с входом первого сумматора, второй выход второго блока памяти соединен с первым входом второго сумматора, третий выход второго блока памяти соединен с первым входом третьего сумматора, выход первого сумматора соединен с первым вхоцом третьего счетчика, второй вход третьего счет- чика и первый вход четвертого счетчика соединены соответственно с выходами второго и третьего сумматоров, второй вход четвертого счетчика соединен с вь ходом второго сумматора, третий вход третьего счетчика соединен с выходом второго сумматора, четвертый вход третьего счетчика соединен с первым выходом четвертой схемы сравнения, первый вход которой соединен с выходом третьего счетчика, торой вход четвертой схемы сравнения соединен с первым выходом четвертого блока памяти, второй выход которого соединен с вторым входом второй схемы сравнения, второй выход чет вергой схемы сравнения соединен с вторым входом второго сумматора, выход которого соединен с вторым входом третьего сумматора, третий вход которого соединен с выходом первого сумматора, третий выход четвертого блока памяти соединен с первым входом пятой схемы сравнения, второй вход которой соединен с выходом четвертого счетчика, первый вьисод пятой схемы сравнения соединен с четвертым входом третьего сумматора, выход которого соединен с входом буферного регистра, первый выход которого соединен с третьим входом четвертого счетчика, второй выход буферного регистра соединен с входом блока индикации, второй выход пятой схемы сравнения подключен к Tpetbему входу генератора прямоугольных импульсов.

Источники информации, принятые во внимание при экспертизе

1.Адлер Ю. П., Маркова Е. В., Грановский Ю. В. Планирование эксперимента при поиске оптимальных условий, М., Наука, 1976, с, 72,

2,Авторское свидетельство СССР по заявке № 293О157/18-24,

кл. Q 06 F 15/20, 1980, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования выдачи топлива | 1981 |

|

SU1008707A2 |

| Устройство для синтеза регрессионных моделей многомерной статистики | 1980 |

|

SU942031A1 |

| Система оптимизации режимов работы объекта | 1985 |

|

SU1287103A1 |

| Система оптимизации режимов работы объекта | 1985 |

|

SU1260916A1 |

| Устройство для вычисления коэффициентов полинома | 1980 |

|

SU960835A1 |

| Генератор псевдослучайных процессов | 1984 |

|

SU1261087A1 |

| Устройство для расчета временных затрат оператора | 1980 |

|

SU959088A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2020766C1 |

| Система автоматической оптимизации | 1983 |

|

SU1125602A1 |

Авторы

Даты

1983-02-28—Публикация

1981-10-23—Подача