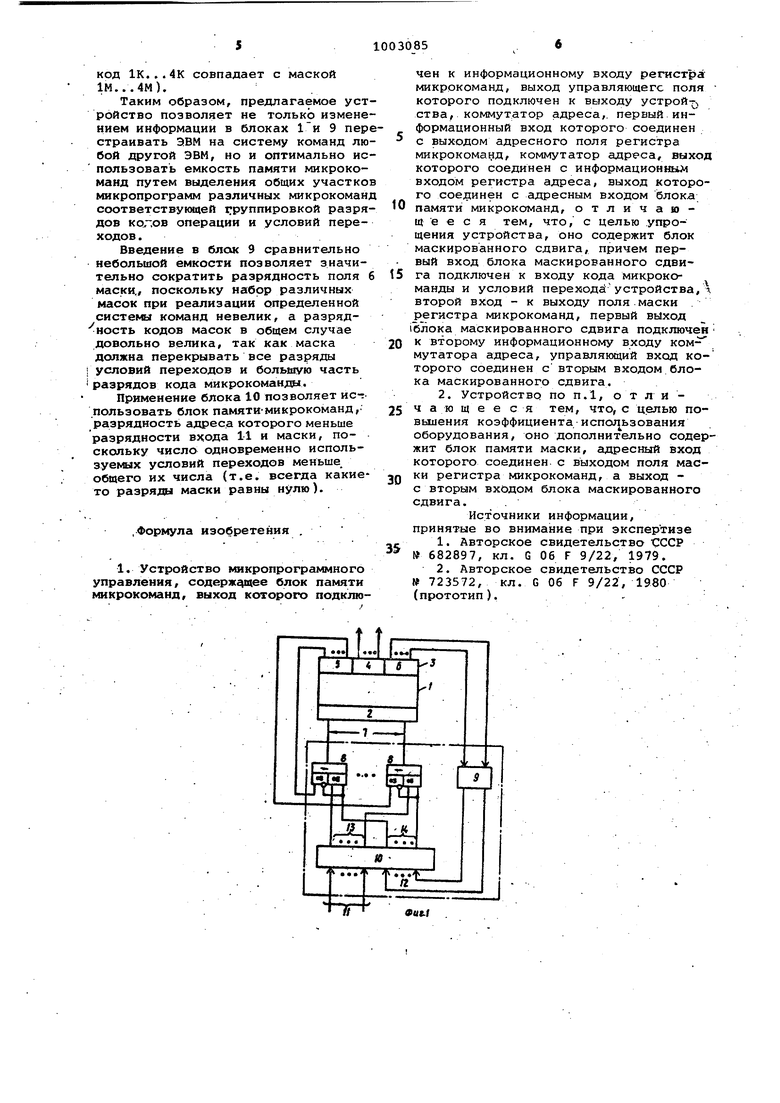

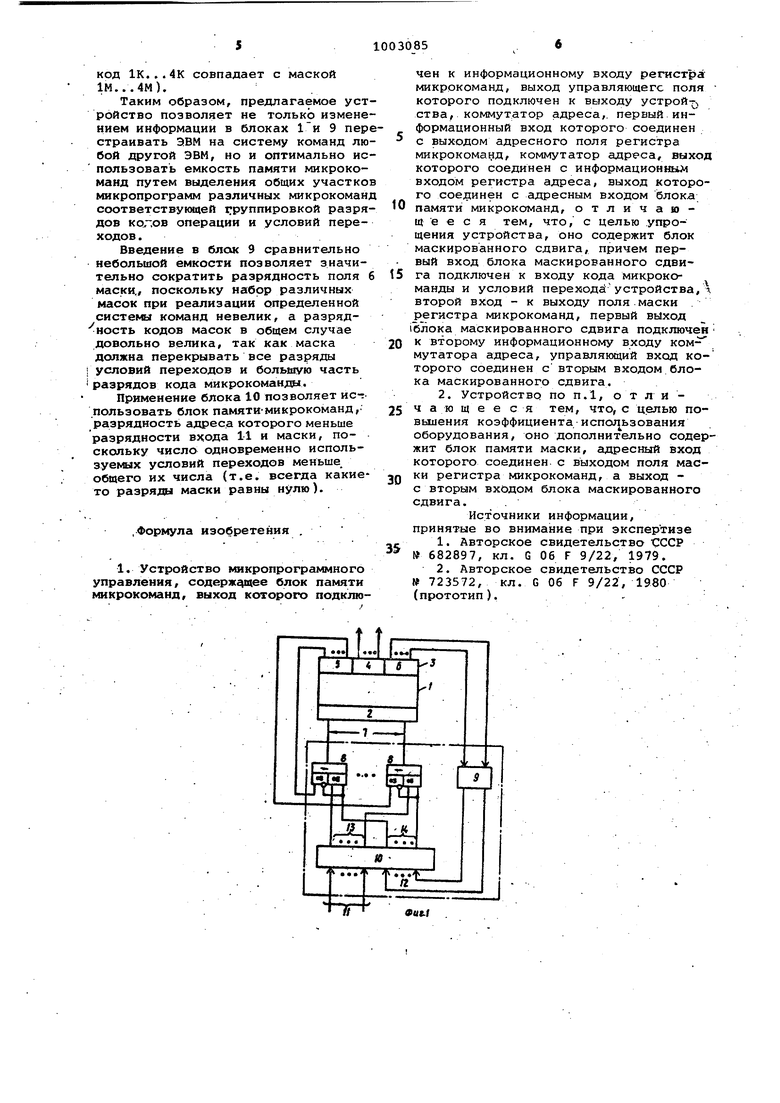

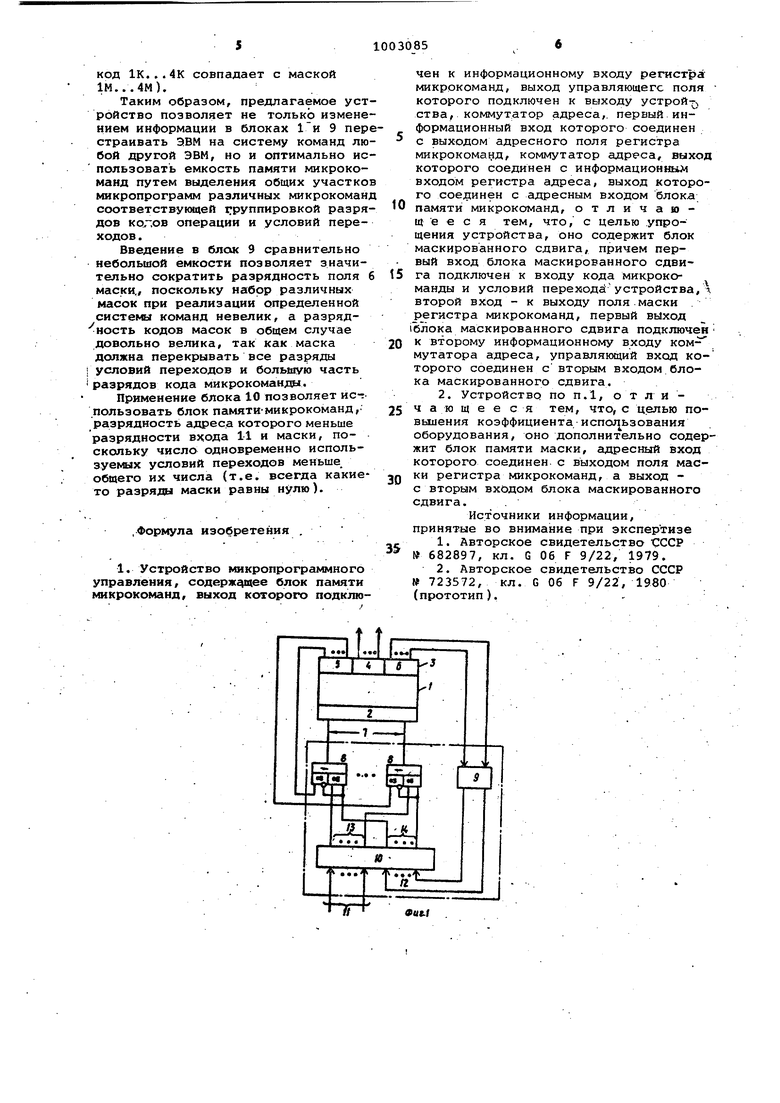

микрокоманд, выход управляющего поля которого подключен квыходу устройства, коммутатор адреса, первый информационный вход которого соединен с выходом адресного поля регистра микрокоманд,коммутатор адр са, выход которого . соединен с инф мационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, введен блок максированного сдвига, причем первый вход бло ка маскированного сдвига подключен входу кода микрокоманды и условий перехода устройства, второй вход к выходу поля маски регистра микрокоманд, первый выход блока маскированного сдвига подключен к второму информационному входу коммутатора адреса, управляющий вход которого соединен с вторым входом блока маск пованного сдвига. . С целью повышения коэффицие нта использования оборудования, в устройство введен блок памяти маски, адресный вход которого соединен с выходом поля маски регистра-микрокоманд, а выход с вторым входс м блока маскированного, сдвига. На фиг. 1 изображена-функциональ ная схема предлагаемого устройстBaf на фиг. 2 - диаграмма, поясняю щая прицип действия блока маскированного сдвига; на фиг. 3 - пример реализации блока маскированного сд га. Устройство содержит блок 1 памят микрокоманд, регистр 2 адреса, регистр 3 микрокоманд, имеющий поле 4 управления, поле 5 адреса и поле 6 маски, выход. 7 коммутатора 8 адреса блок 9 памяти масок, блок 10 маскированного сдвига, вход 11 кодов мик рокоманды и условий переходов, выход 12 блока 9, первый выход 13 бло ка 10, второй выход 14 блока 10. Блок 10 маскированного сдвига (фиг. 3) содержит элементы И 15-17 и элементы И-ИЛИ 18-23. Устройство работает следующим образом. Первоначально регистр 2 обнулен и из блока 1 считывс;ется начальная микрокоманда по адресу, указанному в поле б маски, по которой из блока 9 считывается маска. В блоке 10 те разряды :кода,j принимаемого с входа 11, которым соответствуют единицы в коде маски, сдвигаются вправо вплотную друг к другу (собираются). Собранный таким образом код с первого выхода 13 блока 10 поступает на коммутатор 8. Одновременно в блоке 10 собирают.ся вместе со сдвигом вправо все разряды маски, равные единице, и со второго выхода 14 поступают на управляющий вход коммутатора 8. На выходе 7 коммутатора 8 появляется код, совпадающий в первых k разрядах с собранн(шии маскированными разрядами, а в остальных n-k разрядах - с n-k , старшими разрядами кода поля 5 адреса, где k - количество единиц в коде маски. На фиг. 2 иллюстрируется сборка 8-разрядного кода. Слева обозначены входы и выходы, на которых наблюдаются эти, показанные справа, коды. Разряды, значения которых безразличны, обозначены через X. Пусть поле 5 адреса содержит нулевой код, а код маски на втором входе 12 блока 10 содержит единицы в разрядах, соответствующих определенным разрядам кода операции микрокоманды, поступающего по входу 11. При этом на выходе коммутатора 8 из маскируемых разрядов кода операции вырабатывается адрес, по которому из блока 1 выбирается первая микрокоманда микропрограмлм, соответствующей данной микрокоманде, т.е. выполняется дешифрация выделенной час.ти операции. Бели маска микрокоманды нулевая, то адрес следующей микрокоманды совпадает с кодом поля 5 адреса. Если же очередная маска содержит единицы в paзpя : дx, соответствующих некоторым разрядам кода операции, то по этим разрядам осуществляется вторая ступень дешифрации кода операции. Таким /образом, задавая определенные маски, можно осуществить многоступенчатую (и в произвольном порядке ) дешифрацию кода операции. Если маска содержит единицу в разряде, соответствующем какому-либо условию или состоянию ЭВМ, то в зависимости от выполнения этого условия или наличия этого состояния происходит ветвление микротгрограммы. Так как код маски .можно задавать произвольно, то этапы дешифрации кода операции и условия: ветвления микропрограммы можно задавать также произвольно и в любом их сочетании. Это позволяет произвольно изменять формат, команды, отводя под код .операции и режима адресации любые-разряды регистра команд ЭВМ, и любым образом кодировать операции. Выбор той кли иной кодировки никак не отражается на устройстве коммутатора. 8 и определяет лишь информацию,, которую необходимо занести в блоки 1 и 9. На фиг. 1 показан пример принципиальной схемы блока 10 -4-разрядного кода 1К...4К по маске 1М...4М. Разряды собранного кода обозначены, соответственно, через 1СК...4СК. Аналогичную схему можно использовать для сборки маски (считая, что код IK...4К совпадает с маской 1М...4М). Таким образом, предлагаемое уст ройство позволяет не только измене нием информации в блоках 9 пер страивать ЭВМ на систему команд лю бой другой ЭВМ, но и оптимально ис пользовать емкость памяти микрокоманд путем выделения общих участко микропрограмм различных микрокоман соответствующей г руппировкой разря дов ког.ов операции и условий переходов . Введение в блох 9 сравнительно небольшой емкости позволяет значительно сократить разрядность поля маски,, поскольку набор различных масок при реализации определенной системы команд невелик, а разрядность кодов масок в общем случае довольно велика, так как маска должна перекрывать все разряды i условий переходов и большую часть разрядов кода микрокоманды. Применение блока 10 позволяет ис-; пользовать блок памяти-микрокоманд, разрядность адреса которого меньше разрядности входа 11 и маски, поскольку число одновременно используемых условий переходов меньше общего их числа (т.е. всегда какие то разряды маски равны нулю). .Формула изобретения , 1. Устройство микропрограммного управления, содержгдаее блок памяти микрокоманд, выход которого подключен к информационному входу регистрамикрокоманд, выход управляющегс поля которого подключен к выходу устройства, коммутатор адреса,, первый, информационный вход которого соединен с выходом адресного поля регистра микрокоманд, коммутатор адреса, выход которого соединен с информационными входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, отличаю ц е е с я тем, что, с целью .упрощения устройства, оно содержит блок маскированного сдвига, причем первый вход блока маскированного сдвига подключен к входу кода микрокоманды и условий переходиустройства, второй вход - к выходу поля.маски . р егистра микрокоманд, первый выход блока маскированного сдвига подключен к второму информационному входу коммутатора адреса, управляющий вход которого соединен с вторым входом.блока маскированного сдвига. 2. Устройство по П.1, отличающееся тем, что, с целью повыиения коэффициента использования оборудования, оно дополнительно содержит блок памяти маски, адресный вход которого соединен, с выходом поля маски регистра микрокоманд, а выход с вторым входом блока маскированного сдвига. .. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 682897, кл. G Об F 9/22, 1979. 2.Авторское свидетельство СССР 723572, кл. G Об F 9/22, 1980 (прототип)./ О / О X Л X X

(I II

/ 0100101 X X X X О 10 1

ft- 0.x {о X. IX X

II- 0 о ( 00

к- Q. 000 / / / /.

I I I ( Фиг2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

Авторы

Даты

1983-03-07—Публикация

1981-10-21—Подача