Изобретение относится к вычислительной технике и может быть применено для усиления сигналов считываемой информации в запоминающих усх-г. ройствах на дополнягаоих мдп-транзисторах.

Известны усилители считывания,, содержащие триггер на МДП-транзистррах, затворы нгорузочных транзисторов в котором соединены со входами усилителя считьюания, а также содержсццих стробирующие транзисторы, включенные между общей шиной и транзисторами, соединеннь ш по схеме с перекрестной связью, или между общей шиной и нагрузочными транзисторами fl 3.

Недостатком этих усилителей считывания является большёш потребляемая мощность.

Наиболее близким к предлагаемому является усилитель считывания на дополняющих МДП-транзисторах,содерЖс1щий первый и второй р-канальные транзисторы, соединенные по схеме с перекрестной связью, истоки которых соединены с шиной питания, стоки - соответственно со входами первого и второго инвертора и соответственно со стоками первого и второго нагрузочных п-канальных транзисторов затворы которых соединены соответственно с первым и вторым входами усилителя считывания, истоки со стоком п-канального стробирукнцего транзистора, затвор которого соединен с шиной , исток -. с общей шиной t2l.

Недостатком известного усилителя.

10 считывания является большая потребляемая мощность, обусловленная сквозным протеканием тока -после переключения усилителя считывания.

Цель изобретения - уменьшение

15 мощности, потребляемой усилителемсчитывания.

Поставленная цель достигается тем, что усилитель считывания на ,4 дополняющих МДП-транзисторах, включающий первый и второй ключевые р.-кансшьные транзисторы, соединенные перекрестной связью, истоки которых соединены с шиной питания, стоки - соответственно со входами

25 первого и второго инвертируюидах транзисторов и соответственно - со стоками первого и второго нагрузочных п-канальных транзисторов, затворы которых являются соответственна

30 первым и вторым входами усилителя

считывания, истоки первого и второго нагрузочных п-канальных транзисторов - со стоком п-гканального стробирующего транзистора, затвор которого соединен с шиной строба, исток - с общей шиной,содержит два форсирующих п-канальных транзистора и два установочных р-канальных транзистора, причем истоки форсирующих п-канальных транзисторов соединены со стоком стробирующего транзистора, сток первого форсирующего п -канального транзистора соединен с затвором первого нагрузочного п -канального транзистора, а затвор - с выходом второго инвертирующего транзистора, сток второго форсирующего П -канального транзистора соединен с затвором второго нагрузочного п -канального транзистора, а затвор - с выходом первого инвертирующего транзистора, истоки первого и второго установочных р-канальных транзисторов соединены с шиной питания, затворы - с шиной строба, стоки - соответственно со стоками первого и второго нагрузочных п-канальных транзисторов, исток стробирующего транзистора соединен с истоками первого и второго инвертирующих транзисторов и общей шиной.

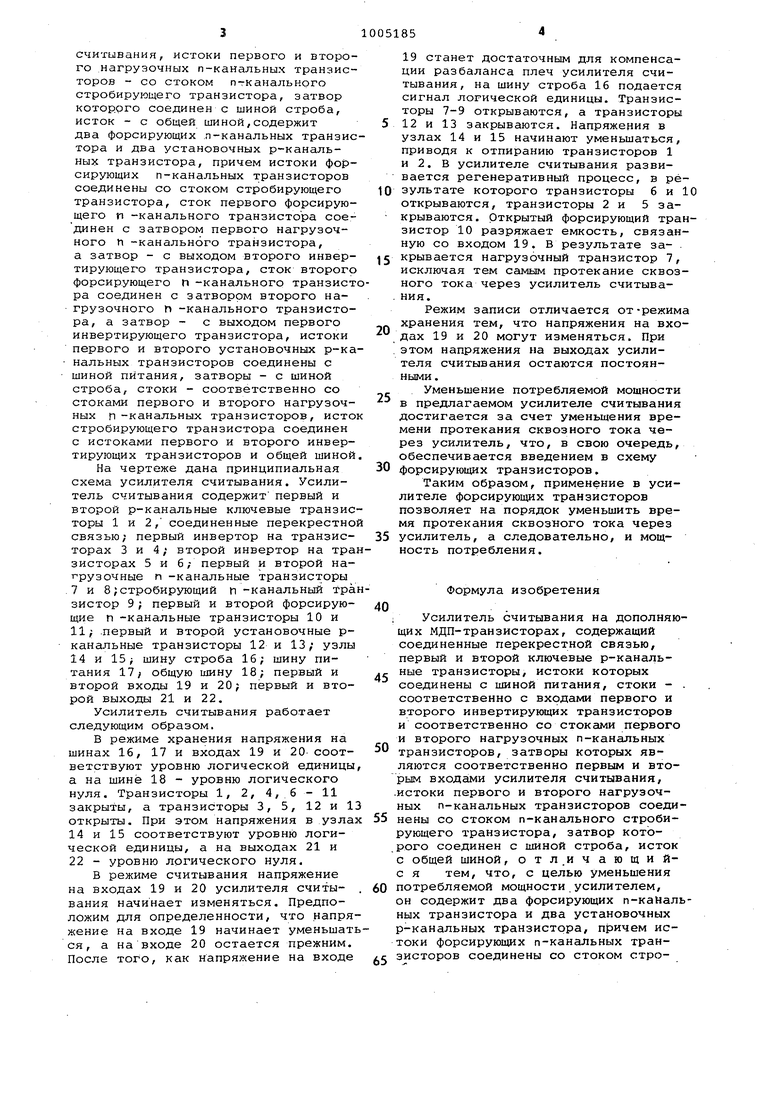

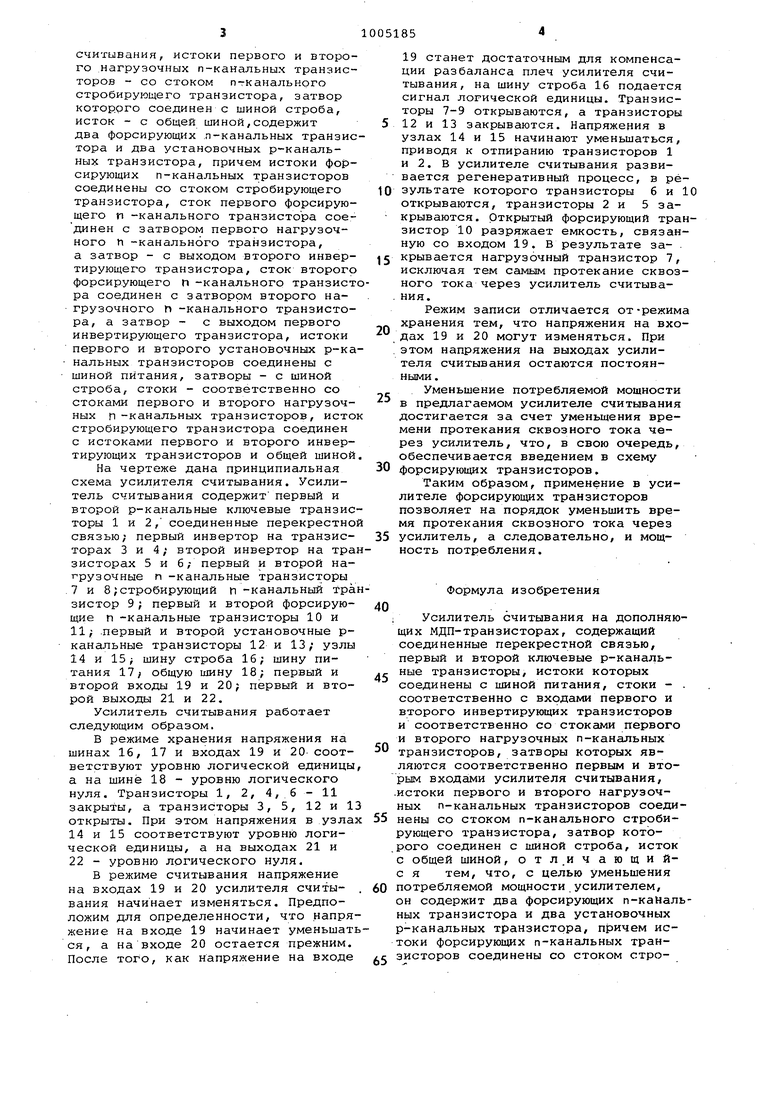

На чертеже дана принципиальная схема усилителя считывания. Усилитель считывания содержит первый и второй р-канальные ключевые транзисторы 1 и 2, соединенные перекрестной связью; первый инвертор на транзисторах 3 и 4; второй инвертор на транзисторах 5 и б,- первый и второй нат рузочные п -канальные транзисторы 7 и 8;стробирующий п -канальный транзистор 9; первый и второй форсирующие п -канальные транзисторы 10 и 11; .первый и второй установочные рканальные транзисторы 12 и 13; узлы 14 и 15; шину строба 16; шину питания 17; общую шину 18; первый и второй входы 19 и 20; первый и второй выходы 21 и 22.

Усилитель считывания работает следующим образом.

В режиме хранения напряжения на инах 16, 17 и входах 19 и 20 соответствуют уровню логической еди-ницы, на шине 18 - уровню логического нуля. Транзисторы 1, 2, 4, 6 - 11 закрыты, а транзисторы 3, 5, 12 и 13 ткрыты. При этом напряжения в узлах 14 и 15 соответствуют уровню логиеской единицы, а на выходах 21 и 22 - уровню логического нуля.

В режиме считывания напряжение а входах 19 и 20 усилителя считы- . ания начинает изменяться. Предпоожим для определенности, что напряение на входе 19 начинает уменьшатья, а на входе 20 остается прежним. осле того, как напряжение на входе

19 станет достаточным для компенсации разбаланса плеч усилителя считывания, на шину строба 16 подается сигнал логической единицы. Транзисторы 7-9 открываются, а транзисторы 12 и 13 закрываются. Напряжения в узлах 14 и 15 начинают уменьшаться, приводя к отпиранию транзисторов 1 и 2. В усилителе считывания развивается регенеративный процесс, в результате которого транзисторы 6 и 1 открываются, транзисторы 2 и 5 закрываются. Открытый форсирующий транзистор 10 разряжает емкость, связанную со входом 19. В результате за- . крывается нагрузочный транзистор 7, исключая тем самым протекание сквозного тока через усилитель считывания.

Режим записи отличается от-режима хранения тем, что напряжения на входах 19 и 20 могут изменяться. При этом напряжения на выходах усилителя считывания остаются постоянными .

Уменьшение потребляемой мощности в предлагаемом усилителе считывания достигается за счет уменьшения времени протекания сквозного тока через усилитель, что, в свою очередь, обеспечивается введением в схему форсирующих транзисторов.

Таким образом, применение в усилителе форсирующих транзисторов позволяет на порядок уменьшить время протекания сквозного тока через усилитель, а следовательно, и мощность потребления.

Формула изобретения

Усилитель считывания на дополняющих МДП-транзисторах, содержащий соединенные перекрестной связью, первый и второй ключевые р-канальные транзисторы, истоки которых соединены с шиной питания, стоки - . соответственно с входами первого и второго инвертирующих транзисторов и соответственно со стоками первого и второго нагрузочных п-канальных транзисторов, затворы которых являются соответственно первым и вторым входами усилителя считывания, .истоки первого и второго нагрузочных п-канальных транзисторов соеди5 иены со стоком п-канального стробирующего транзистора, затвор которого соединен с шиной строба, исток с общей шиной, отл.ичающийс я тем, что, с целью уменьшения 0 потребляемой мощности усилителем,

он содержит два форсирующих п-каНальных транзистора и два установочных р-канальных транзистора, причем истоки форсирующих п-канальных тране зисторов соединены со стоком стробирующего транзистора, сток первого форсирующего п-канального транзистора соединен с затвором первого нагрузочного п-канального транзистора, а затвор - с выходом второго инвертирующего транзистора, сток второго форсирующего п-канального транзистора соединен с затвором второго нагрузочного п-канального транзистора, а затвор - с выходом первого инвертирующего транзистора, истоки первого и второго установочных р-канальных транзисторов соединены с шиной питания, затворы - с

шиной строба, стоки - соответственно со стоками первого и второго нагрузочных h -канальных транзисторов, исток стробирующего транзистора соединен с истоками первого и второго инвертирующих транзисторов и общей шиной.

Источники информации, принятые во внимание при экспертизе 1. Патент США 4136292, кл. 307-355, 1976. 2. Патент Англии 2018076, кл. G 011 С 7/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель считывания на КМДП-транзисторах для статических запоминающих устройств | 1987 |

|

SU1513513A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

Авторы

Даты

1983-03-15—Публикация

1981-12-08—Подача