СП

00

ел

со

3151

Изобретение относится к вычислительной технике и может быть использовано в статических з-апоминанлцих устройствах для усиления сигналов считывания информации.

Цель изобретения - уменьшение потребляемой мощности и упрощение усилителя считывания.

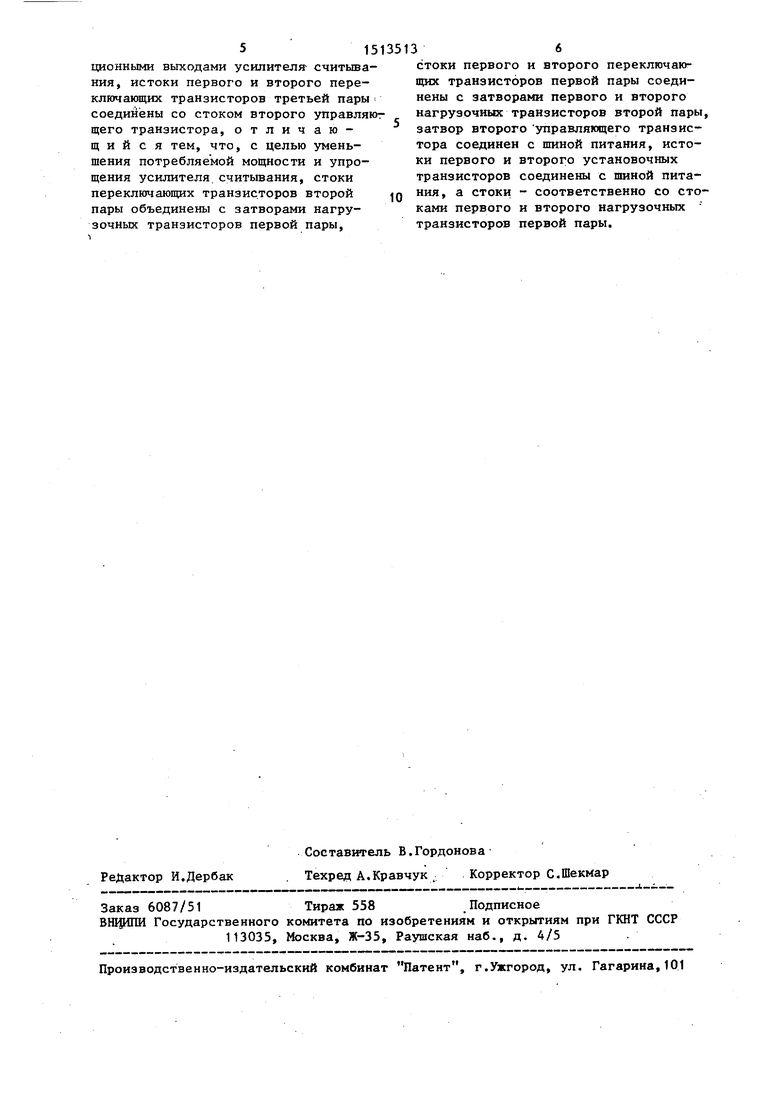

На чертеже представлена принци- Пиальная электрическая схема усилителя считывания.

Усилитель считывания содержит стробируклций транзистор 1 первого типа проводимости, первую 2 и 3, вторую 4 и 5 и третью 6 и 7 пары переключающих транзисторов первого типа проводимости, первую 8 и 9 и вторую 10 и 11 пары нагрузочных транзисторов второго типа проводимости, первый 12 и второй 13 управлякхцие транзис- торь второго и первого типов проводимости соответственно, первый 14 и Второй 15 установочные транзисторы второго типа проводимости, первый 16 и второй 17 информационные входы, первый 18 и второй 19 информационные выходы, управляющий вход 20, а также общую шину 21, шину 22 питания и - внутренние узлы 23-25 схемы.

Усилитель считывания работает -следующим образом,

В статическом режиме на управляющем входе 20 поддерживается напряжение, соответствукнцее логическому ну- лю. При этом стробируклций транзистор 1 закрыт, а установочные транзисторы 14 и 15 открыты, благодаря чему в узлах 23 и 24 устанавливается напряжение логической единицы. В результа те транзисторы 10 и 11 закрыты, а транзисторы 6, 7 и 13 открыты и на выходах 18 и 19 устанавливается напряжение логического нуля. Транзисторы 2-3 закрыты по истоку, транзистор 8, 9 и 12 - по затвору, в результате чего в узле 25 поддерживается напряжние в диапазоне от U „„ до „op р где и (,„ - напряжение источника питания, U(iop р пороговое напряжение транзистора второго типа проводимости. При этом в схеме отсутствует сквозное протекание тока, т,е, схема не потребляет мощности,

В режиме считывания на информационые входы 16 и 17 подается считывав- мый сигнал, а на управляющий вход 20 - напряжение логической единицы. Пусть для определенности напряжение

,

4

на входе 16 больше, чем на входе 17, В этом случае после переключения схемы напряжение в узле 23 меньше, чем в узле, 24, в результате чего на первом информационном выходе 18 устанавливается напряжение логического нуля, а на информационном выходе 19 - логической единицы.

Для обеспечения высокой чувствительности усилителя считывания необходимо, чтобы при считывании усилитель находился в рабочей -точке с максимальным усилением. Это достигается за счет соответствующего выбора размеров транзисторов.

Формула изобретения

Усилитель считывания на КМДП-тран- зисторах для статических запоминающих устройств, содержащий стробирующий транзистор первого типа проводимости, первую, вторую и третью пары переключающих транзисторов первого типа проводимости, первый и второй управляющие транзисторы соответственно второго и первого типов проводимости, причем исток стробирующего транзисо

тора соединен с истоком второго уп- равляклцего транзистора и общей шиной, сток - с истоками переключающих транзисторов первой и второй пар, стокгт первого и второго переключающих транзисторов первой пары соединены со стоками первого и второго нагрузочных транзисторов первой пары соответственно, затворы - с затворами первого и второго.переключающих транзисторов второй пары соответственно и являются первьш и вторым информационными входами усилителя считьтания, истоки нагрузочных транзисторов первой и второй пар соединены.с шиной питания и истоком первого управляющего транзистора, затвор которого объединен со стоком и соединен с затвором первого нагрузочного транзистора, первой пары и стоком первого переключа- ющего транзистора второй пары, затвор стробирующего транзистора соединен с затворами установочных транзисторов и является управляющим входом усилителя считывания, стоки первого и второго переключающих транзисторов третьей пары соединены со стоками первого и -второго нагрузочных транзисторов второй пары соответственно и являются первым и вторым информа515135136

ционными выходами усилителя- считыва-стоки первого и второго переклгочаюния, истоки первого и второго пере-щих транзисторов первой пары соедиключающих транзисторов третьей пары нены с затворами первого и второго

соединены со стоком второго управляютнагрузочных транзисторов второй пары,

щего транзистора, отличаю-затвор второго управляющего транзисщ и и с я тем, что, с целью умень-тора соединен с шиной питания, истошения потребляемой мощности и упро-ки первого и второго установочных

щения усилителя считывания, стокитранзисторов соединены с шиной питапереключающих транзисторов второй «пния, а стоки - соответственно со стопары объединены с затворами нагру-ками первого и второго нагрузочных

зочных транзисторов первой пары,транзисторов первой пары.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU1005185A1 |

| Усилитель считывания | 1986 |

|

SU1392592A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

Изобретение относится к вычислительной технике и может быть использовано в статических запоминающих устройствах для усиления сигналов считывания информации. Цель изобретения - уменьшение потребляемой мощности и упрощение усилителя считывания. Устройство содержит стробирующий транзистор 1 первого типа проводимости, первую 2, 3, вторую 4, 5 и третью 6, 7 пары переключающих транзисторов первого типа проводимости, первый 12 и второй 13 управляющие транзисторы второго и первого типов проводимости соответственно, первую 8, 9 и вторую 10, 11 пары нагрузочных транзисторов второго типа проводимости, первый 14 и второй 15 установочные транзисторы второго типа проводимости. 1 ил.

| Journal of Solid-State Circuits, IEEE, 1985, V.20, № 5, p.944, fig.8 | |||

| Journal of Solid-state Circuits, IEEE, 1984, V.19, № 6, p.1011, fig,7. |

Авторы

Даты

1989-10-07—Публикация

1987-12-30—Подача