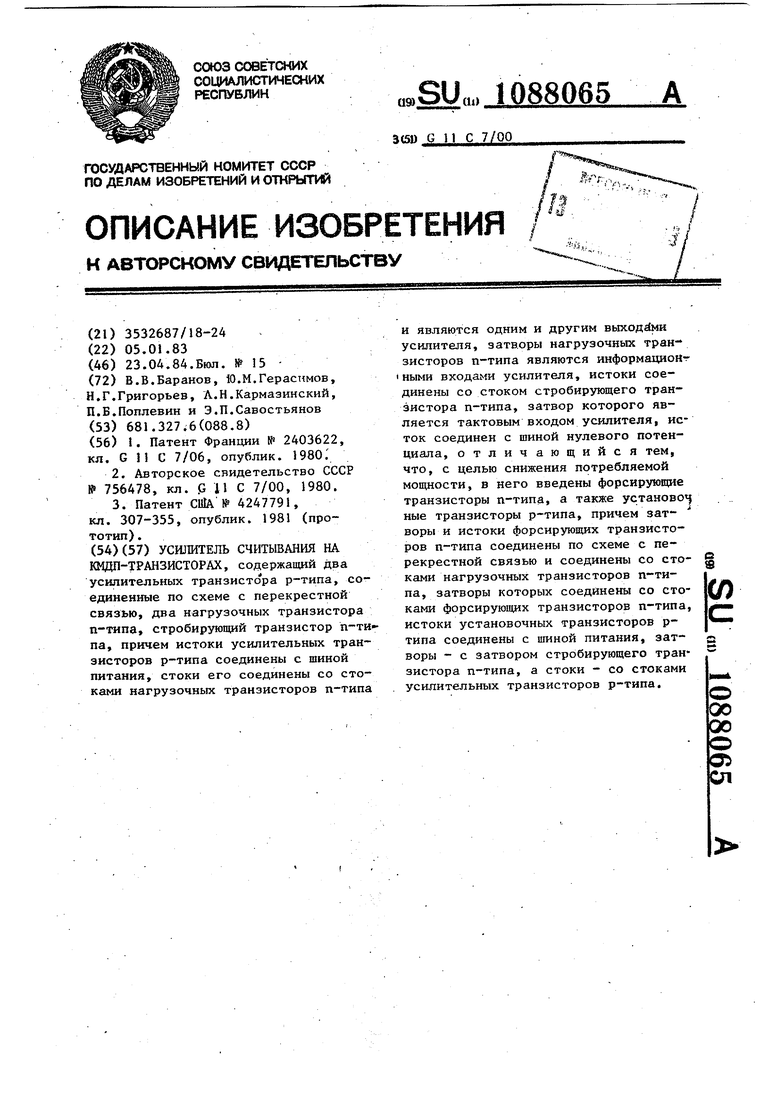

Изобретение относится к вычислительной технике и может быть использовано для усиления сигналов считьюа емой информации в запоминающих устро ствах на КМДИ-транзисторах. Известен усилитель считывания, содержащий первый и второй активные МДП-транзисторы, соединенные по схеме с перекрестной связью, первый и второй нагрузочные транзисторы, стро бирующий транзистор, две тактовые щи ны, шину питания, общзпо шину, первый и второй выходы, первую и вторую раз рядные шины а также три установочных транзистора, причем истоки активных транзисторов соединены со стоком стробирующего транзистора, затвор которого соединен с первой тактовой шиной, исток - с общей шиной, затворы первого и второго нагрузочных транзисторов соединены с первой и второй разрядными шинами соответственно, затворы установочных транзисторов соединены со второй так товой шиной I. Недостатком данного усилителя является большая потребляемая мощность обусловленная тем, что после переклкучения усилителя нагрузочные транзисторы остаются открытыми. Известен также усилитель считьшания на КЩЩ-траизисторах, содержащий первый и второй активные транзисторы первого типа проводимости, первый ивторой нагрузочные транзисторы вто рого типа проводимости, первый и вто рой стробирующие транзисторы второго типа проводимости, а также первый и второй установочные транзисторы первого типа проводимости, три тактовые шины, шину питания, общую шину, первый и второй выходы, первую и вто рую разрядные шины, причем истоки активных транзисторов соединены с общей шиной и истоками установочных транзисторов, стоки - со стоками нагрузочных транзисторов, которые соединены с выходами усилителя,- соединенными с разрядными шинами, первый и второй нагрузочные транзисторы соединены по схеме с перекрестной обратной связью, истоки стробирующих транзисторов соединены с шиной питания, затворы - с первой и второй так товыми шинами, стоки - с истоками первого и второго нагрузочных транзисторов, стоки первого и второго ус тановочных транзисторов соединены с первой и второй разрядными шинами соответственно, затворы - с третьей тактовой шиной С2 3. Недостатком этого усилители является низкое быстродействие, а также большая потребляемая мощность, обусловленная тем, что нагрузочные транзисторы значительное время находятся в открытом состоянии. Наиболее близким к изобретению является усилитель считывания на КМДПтранзисторах,содержащий первый и второй усилительные транзисторы р-типа, соединенные по схеме с перекрестной связью, первый и второй нагрузочные транзисторы п-типа, стробирующий транзистор п-типа, тактовую шину, шину питания,- общую шину, первый и второй выходы, первую и вторую разрядные шины, а также установоч ный транзистор п-типа, причем истоки первого и второго усилительных транзисторов р-типа соединены с шиной питания, стоки - с первым и вторым выходами соответственно, которые соединены со стоками первого и второго нагрузочных транзисторов птипа соответственно, затворы которых соединены с первой и второй разряд-г ными шинами соответственно, истоки со стоком стробирующего транзистора п-типа, затвор которого соединен с тактовой шиной, исток - с общей шиной, исток и сток установочного транзистора р-типа соединены с первым и вторым выходами усилителя соответственно, затвор - с тактовой шиной 13), Недостатком известного устройства является большая потребляемая мощность, обусловленная тем, что нагрузочные транз-исторы длительное время остаются открытыми из-за медленного разряда разрядных шин. Цель изобретения - снижение потребляемой мощности. Поставленная цель достигается тем, что в усилитель считывания на КЩПтранзисторах, содержащий два усили- тельных транзистора р-типа, соединенные по схеме с перекрестной связью, два нагрузочных транзистора п-типа, стробирующий транзистор п-типа, причем истоки усилительных транзисторов р-типа соединены с шиной питания, стоки соединены со стоками нагрузочных транзисторов п-типа и являются одним и другим выходами усилителя, затворы нагрузочных транзисторов п-типа являются информационными входами усилителя, истоки соединены со стоком стробирующего транэистора п-типа, эатйор которого являе1;ся тактовым входом усилителя, исток соединен с шиной нулевого потенциала, введены форсирующие транзисторы п-типа, а также установочные транзисторь р-типа, причем затворы и истоки форсирующих транзисторов п-типа соединены по схеме с перекрестной связью н соединены со стоками нагрузочных транзисторов п-типа, затворы которых соединены со стоками форсирующих транзисторов п-типа, ч истоки установочных транзисторов ртипа соединены с шиной питания, затворы - с затвором стробирующего тран зистора п-типа, а стоки - со стоками усилительных транзисторов р-типа. На чертеже дана принципиальная схема усилителя считьгоания. Усилительсчитывания содержит пер вый I и второй 2 усилительные транзи торы р-типа, соединенные по схеме с перекрестной связью, первый 3 и второй 4 нагрузочные транзисторы п-типа стробирующий транзистор 5 п-типа, та товую шину 6, шину питания 7, шину 8 нулевого потенциала, первый 9 и второй 10 выходы, первую 11 и вторую 12 разрядные шины, а 1акже первый 13 и второй 14 форсирующие транзисторы П-типа, первый 15 и второй 16 установочные транзисторы р-типа. Причем истоки усипительных транзисторов 1 и 2 соединены с шиной 7 питания, стоки - с первым 9 и вторым 10 выходами соответственно, которые сое динены со стоками первого 3 и второго 4 нагрузочных транзисторов соответственно, затворы которых соединены с первой и второй разрядными шинами II и 12 соответственно, истоки - со стоком стробирующего транзистора 5, затвор которого соединен с тактовой шиной 6, исток - с шиной нулевого потенцигша 8, затворы первого и второго форсирующих транзисторов 13 и 14 соединены со стоками первого 3 и второго 4 нагрузочных транзисторов соответственно, истоки со стоками второго 4 и первого 3 нагрузочных транзисторов соответственно, стоки - с затворами первого 3 и второго 4 нагрузочных транзисторов соответственно, истоки первого и вто рого установочных транзисторов 15 и 16 соединены с шиной 7 питания, стоки - с первым 9 и вторым 10 выхода654ми усилителя соответственно, затворы с тактовой шиной 6, Усилитель считывания работает следующим, образом. В статическом режиме на тактовой шине 6 и шине нулевого потенциала 8 поддерживаются потенциалы ЛОГИЧРСКОго нуля, а на ошне питания 7 и разряд ных шинах II и 12 - потенциалы логической единицы, при зтом транзисторы 15 и 16 открыты, остальные транзисторы закрыты. В результате на выходах 9 и 10 усилителя устанавливаются потенциалы логической единицы. Таким образом, с помощью установочных транзисторов 15 и 16 осуществляется установка потенциалов на выходах 9 и 10 до уровня логической едини1ц 1-. Форсирующие транзисторы 13 и 14 в данном режиме в работе не участвуют и остаются закрытыми. Б режиме считывания на разрядные шины 11 и 12 подается сигнал считывания, равный разности потенциалов зтих шин. Предположим для определенности, что потенциал разрядной шины 12 остается равным логической единице, а потенциал разрядной шины 11 начинает уменьшаться от уровня логической iединицы. Когда сигнал считывания ста|новится достаточным, чтобы скомпенсировать разбаланс плеч усилителя, обусловленный разбросом параметров транзисторов, подается сигнал логической единицы на тактовую шину 6. При зтом установочные транзисторы 15 и 16 закрываются, а стробирующий транзистор 5 и нагрузочные транзисторы 3 и 4 открываются. Потенциалы выходов 9 и 10 начинают уменьшаться. В схеме развивается регенеративный процесс, в результате которого на выходе 10 устанавливается потенциал логического нуля, а на выходе 9 - потенциал логической единицы. При зтом форсирующий транзистор 14 остается закрытым, а форсирующий Т4 анзистор 13 открывается, форсируя процесс уменьшения потенциала на разрядной шине И, в результате которого закрывается нагрузочный транзистор 3. Сравнительный анализ данного усилителя считывания с известным показывает, что введение форсирующих транзисторов дает снижение потребляемой мощности на порядок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU1005185A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Усилитель записи-считывания на КМДП-транзисторах | 1988 |

|

SU1571673A1 |

| Усилитель для считывания информации из блоков памяти | 1985 |

|

SU1283851A1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Усилитель записи-считывания для запоминающего устройства на дополняющих мдп-транзисторах | 1977 |

|

SU739643A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель считывания на КМДП-транзисторах для статических запоминающих устройств | 1987 |

|

SU1513513A1 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ НА КМДП-ТРАНЗИСТОРАХ, содержащий два усилительных транзистсзра р-типа, соединенные по схеме с перекрестной связью, два нагрузочных транзистора п-типа, стробируюп№1й транзистор п-типа, причем истоки усилительных транзисторов р-типа соединены с шиной питания, стоки его соединены со стоками нагрузочных транзисторов п-типа и являются одним и другим выходами усилителя, затв.оры нагрузочных тран- зисторов п-типа являются информациоНгными входами усилителя, истоки соединены со стоком стробирующего транзистора п-типа, затвор которого является тактовым входом усилителя, исток соединен с шиной нулевого потенциала, отличающийся тем, что, с целью снижения потребляемой мощности, в него введены форсирующие транзисторы п-типа, а также установо ные транзисторы р-типа, причем зат воры и истоки форсирующих транзисторов п-типа соединены по схеме с перекрестной связью и соединены со стоками нагрузочнь1х транзисторов п-ти(О па, затворы которых соединены со стоками форсирующих транзисторов п-типа, истоки установочных транзисторов ртипа соединены с шиной питания, затворы - с затвором стробирующего транзистора п-типа, а стоки - со стоками усилит€У1ьных транзисторов р-типа.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| КОРАБЕЛЬНЫЙ ОПТИКО-ЭЛЕКТРОННЫЙ ДАТЧИК | 2009 |

|

RU2403622C2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1984-04-23—Публикация

1983-01-05—Подача