IT

83ПП7

113

Изобретение относнгся к вычислительной технике и может быть использовано в запоминающих устройствах на КМДП-транзисторах для усиления сигналов считываемой информации.

Целью изобретения является повышение надежности усилителя считывания.

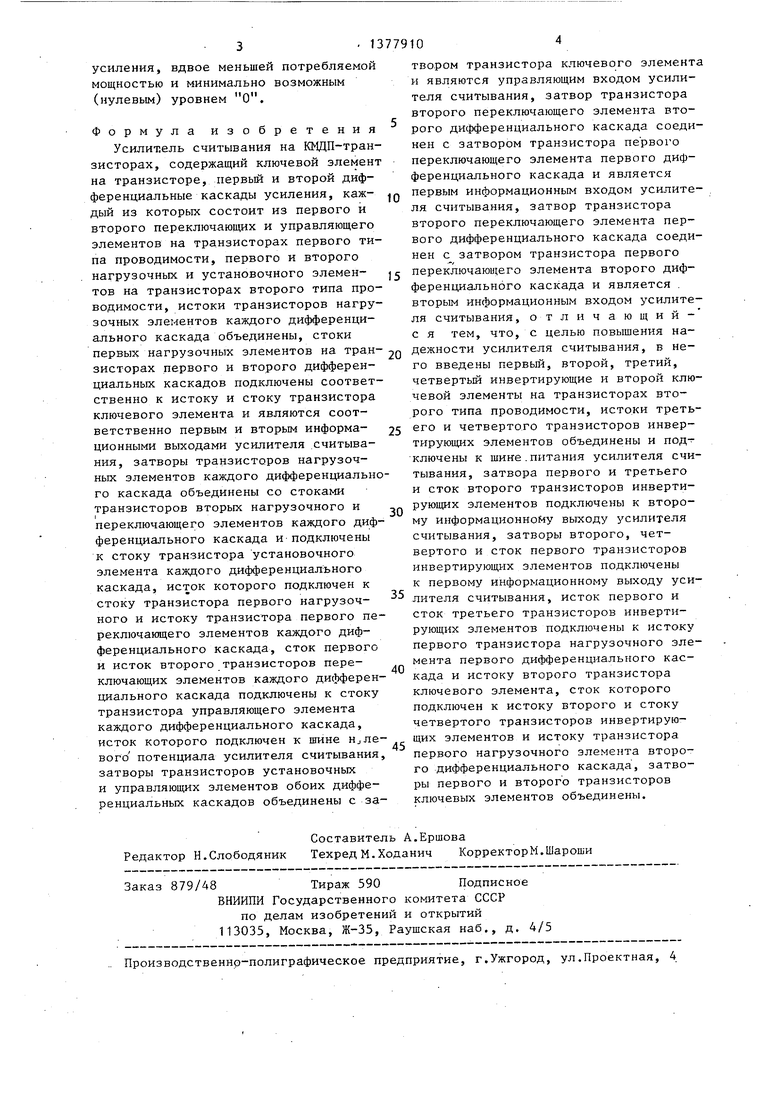

На чертеже представлена схема усилителя считывания.

Устройство содержит первый 1 и второй 2 дифференциальные каскады, каждый из которых состоит из транзисторов 3-5 первого типа проводимости - управляющего, первого и второго Переключающих элементов, транзисторов 6-8 второго типа про- вод -1мости - установочного, первого и второго н агрузочных элементов, шину нулевого потенциала, первый 10 и вто- рой 11 информационные входы, первый 12 и второй 13 информационные выходы первый ключевой элемент 14 на транзисторе второго типа проводимости, управляющий вход 15, первый - четвер- тый инвертирующие и второй ключевой элементы на транзисторах 16-20 второго типа проводимости, шину 21 питания.

Принцип действия усилителя считы- вания заключается в следующем.

В статическом режиме на входе 15 поддерживается напряжение О, а на входах 10 и 11 - напряжения, соответ

ствующие произвольной информации. При этом транзисторы 3 закрыты, а транзисторы 6, 14, 20 открыты, в результате чего на выходах 12 и 13 и истоках транзисторов 7 и 8 каскадов 1,2 установлены одинаковые напряжения, лежащие в диапазоне от 4° .где поРР -напряжение питания и пороговое напряжение транзисторов второго типа проводимости.. В активном режиме, т.е. в режиме считывания информации, на вход 15 подается напряжение 1, а на входы 10 и 11 - напряжения, соответствующие считываемой информации. Пусть для определенности U - напряжение на входе 10, а Ug напряжение на входе 11 и и „у Uovn Тогда после пеР t ол л

реключения усилителя на выходе усилителя 12 устанавливается низкий уровень напряжения U°, а на. выходе 13 - высокий уровень напряжения U . Причем размеры транзисторов в схеме выбираются такими, что обеспечивается условие и (jpp . В результате

0

2

транзисторы 16, 18 после переключения усилителя оказываются закрытыми, т.е. исключается протекание тока через каскад 1. Поскольку транзисторы 3-5 каскада 1 открыты по затвору, то- напряжение на выходе 12 оказывается равным напряжению шины 9, т.е. . В прототипе ток после переключения усилителя протекает через оба каскада, т.е. через усилитель протекает вдвое больший ток, а уровень О при малом входном.сигнале (U - ,U) определяется формулой

-Un

ОРП

1 + 1,

где и

ПОРП

пороговое напряжение транзисторов первого типа проводимости; коэффициент влияния подложки этих транзисторов,

8м - 1 «Ч 1,0 составляет значительную величину.

что при и.

равную ,5-2,0 В. Транзисторы 16 - 19 включены по схеме с положительной обратной связью, что приводит к увеличению коэффициента усиления по сравнению с прототипом в К раз, где U -U

О

5

5

1 - «ш8.1-/liji jn - 12: V k t+nn- 1

нагр

((1tfi)

нагр

-1).

где W

ИН81

и W

ИН82

0

W.

Harp

5

0

К

k; и k;

что при К -15;

W.

ширина каналов транзисторов 16 - 19 соответственно;ширина канала транзисторов 7 и 8;

коэффициенты влияния подложки транзисторов первого и второго типа проводимости;

коэффициент усиления прототипа; удельные крутизны транзисторов 3, 4 и 7,8, 0,05;

/Т.1

НЧГР

0,1 и W,,,,/W,

и и и а 1- Р

П( .1 и иий2

0,5 - 1,0 составляет ,0-5,5.

По сравнению с прототипом предлагаемый усилитель обладает в 5,0- 5,5 раза более высоким коэффициентом

усиления, вдвое меньшей потребляемой мощностью и минимально возможным (нулевым) уровнем О.

Формула изобретения Усилитель считывания на КМДП-тран- зисторах, содержащий ключевой элемент на транзисторе, первьй и второй дифференциальные каскады усиления, каждый из которых состоит из первого и второго переключающих и управляющего элементов на транзисторах первого типа проводимости, первого и второго нагрузочных и установочного элементов на транзисторах второго типа проводимости, истоки транзисторов нагрузочных элементов каждого дифференциального каскада объединены, стоки

твором транзистора ключевого элемента и являются управляющим входом усилителя считывания, затвор транзистора второго переключающего элемента второго дифференциального каскада соединен с затвором транзистора первого переключающего элемента первого дифференциального каскада и является первым информационным входом усилителя считывания, затвор транзистора второго переключающего элемента первого дифференциального каскада соединен с затвором транзистора первого переключающего элемента второго дифференциального каскада и является . вторым информационным входом усилителя считывания, отличающий- с я тем, что, с целью повышения на

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель считывания на КМДП - транзисторах | 1986 |

|

SU1348904A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Усилитель считывания на КМДП-транзисторах для статических запоминающих устройств | 1987 |

|

SU1513513A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на КМДП-транзисторах. Цель изобретения - повышение надежности усилителя считывания. Поставленная цель осуществляется за счет введения инверти944, - слильтееля щеирующих транзисторов, образующих положительную обратную связь, увеличивающую коэффициент усиления, а также приводящую к запиранию одного из инвертирующих транзисторов, за счет чего исключается протекание тока через соответствующий дифференциальный каскад усилителя, следовательно, уменьшаются потребляемая мощность и уровень логического нуля усилителя. Устройство содержит дифференциальные каскады 1, 2, каждый из которых состоит из транзисторов 3, 4, 5 первого типа проводимости - управляющего, первого и второгЬ переключающих элементов, транзисторов 6,7,8 второго типа проводимостей - установочного, первого и второго нагрузочных элементов, ключевые элементы 14, 20 на транзисторах второго типа проводимости, четыре инвертирующих элемента 16 - 19 на транзисторах второго типа проводимости, 1 ил. (Л

первых нагрузочных элементов на тран- 2Q дежности усилителя считывания, в не25

зисторах первого и второго дифференциальных каскадов подключены соответственно к истоку и стоку транзистора ключевого элемента и являются соответственно первым и BTOpbiM информационными выходами усилителя считывания, затворы транзисторов нагрузочных элементов каждого дифференциального каскада объединены со стоками транзисторов вторых нагрузочного и ,« переключающего элементов каждого дифференциального каскада и подключены к стоку транзистора установочного элемента каждого дифференциального каскада, исток которого подключен к стоку транзистора первого нагрузочного и истоку транзистора первого переключающего элементов каждого дифференциального каскада, сток первого и исток второго транзисторов переключающих элементов каждого дифференциального каскада подключены к стоку транзистора управляющего элемента каждого дифференциального каскада, исток которого подключен к шине HJлевого потенциала усилителя считывания, затворы транзисторов установочных и управляющих элементов обоих дифференциальных каскадов объединены с за35

40

45

го введены первьш, второй, третий, четвертый инвертирующие и второй клю чевой элементы на транзисторах второго типа проводимости, истоки треть его и четвертого транзисторов инвертирующих элементов объединены и подключены к шике.питания усилителя счи тывания, затвора первого и третьего и сток второго транзисторов инвертирующих элементов подключены к второму информационному выходу усилителя считывания, затворы второго, четвертого и сток первого транзисторов инвертирующих элементов подключены к первому информационному выходу уси лителя считывания, исток первого и сток третьего транзисторов инвертирующих элементов подключены к истоку первого транзистора нагрузочного эле мента первого дифференциального каскада и истоку второго транзистора ключевого элемента, сток которого подключен к истоку второго и стоку четвертого транзисторов инвертирующих элементов и истоку транзистора первого нагрузочного элемента второго дифференциального каскада, затворы первого и второго транзисторов ключевых элементов объединены.

5

«

5

0

5

го введены первьш, второй, третий, четвертый инвертирующие и второй ключевой элементы на транзисторах второго типа проводимости, истоки третьего и четвертого транзисторов инвертирующих элементов объединены и подключены к шике.питания усилителя считывания, затвора первого и третьего и сток второго транзисторов инвертирующих элементов подключены к второму информационному выходу усилителя считывания, затворы второго, четвертого и сток первого транзисторов инвертирующих элементов подключены к первому информационному выходу усилителя считывания, исток первого и сток третьего транзисторов инвертирующих элементов подключены к истоку первого транзистора нагрузочного элемента первого дифференциального каскада и истоку второго транзистора ключевого элемента, сток которого подключен к истоку второго и стоку четвертого транзисторов инвертирующих элементов и истоку транзистора первого нагрузочного элемента второго дифференциального каскада, затворы первого и второго транзисторов ключевых элементов объединены.

| УСТРОЙСТВО ДЛЯ ЗАТИРКИ И ЗАГЛАЖИВАНИЯ ПОВЕРХНОСТЕЙ | 1993 |

|

RU2100542C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| IEEE Journal of Solid-State Circuits, 1985, vol | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-02-28—Публикация

1986-09-17—Подача