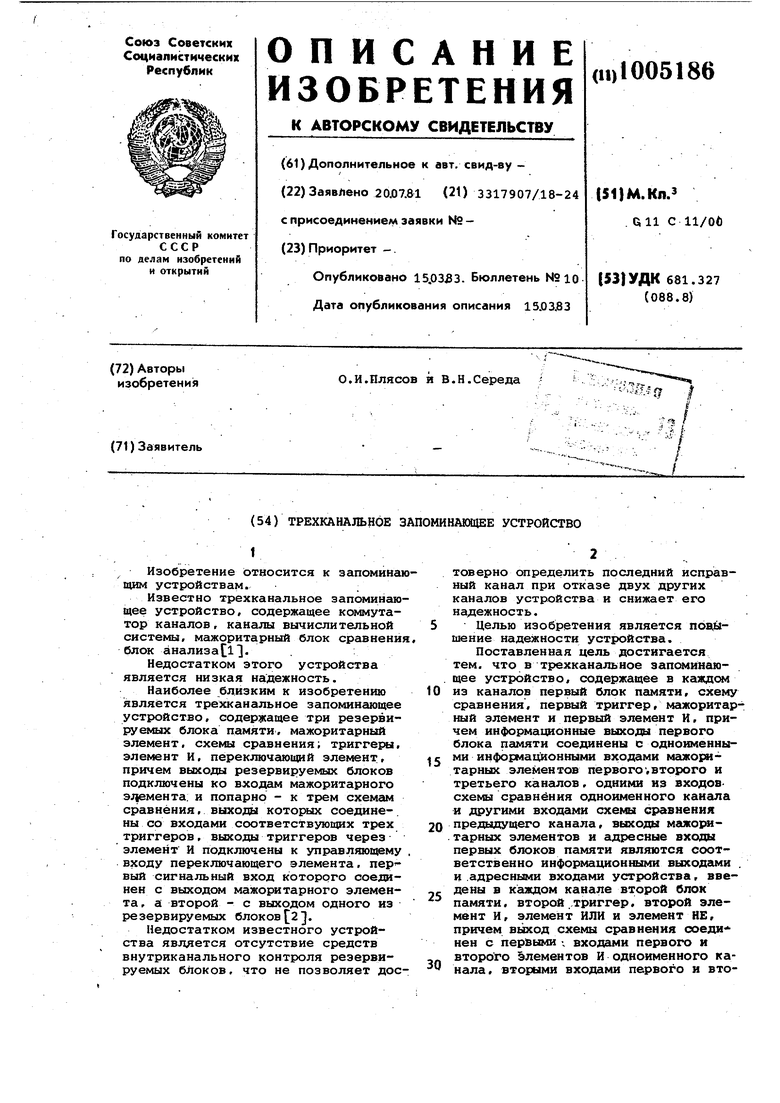

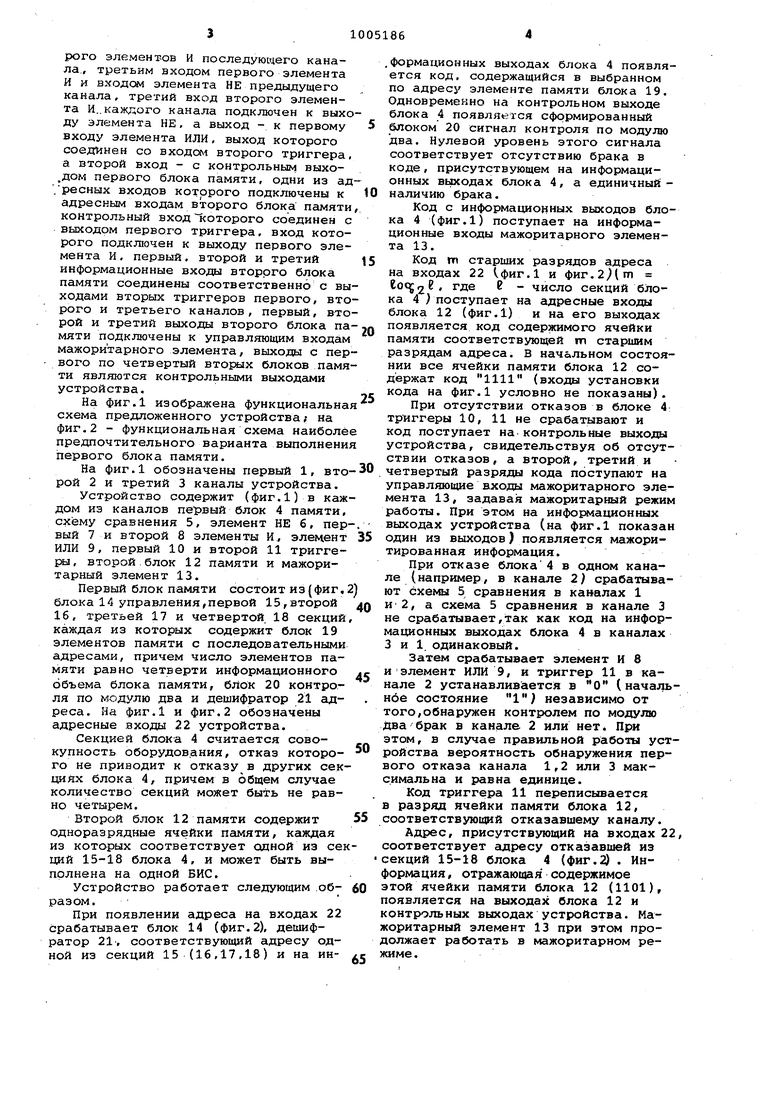

рого элементов И последующего канала., третьим входом первого элемента И и входом элемента НЕ предыдущего канала, третий вход второго элемента И..каждого канала подключен к выхо ду элемента НЕ, а выход - к первому входу элемента ИЛИ, выход которого соедтинен со входе второго триггера, а второй вход - с контрольным выхо.дом первого блока памяти, одни из ад .ресных входов которого подключены к адресным входам второго блока памяти контрольный вход которого соединен с выходом первого триггера, вход которого подкл очен к выходу первого элемента И. первый, второй и третий информационные входы второго блока памяти соединены соответственно с вы ходами вторых триггеров первого, вто рого и третьего каналов, первый, вто рой и третий выходы второго блока па мяти подключены к управляющим входам мажоритарного элемента, выходы с пер вого по четвертый вторых блоков памя ти являются контрольными выходами устройства. На фиг.1 изображена функциональна схема предложенного устройства; на фиг.2 - функциональная схема наиболе предпочтительного варианта выполнени первого блока памяти. На фиг.1 обозначены первый 1, вто рой 2 и третий 3 каналы устройства. Устройство содержит (фиг.1) в каж дом из каналов первый блок 4 памяти, схему сравнения 5, элемент НЕ б, пер вый 7 и второй 8 элементы И, элемент ИЛИ 9, первый 10 и второй 11 триггера, второй.блок 12 памяти и мажоритарный элемент 13. Первый блок памяти состоит из {фиг, блока 14 управления,первой 15,второй 16, третьей 17 и четвертой 18 секций каждая из которых содержит блок 19 элементов памяти с последовательными адресами, причем число элементов памяти равно четверти информационного объема блока памяти, блок 20 контроля по модулю два и дешифратор 21 адреса. На фиг.1 и фиг.2 обозначены адресные входы 22 устройства. Секцией блока 4 считается совокупность оборудования, отказ которо го не приводит к отказу в других сек циях блока 4, причем в общем случае количество секций может быть не равно четырем. Второй блок 12 памяти содержит одноразрядные ячейки памяти, каждая из которых соответствует одной из сек ций 15-18 блока 4, и может быть выполнена на одной БИС. Устройство работает следующим .образом. При появлении адреса на входах 22 срабатывает блок 14 (фиг.2), дешифратор 21-, соответствующий адресу одной из секций 15 (16,17,18) и на информационных выходах блока 4 появляется код, содержащийся в выбранном по адресу элементе памяти блока 19. Одновременно на контрольном выходе блока 4 появляется сформированный блоком 20 сигнал контроля по модулю два. Нулевой уровень этого сигнала соответствует отсутствию брака в коде, присутствующем на информационных вьЕходах блока 4, а единичныйналичию брака. Код с информационных выходов блока 4 (фиг.1) поступает на информационные входы мажоритарного элемента 13. Код m старших разрядов адреса на входах 22 .фиг.1 и фиг.2Лт где К - число секций блока 4 } поступает на адресные входы блока 12 (фиг.1) и на его выходах появляется код содержимого ячейки памяти соответствующей m старшим разрядам адреса. В начальном состоянии все ячейки памяти блока 12 содержат код 1111 (входы установки кода на фиг.1 условно не показаны). При отсутствии отказов в блоке 4 триггеры 10, 11 не срабатывают и код поступает на-контрольные выходы устройства, свидетельствуя об отсутствии отказов, а второй, третий и четвертый разряды кода поступают на управляющие входы мажоритарного элемента 13, задавая мажоритарный режим работы. При этом на информационных выходах устройства (на фиг.1 показан один из выходов) появляется мажоритированная информация. При отказе блока 4 в одном канале (например, в канапе 2) срабатывают схемы 5 сравнения в каналах 1 и-2, а схема 5 сравнения в канале 3 не срабатывает,так как код на информационных выходах блока 4 в каналах 3 и 1 одинаковый. Затем срабатывает элемент И 8 и элемент ИЛИ 9, и триггер 11 в канале 2 устанавливается в О (начальное состояние 1 независимо от того,обнаружен контролем по модулю два брак в канале 2 или нет. При этом, в случае правильной работы устройства вероятность обнаружения первого отказа канала 1,2 или 3 максимальна и равна единице. Код триггера 11 переписывается в разряд ячейки памяти блока 12, соответствующий отказавшему каналу. Адрес, присутствующий иа входах 22, соответствует адресу отказавшей из секций 15-18 блока 4 (фиг.2) . Информа ция, отражающа я содержимое этой ячейки памяти блока 12 (1101), появляется на выходах блока 12 и контрольных выходах устройства. Мажоритарный элемент 13 при этом продолжает работать в мажоритарном режиме .

Аналогичные процессы происходят при отказе блока 4 одного- из каналов 1 или 3.

При отказе блока 4 в двух из каналов 1,2,3 информация первого отказавшего канала может быть искажена или соответствовать правильной. Последнее происходит, например, в случае отказа информационного разряда блока 4 в одном из каналов 1,2,3 при случайном (с вероятностью 0,5) совпадении его значения с правильным значением. При этом обнаружение второго отказа производится схемами сравнения. При искажении информации обоих отказавших каналов схемы 5 сравнения и элементы И 7 щсех трех каналов 1,2;3 срабатывают, в триггер 10 и первый разряд блока 12 записывается О (начальное состояние триггера 10 - 1) , триггер 11 второго отказавшего из каналов 1,2,3 срабатывает при обнаружении отказа в нем контролем по модулю два. .

Например, если отказали одноименные из секции 15-18 (фиг.2) каналов 1 и 2 (фиг.1) то выходные коды блоков 12 будут 1001 или 0001, и мажоритарные элементы 13 перестраиваются на выдачу кода последней исправной из секций 15-18 (фиг.2) блока 4 третьего канала 3. При обнаружений отказа в блоке 4(,фиг.1 последнего (третьего) канала 3, например, выходной код блока 12 будет 10 00 или 0000, и мажоритарный элемент 13 перестраивается на работу в мажоритарном режиме.

Это позволяет, в случае отказа разноименных информационных разрядов блоков 4 в трех каналах 1,2 и 3 сформировать правильную информацию на выходе мажоритарного элемента 13

Таким образом, повышение надежности устройства достигается за счет обеспечения работоспособности устройства при максимальном числе отказов с различными вариантами распреде е ния отказов по секциям 15-18 (фиг.2) блоков 4 (фиг.1).

.Технико-экономическое преимущество предложенного устройства заключается в его более высокой надежности по сравнению с прототипом. Формула изобретения

Трехканальное запоминающее устройство, содержащее в каждом из каналов

первый блок памяти, схему сравнения, первый триггер, мажоритарный элемен.т и первый элемент И, причем информационные выходы первого блока памяти соединены с одноименными информационными входами мажоритарных элементов первого/ второго и третьего каналов, одними из входов схемы сравнения одноименного канала и другими входами схемы сравнения предыдущего кана0ла, выходы мажоритарных элементов и адресные входы первых блоков памяти являются соответственно информационными выходами и адресными входами устройства, отличающееся тем,

5 что, с целью повышения надежности устройства, в него введены в каждом канале второй бЛок памяти, второй триггер, второй элемент И, элемент ИЛИ и элемент НЕ, причем выход схемы сравнения соединен с первыми вхо0дами первого и второго элементов И одноименного канала, вторыми входами первого и второго элементов И последующего канала,третьим входом первого элемента И и входом элемен5та НЕ предыдущего канала, третий вход второго элемента И каждого канала подключен к выходу элемента НЕ, а выход - к первому входу элемента ИЛИ, выход которого соединен с вхо0дом второго триггера, а второй входс контрольным выходом первого блока памяти, одни из адресных входов которого подключены к адресным входам второго блока памяти, контрольный

5 вход которого соединен с выходсии первого триггера, вход которого подключен к выходу первого элемента И, первый, второй и третий инфо)мационные входы второго блока

0 памяти соединены соответственно с выходами вторых триггеров первого, второго и третьего каналов, первый второй и третий выходы второго блока памяти подключены к управляющим

5 входам мажоритарного элемента, выходы с первого по четвертый вторых блоков памяти являются котрольными выходами устройства.

Источники информации,

0 принятые во внимание при экспертизе

1.Авторское свидехельство СССР 383047, кл. G 06 F 9/00,: 1971.

2.Авторское свидетельство СССР

5 318919, кл. 05 В 23/00. .2

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-20—Подача