(54) КВАДРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1983 |

|

SU1092501A1 |

| Квадратор | 1981 |

|

SU1010620A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU928347A1 |

| Аналого-цифровой квадратор | 1983 |

|

SU1120374A1 |

| Цифровой функциональный преобразователь | 1978 |

|

SU742951A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

1

Изобретение относится, к вычислительной технике и может быть использовано в в (Специализированных ци(}ровых вычислительных машинах.

Известны устройства для возведения в квадрат числоимпульсных кодов Lij и 2 .

Недостатком данных устройств является низкое быстродействие. Например, в 2 каждое приращение квадрата с юрми- ,д руется в числоимпульсном коде, что обусловливает воегфоизведение функции у х за время Т .2.-t , где t период частоты представления числокмпульсного кода.

Наиболее близкий к гфедлагаемому квадратор 2 содержит счетчик, элеменгг задержки, ключи и сумматор.

Квадратор {i реализует алгоритм

y..,.6.(1)

х(.б)0

где .i - О, ч - номер итерации;

8 ( - приращение аргумента.

Быстродействие алгоритма (1) определяется формулой

ПрОТ npOT.niOD.2

где t - период частоты следования импульсов приращения гументаХ,

Низкое бысггродействие квадратора 2j обусловлено неполным использованием функциональных возможностей сумматора.

Цель изобретения - повьшение быстродействия квадратора.

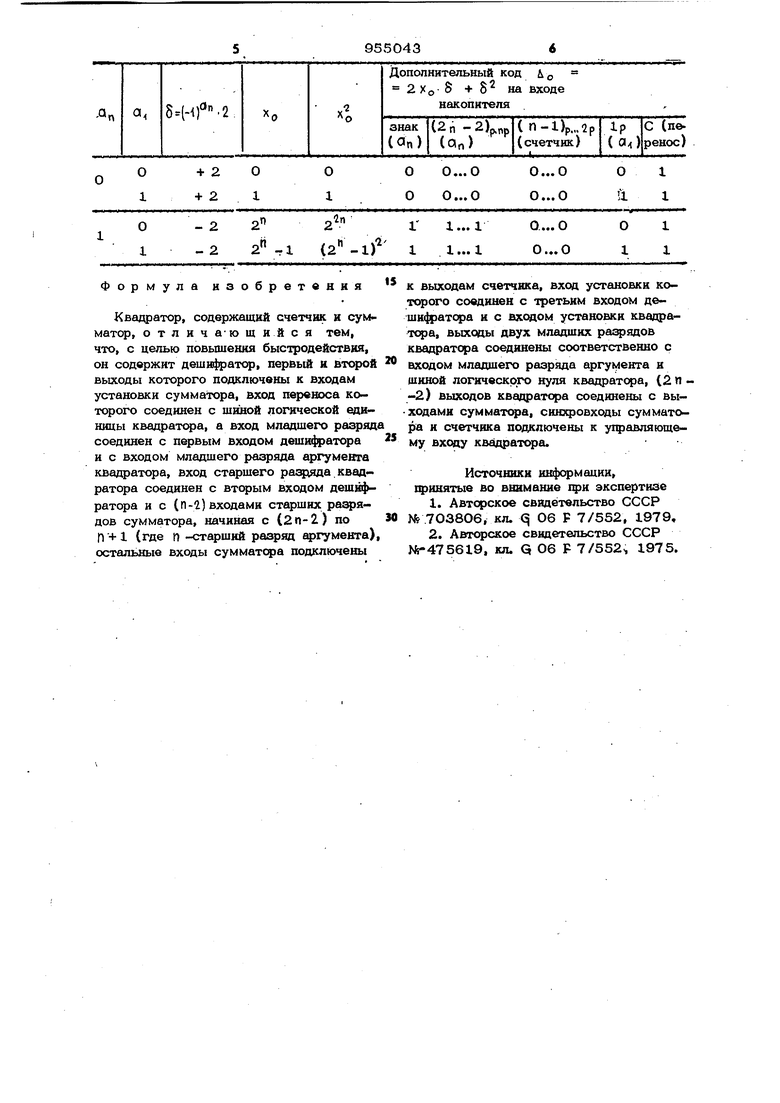

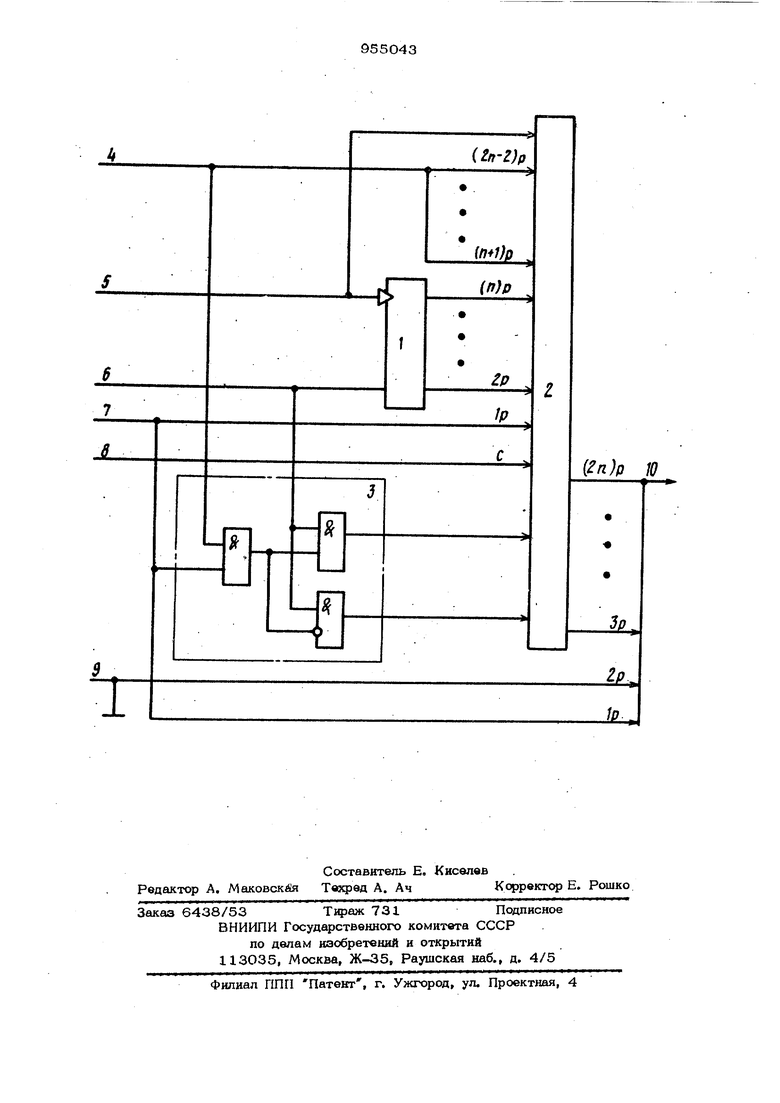

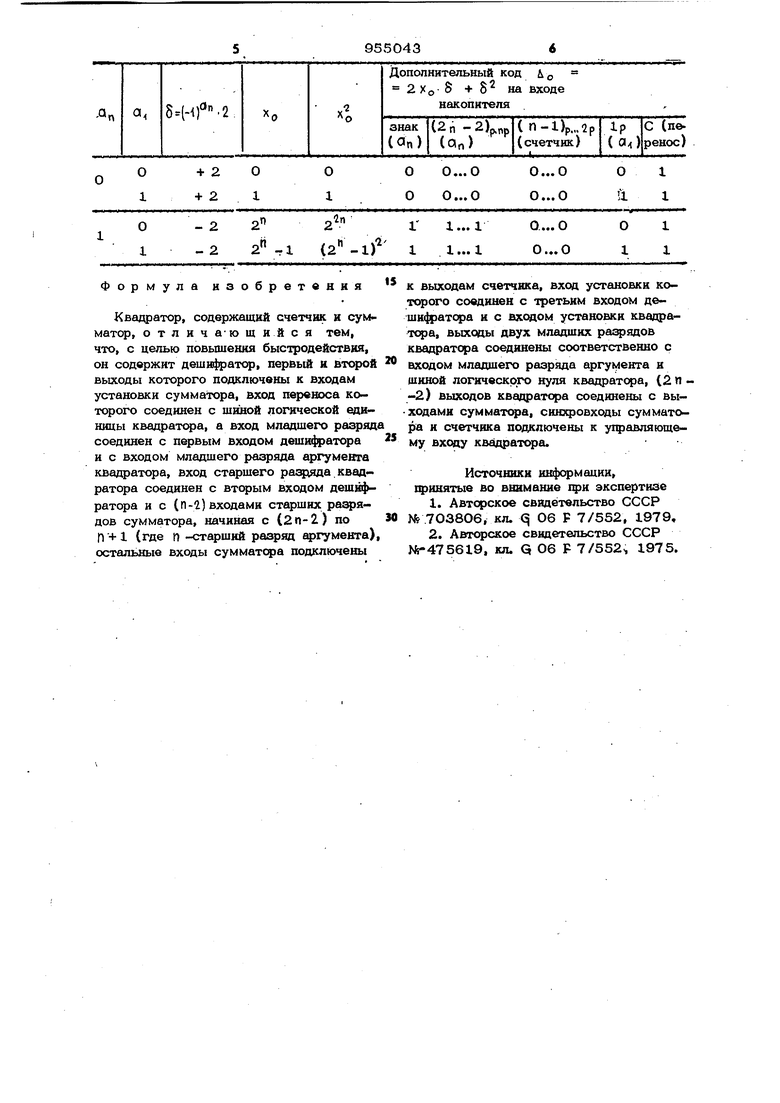

Поставленная цель достигается тем, что квадратор, содержащий счетчик и сумматор, содержит дещи(, первый и второй выходы которого подключены к входам установки сумматора, вход переноса которого соединен с щиной логической единицы квадратора, а вход младшего разряда соединен с первым входом дешифратора и с входом младшего разряда аргумента квадратора, вход старшего . разряда аргумента квадратора соединен с вторым входом деши(|рратора и с ( п-2) входами старших разрядрв сумматора. 3Q начиная с (2п-2) по п +1 (где п - ста ший разряд аргумента), остальные входы сумматора подключены к выходам счетчика, вход установки которого соединен с третьим входом деши(|ратора и с входом установки квадратора, выходы двух младших разрядов квадратора соединены соответственно с входом младшего разр аргумента и шиной логического нуля квадратора, (2 ) выходов квадратора соединены с выходами сумматора, синхровходы сумматора и счетчика подключены к управляющему входу квадратора. На чертеже представлена блок-схема устройства. . Квадратор содержит счетчик 1, сумматор 2, дещи(}ратор 3, вход 4 старшего разряда аргумента, тактовый вход 5, вход 6 установки квадратора, вход 7 младщего разряда аргумента, шину 8 лргической единицы, шину 9 логического fjyna и вь.1ход 10 квадратора. Предлагаемый квадратор реализует алгоритм (1) при: iH.1,..., где sign 5 () - знак приращения аргу мента , 0(п -разрядная цифра старшего разр5зда аргумен та х.. Квадратор работает циклически. Перед началом каждого цикла в сумматор 2 заносится начальная установка условия вычисления. Цикл начинается с поступления на вход 6 импульса установки квадратора. В течение каждого циКла на входы 4 и 7 подаются логические сигналы п 0(1 и 4-7 0 , определяемые разрядными цифрами соответственно старшего { а п ) и младщего ( а ) разрядов кода аргумента х. По каждому импульсу установки квадратора счетчик 1 устанавливается в О, а в сумматор 2 в зависимости от а п и 01 заносится код началь ных условий вычислений в соответствии с таблицей. Вес младшего разряда сумматора по входу (выходу) равен 4, поэтому в сумматор заносятся старшие 211-2 разряда (прих: 2 в сумматор 2 кода Х5 34 занЬсятся все нули, т.е. переполнение сумматора не фиксируется, так как это не влияет на результат вычислений). По содержимому счетчика 1 и значениям а и 0(1 формируется дополнительный код -х , а по. значению переноса С и дополнительному коду - дополнительный код Д , , поступающий на вход сумматора. Знак каждого из кодов определяется значением Q п- После окончания импульса установки квадратсфа на счетный вход счетчика I и тактовый вход сум иатора поступают с входа 5 импульсы приращений ( S ). .В момент окончания каждого импульса содержимое счетчика 1 увеличивается на . единицу младшего разряда (т.е. аргумент изменяется, соответственно, на S ), а содержимое сумматора 2 на А 2х .8 + 6. После окончания N -го импульса ( S ) с выходов Ю можно снимать код, равный X , до гфихода следующего импульса установки квадратора. Из описанного следует, что число импульсов (6 ) определяется выражением ,а„и%).а,.с| Время вычисления функции (l) опреде ляется выражением ап12 -х)+5п-х1,„п-2.„(5) ii|. max. Сравнивая вьфажения (4) .и (5), полу г прот.тах Таким образом, быстродействие предагаемого квадратора (см. оценку (б) вьше, чем прототипа. При этом его счетчик и сумматор проще, так как .счетчик имеет разность ( п -l), а сумматор (2п -2) (выход младшего разряда квадатора определяется младшим разрядом аргумента, а второй разряд при возвеении в квадрат любого числа всегда одержит нуль). Технико-экономическая эффективность зобретения заключается в том, что зедлагаемый квадратор не сложнее проотипа, но имеет более высокое быстроействие. Формула изобретения Квадратор, содержащий счетчик и сумматор, отлича-ющийся тем, что, с целью повышения быстродействия, он содержит дешифратор, первый и второй выходы которого подключены к входам установки сумматора, вход переноса которого соединен с шиной логической единицы квадратора, а вход младшего разряд соединен с первым входом дешифратора и с входом младшего разряда аргумента квадратора, вход старшего квадратора соединен с вторым входом деш1фратора и с (п-2) входами старших разрядов сумматора, начиная с {2п-2) по П+ 1 (где Г) -старший разряд аргумента) остальные входы сумматс5 а подключены к выходам счетчика, вход установки которого соединен с третьим входом дешифратора и с входом установки квадрат а, выходы двух младших разрядов квадратора соединены соответственно с входом младшего paapsma аргумента и шиной логического нуля квадратора, (2 п -2) выходов квадратора соединены с выходами сумматора, сиюфовходы сумматора и счетчика подключены к ущзавляющему входу квадратора. Источники информации, 1финятые во внимание 1фи экспертизе 1.Авторское свидетельство СССР № 703806, кл. q 06 F 7/552, 1979, 2.Авторское свидетельство СССР Nr47 5619. кл. Q 06 F 7/552 1975.

Авторы

Даты

1982-08-30—Публикация

1980-12-10—Подача