6

02 6-4-

DO

7

О

Фиг.|

Иэо&ретение относится к вычислительной технике и элект ронИке и может быть использовано при построении микромощных интегральных запоминающих устройст (ЗУ), на дополняющих МДП-транзистор

Известны ячейки для построения параллельного дешифратора на одноканальных МДп-транзисторах статического и динамического типа, представляющие собой логические элементы ИЛИ-НЕ или И-НЕ, состоящие из параллельной группы транзисторов и нагрузочного транзистора, на отношение размеров которых наложено ограничение 2. Однако дешифраторы п6строенные на основе таких ячеек, потребляют значительную мощность в статическом режиме и непригодны для ЗУ на дополняющих МДП-транзисторах.

Наиболее близкой к изобретению является ячейка параллельного дешифратора, содержащая квазистатический логическ йй элемент ИЛИНЕ (И-НЕ) с информационными и управляющими входами, логический элемент И .с задержкой, в которой выход квазистати1еского элемента ИЛИ-НЕ подключен к первому входу оэлемента И-НЕ, а его первый управ.ляющий вход - к выходу элемента И-НЕ, второй управляющий вход соединен с вторым входом элемента И, и с задержкой подключен к второй шине управлений, первый выход.логического элемента И с задержкой подключен к первой шине управле ния, а выход этого элемента - к втрому входу логического элемента И-НЕ. На шины питания всех элементов ячейки подаются постоянные потенциалы 3.

Недостатком известной ячейки параллельного дешифратора является наличие ограничений на фазовые соотношения ме.жду сигн алами на управляющих входах, а так- . ,же на величину задержки сигнала И, в результате чего снижается быстро .действие дешифратора и процент выхода годных. Кроме того, известная схема параллельного дешифратора критична к разбросу параметров транзисторов, в результате чего она имеет.небольшой диапазон работоспособности при воздействии разлных дестабилизирующих факторов. Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в параллельный дешифратор содержащий квазистатический элемент ИЛИ-НЕ, выход которого соединен .с первым управляю1аим входом элемента ИЛИ-НЕ и является выходом .дешифратора, второй управляк«ций вход элемента ИЛИ-НЕ является управдяющим входом дешифратора, информационные входы элемента ИЛИ-, НЕ являются информационными входами дешифратора, введены первый и второй инверторы, причем вход первого инвертора соединен с вторым управляющим входом элемента ИЛИ-НЕ, тр.етий управляющий вход которого соединен с выходом первого инвертора и входом второго инвертора, вход которого соединен, с вторым входом элемента И-НЕ.

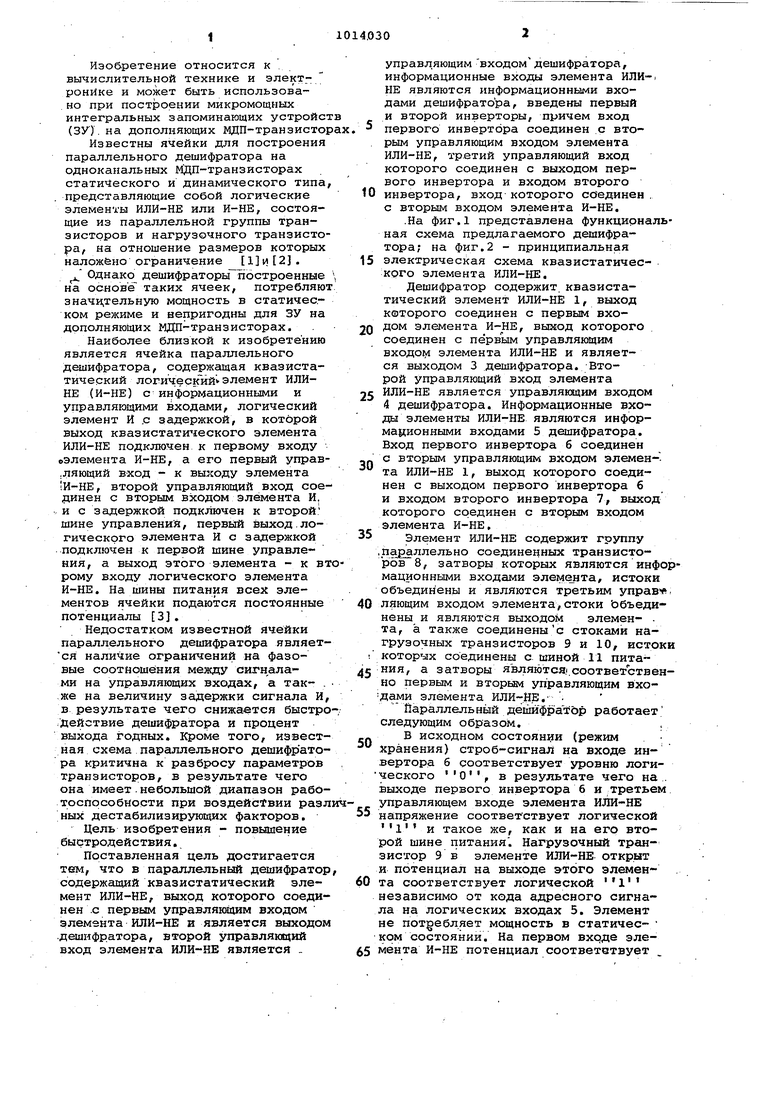

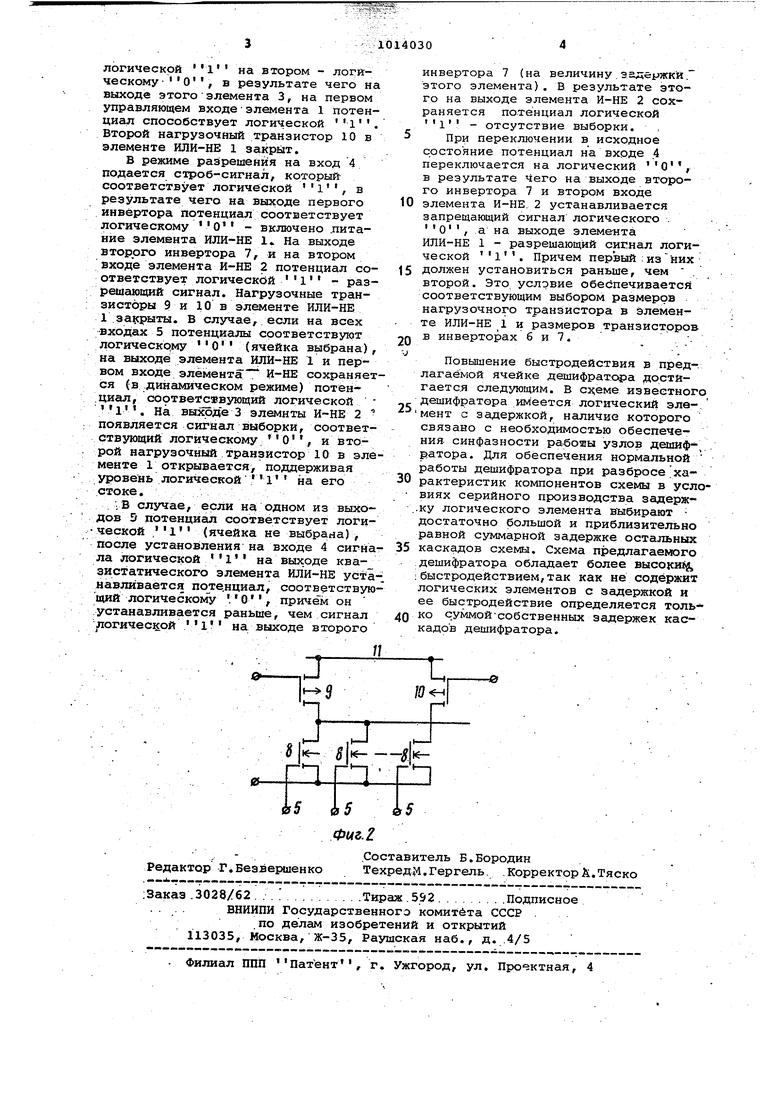

.На фиг.1 представлена функционалная схема предлагаемого дешифратора; на фиг.2 - принципиальная электрическая схема квазистатического элемента ИЛИ-НЕ.

Дешифратор содержит квазистатический элемент ИЛИ-НЕ 1, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с первым управляющим входогу элемента ИЛИ-НЕ и является выходом 3 дешифратора. Второй управляющий вход элемента ИЛИ-НЕ является управляющим входом 4 дешифратора. Информационные входы элементы ИЛИ-НЕ являются информационными входами 5 дешифратора. Вход первого инвертора б соединен с вторым управляющим входом элемента ИЛИ-НЕ 1, выход которого соединен с выходом первого инвертора б и входом второго инвертора 7, выход которого соединен с вторым входом элемента И-НЕ,

Элемент ИЛИ-НЕ содержит группу .параллельно соединенных транзисторов 8, затворы которых являются инфмационными входами элем«энта, истоки объединены и являются третьим управ ляющим входом элемента,стоки объединены и являются выходом элемен- та, а также соединеныс стоками нагрузочных транзисторов 9 и 10, исто которых соединены с шиной 11 питания, а затворы являются.1 соответствено первым и BTopbEvj управляющим входа ми элемента ИЛИ-НЕ. .

Параллельный дешифратЬр работает следующим образом.

В исходном состоян1 и (режим хранения) строб-сигнаЛ на входе ин.вертора б соответствует уровню логического О, в результате чего на выходе первого инвертора 6 и третье управляющем входе элемента ИЛИ-НЕ напряжение соответствует логической и такое же, как и на его второй шине питания . Нагрузочный транзистор 9 в элементе И31И-НЕ открыт и потенциал на выходе этого элемента соответствует логической независимо от кода адресного сигнала на логических входах 5. Элемент не потребляет мощность в статическом состоянии. На первом входе элемента И-НЕ потенциал соответатвует

I д I I

логической I

на втором - логическому О , в результате чего на

1 выходе этогоэлемента 3, на первом управляющем входеэлемента 1 потенциал способствует логической . Второй нагрузочный транзистор 10 в элементе ИЛИ-НЕ 1 закрат.

В режиме разрешения на вход 4 подается строб-сигнал, который соответствует логической 1 , в результате Чего на выходе первого инвертора потенциал соответствует логическому О - включено .питание элемента ИЛИ-НЕ 1 На выходе второго инвертора 7, и на втором входе элемента И-НЕ 2 потенциал соответствует логической Ч - разрешающий сигнал. Нагрузочные транзисторы 9 и 10 в элементе ИЛИ-НЕ 1 за|срыты. В случае, если на всех входах 5 потенциалы соответствуют логическрму О (ячейка выбрана), на выходе элемента НЛИ-НЕ 1 и первом входе элемента й-НЕ сохраняется (в динамическом режиме) потенциал, сортветсжвующий логической . На вызотде 3 элемнты И-НВ 2 появляется сигнал выборки, соответствующий логическому О, и второй нагрузочный.транзистор 10 в элементе 1 открывается, поддерживая уровень логической 1 на его стоке.

. ;В случае, если н одном из выходов D потенциал соответствует логической , (ячейка не выбрана) , после установления на входе 4 сигнала логической

на вых.оде квазистатического элемента ИЛИ-НЕ устанавливается пojre.нциaл, соответствуюадий лoгичecкo 4y V О , причём он устанавливается раньше, чем сигнал логической на выходе второго

Л

инвертора 7 (на величину.задержки, этого элемента). В результате этого на выходе элемента И-НЕ 2 сохраняется потенциал логической - отсутствие выборки.

При переключении в исходное состояние потенциал на входе 4 переключается на логический О, в результате чего на выходе второго инвертора 7 и втором входе

0 элемента И-НЕ. 2 устанавливается запрещающий сигнал логического . О, а на выходе элемента ИЛИ-НЕ 1 - разрешающий сигнал логической . Причем первый ; из них должен установиться раньше, чем .

5 второй. Это условие обейпечивается соответствующим выбором размеррв нагрузочного транзистора в элементе ИЛИ-НЕ 1 и размеров транзисторов в инверторах 6 и 7. ;.

0

J

Повьлшение быстродействия в пред-, лагаёмой ячейке дешифратора достигается следующим. В схеме известного дешифратора имеется логический эле-.

5

мент с задержкой, наличие которого связано с необходимостью обеспечения синфазности рабояы узлов дешиф ратора. Для обеспечения нормальной работы дешифратора при разбросеха0рактеристик компонентов схемы в условиях серийного производства задерж..ку логического элемента вггбирают достаточно большой и приблизительно равной суммарной задержке остальных

5 каскадов схемы. Схема предлагаемого дешифратора обладает более высоки

;быстродействием,так как не содержит логических элементов о задержкой и ее быстродействие определяется толь- ко суммой-собственных задержек кас0кадов дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Элемент памяти для регистра сдвига | 1979 |

|

SU832600A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Параллельный асинхронный регистр на МДП-транзисторах | 1988 |

|

SU1615807A1 |

| Логическое устройство | 1986 |

|

SU1378047A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Источник питания | 1980 |

|

SU900376A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

ПАРАЛЛЕЛЬНЕОЙ ДЕШИФРАТОР, {Содержащий квазистатический эле1мент ИЛИ-НЕ, iвыход которого соединен с первым входом элемента И-НЕ, ВЫХОД которого соединен с первым управляющим входомэлёмец а ИЛИ-НЕ и является выходой дешифратору второй управляющий вход элемента ИЛИ-НЕ является управляющим входом дешифратора, информационные входы элемента ИЛИ-НЕ являются ингформационными входами дешифратора, отличающийся тем, что с целью повышения быстродействия, он содержит первый и второй инверторы, причем вход первого инвертора соединен с вторвм управляющим входом элемента ИЛИ-НЕ, третий . управляющий вход которого соединен с выходом первого инвертора и вхо-. дом второго инвертора, выход ко- торрго соединен с вторым входом (П элемента И-НЕ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4048629, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 3679911, кл, 307-251, опублик | |||

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-09—Подача