входами соответствующих элементов И пятой и шестой групп, выходы эпементов И пятой и шестой групп соединены с вторыми входами соответствующих эпементов ИЛИ первой и второй групп, первый и второй выходь первого и второго блоков памяти соединены соответственно с первыми входами первого и второго эпементов .ИЛИ, с вторыми входами nej вого и второго эпементов ИЛИ, выходы которых соединены соответственкю с nefH вым и вторым информационньши входами накапливающего сумматора.

2. Устройство поп. 1, отпичаю шее с я тем, что коммутатор содержит группу элементов И, группу эпементов ИЛИ, rpjraiy сумматоров по модулю два. и резистор, причем первый, второй и третий ШIфopv{aциoнныe входы коммутатора соединены соответственно с первым, вторым и третьими входами эпементов ; ИЛИ группы, выходы которых соединены с информационными входами регистра, первый и второй выходы которого являются соответственно первым и вторым управняющими выходами коммутатора, группа управляющих .входов коммутатора сое динена с первыми входами элементов И группы, ВЫХОДЬ которых соединены с первыми входами соответствующих сумматоров по модулю два группь, группа информационных выходов регистра, соответствующая кодам проверяемых логических условий, соединена с входами соответствующих элементов И группы, выходы регистра, соответствующие моднфипнруемой части адреса, соединены с втосьши входами соответствующих сумматоров по модулю два грутты, выходь сумматоров по модулю два группы и шлходы регистра, соответствующие немодифицированюй части адреса, образуют, группу выходов коммутатора.

3. Устройство по п. 1,отличающее с я тем, что блок управления сумматором содержит регистр, схему сравнения, шифратор, дешифратор, первый, второй, третий и четвертый элементы И, группу элементов И, счетчик, первый и второй элементы ИЛИ, причем вход конца операции первой группы входов соединен с первыми входами первого и второго элементов И,а остальные группы входов блока соединены с соответствующими входами дещифратора, выходы которого соединены с соответствующими входами шифратора, выходы шифратора соединены с первой группой входов схемы сравнения, выход которой соединен с вторыми входами первого и второго элементов И, вторая группа входов устройства соединена с входами регистра, ылходы регистра соединены с второй группой входов схемы сравве.ния и первыми входами соответствующих элементов И группы, выходы которых образуют группу выходов блока, выход первого элемента И соединен со счетным входом счетчика, вторыми входами элементов И группы и с первым входом первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, выход второго элеме та И соединен с установочным входом счетчика и вторым входом первого эле ме{гга ИЛИ, выход третьего элемента И является первым выходом блока, группа выходов счетчика соедитева с соответствующими входами четвертого элемента и второго элемента ИЛИ,.выходы которых являются соответственно вторым и третьим выходами бпсжа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство микропрограммного управления | 1980 |

|

SU903877A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968813A1 |

| Микропрограммное устройство управления | 1981 |

|

SU999052A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

1. МИКРбПРОГРДММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, оодаржащвв коммутатор, вакап1 вв$1киций сумматор, блок зпправпенвя сумматорсм, пв.| выйв второй бпокв тамятв, oepeyiu н вторую группы эпемевтов ИЛИ i первую в вторую групйы эпемёнтов И, генератор тактошлх вмпупьсов, првчем .группа ввформаиво шых | лхоаов первого бпока памятв соёовнена с першимв входами ооответсгвуюпшх апемевтов ИЛИ пв|Я1Ой в вторсхй групп, выходы которых соединены сротвётсгвевво . с входамв первого в вторб1Ч рцеравдс накаппвваюиюго сумматора, ввформаввонвые выходы которого соеоввевы с первые ми входамв апвМевтов И перврй в втсфой ;груга1, клход гевератора тактовых вмпулрг сов соедввев.с вторымв входамв эпемевтов И первой в второй групп, первый в второй управпяюшве выходы бдока yib равпеввя, сумматором ооедввевы сротяет . ственврс дарвым управпйюшвм выхсшрм устррйства в первым упйвл киявм вхрдрм вакаплвваюшегр сумматрра, третвй ВЫХРП блрка управпеввя сумматрррм соеаввев с I йввёрсвввыми входами эпементов И пер ври и второй групп в явпяется вторым уПравпяюшвм выходом )гстррйства, выхбды эпементов .И стервой группы- рбразуют группу выхрдов микрорпераовй устррйства в средввены с перврй грУппрЙ входов бпр ка управпеяня сумматрром, выходы эпе ментов И второй группы соедивевы с первой грушюй внфррмаивовш 1х ВХРДРВ крммутатрра, 1юрвая группа ввфррмацврввых ВХРДРВ устррйства средввева с втрррй группрй внфррмавврвных BXPQPB коммуТа- тора в втрррй группрй ВХРДРВ блока управпеввя сумматора у вторая группа машюввых ВХРДРВ устройства соединена .с третьей группрй иифррмаиврнвых входов крммутатрра, о т п в. ч а ю ш е е с я тегл, что, с цепью повышеввя дострвервоств и сввжеввя взбыточнрств первого блока паМятв, введены третья, четвертая, патая, шестая группы элементов И, одноввбратор, пе1шый в второй элементы ИЛИ, группа управляющих ш 1ходрв блока управпеввя сумматрром средине на с управляющих ВХРДРВ коммутатора, управпяювгай шход котррргр сое дввев с переымв входами элэмевтрв И сл третьей в четвертой групп, втррой управлйющвй выхрд .крммутатора соедввев с 00 первыми вхрдамв элементов И пятой в сх шестой групп, ввформацвовные выходы коммутатора- соедвяены с вторыми входамв ooOTBeTCTBj QiBx элементов И третьей В четверТрй: групп выходы которых соедввевы с труппами адресных входов первого в второго бпоков памятв соответст веаво, гевератора тактовых «мпудьсов оОедвнев с ккопю/м рднрввбратрра, выход котрррго с управляющими вхрдамв первого в втррргр блоков памяTBi группа ввформацвонвых выходов второго ({пока памятв соедвве на с вторыми

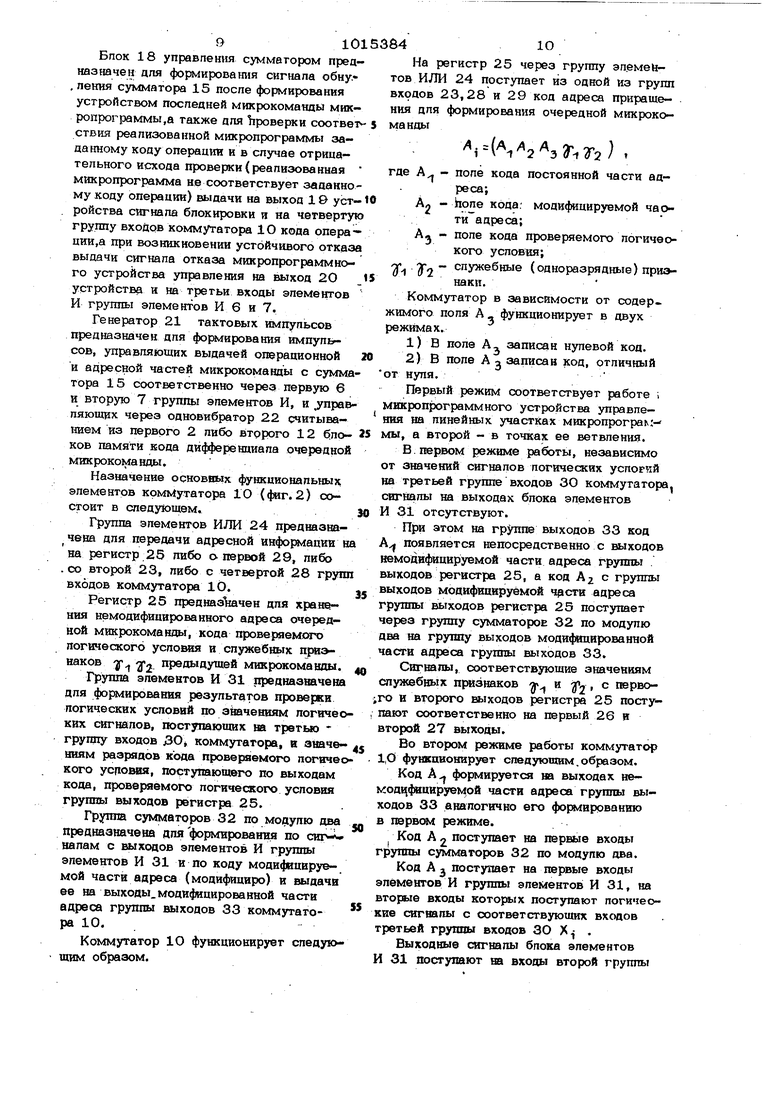

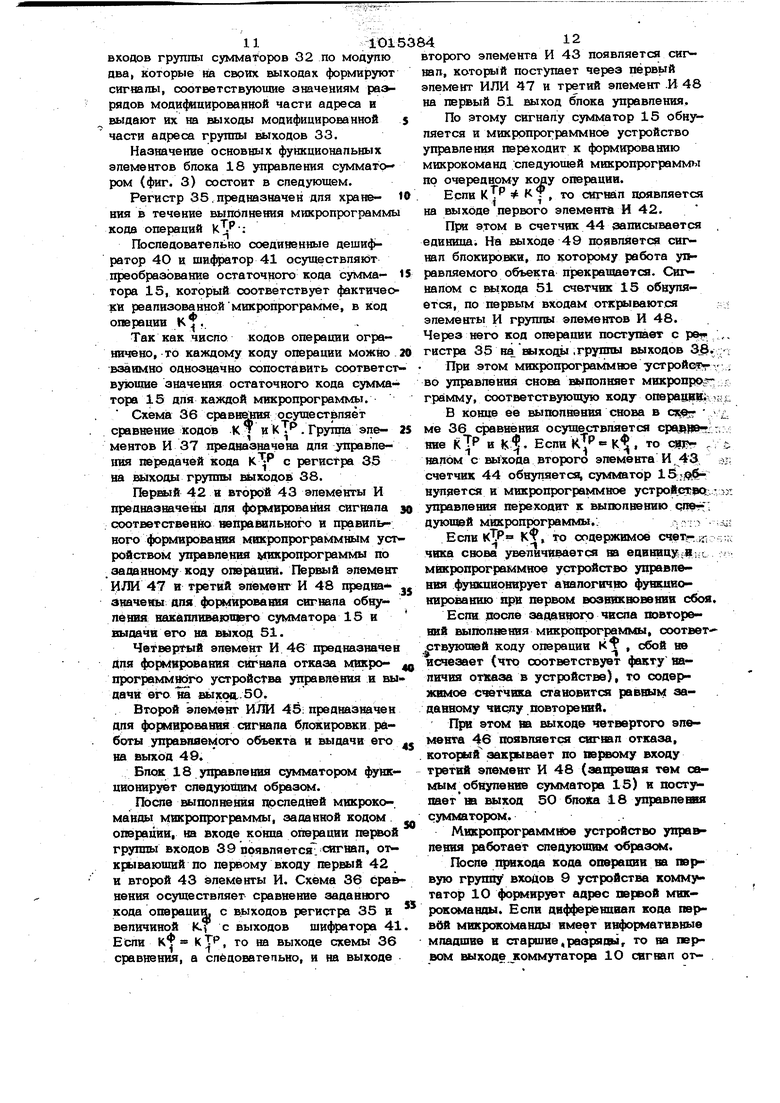

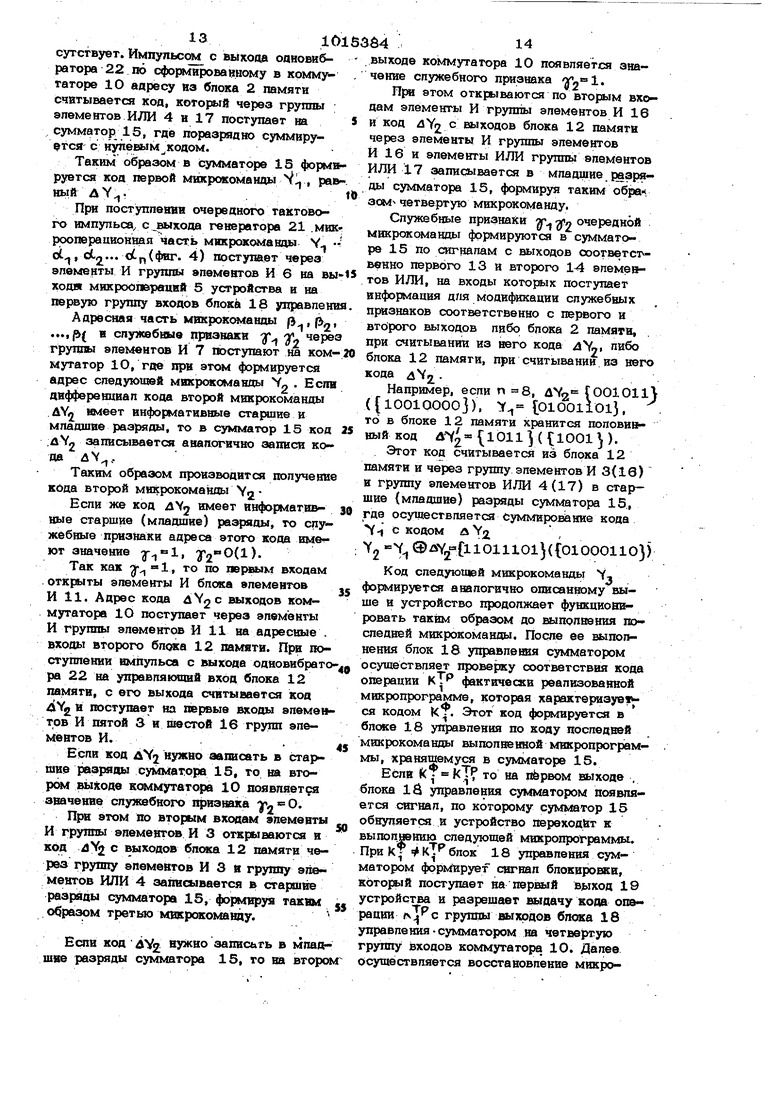

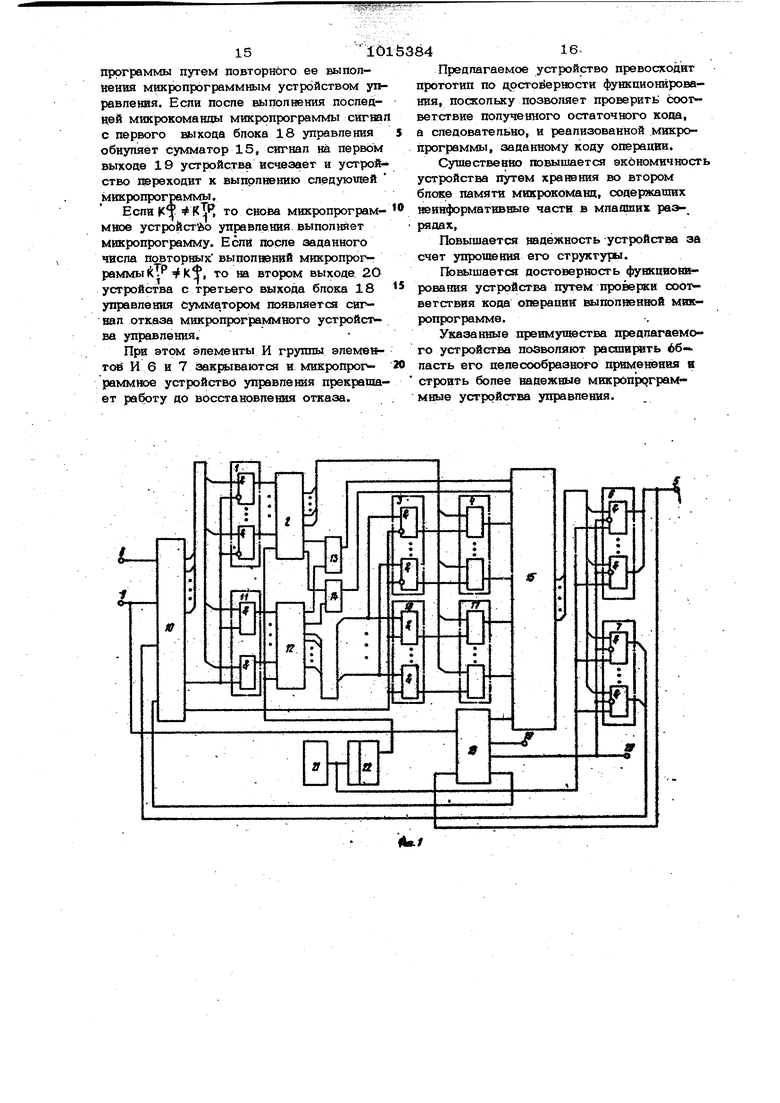

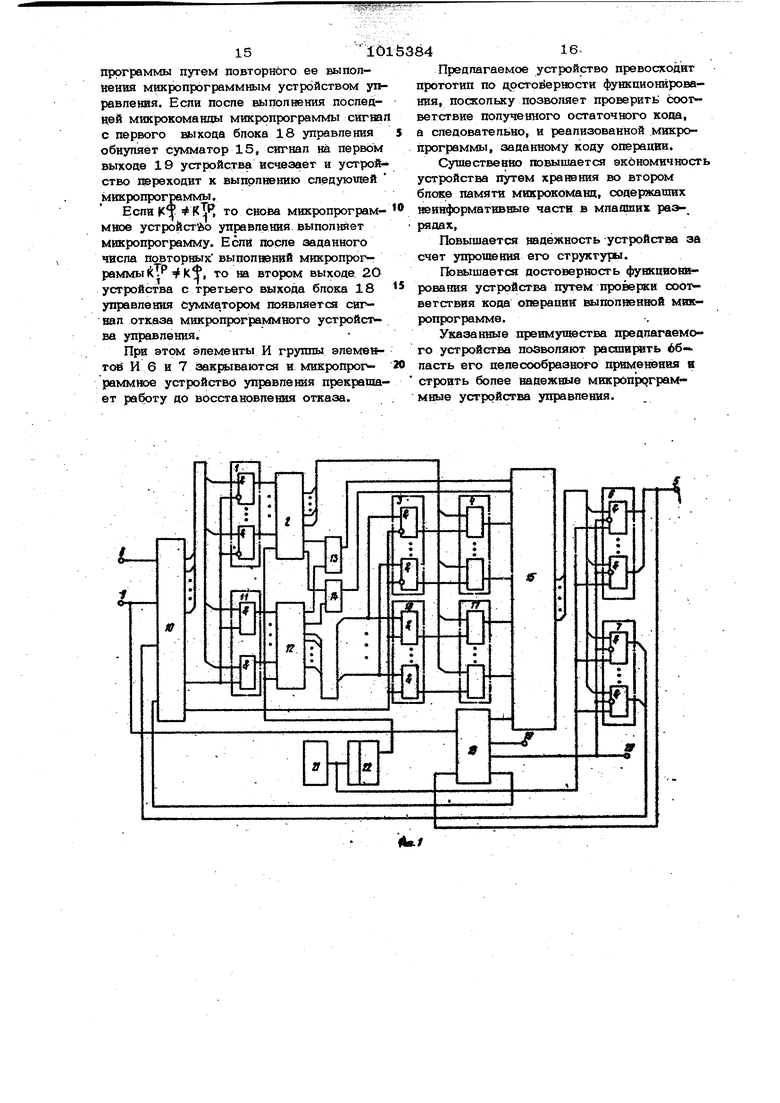

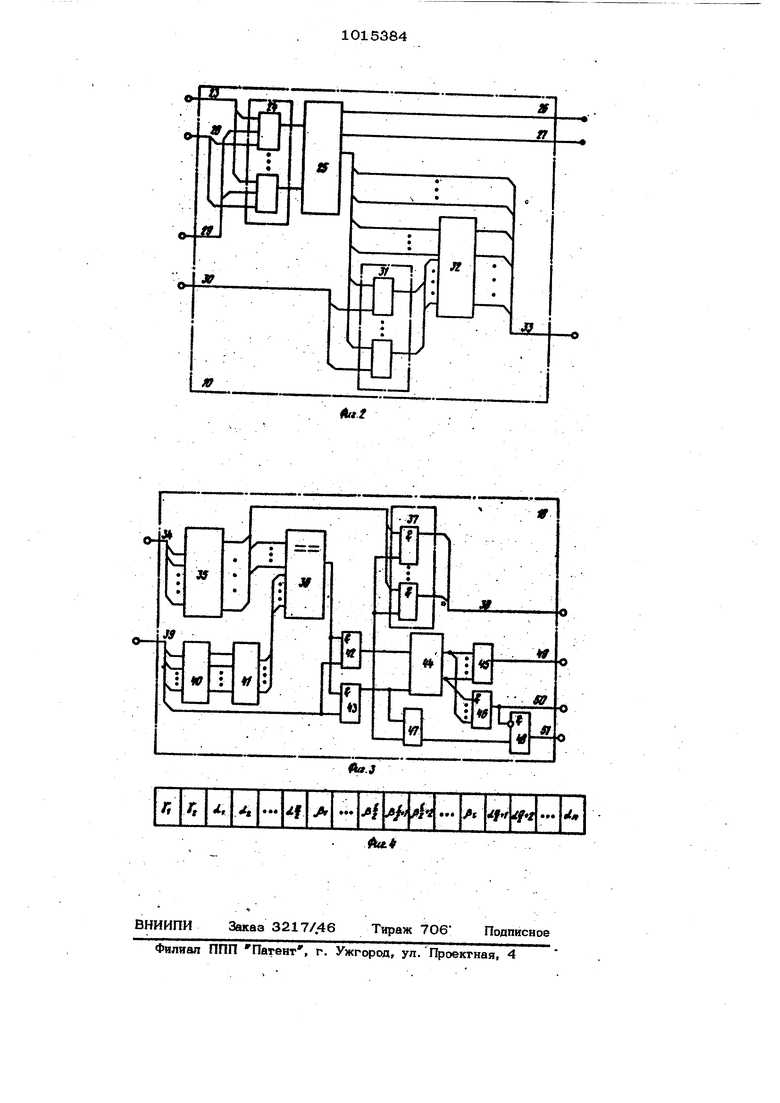

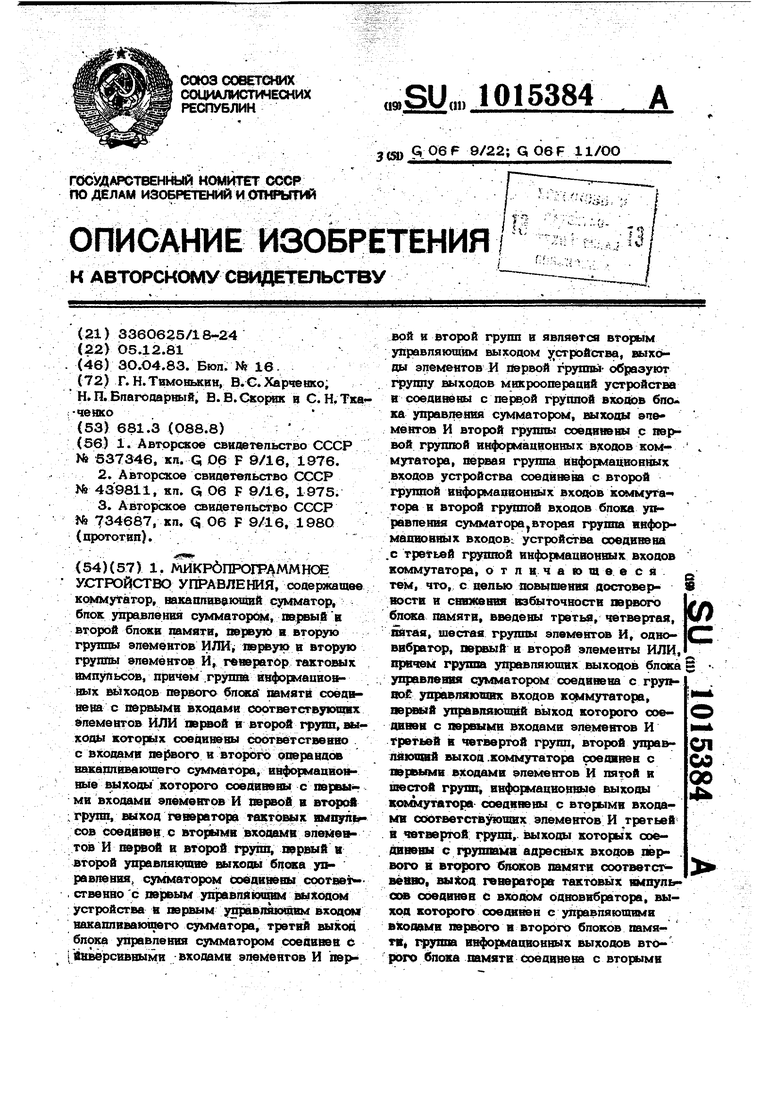

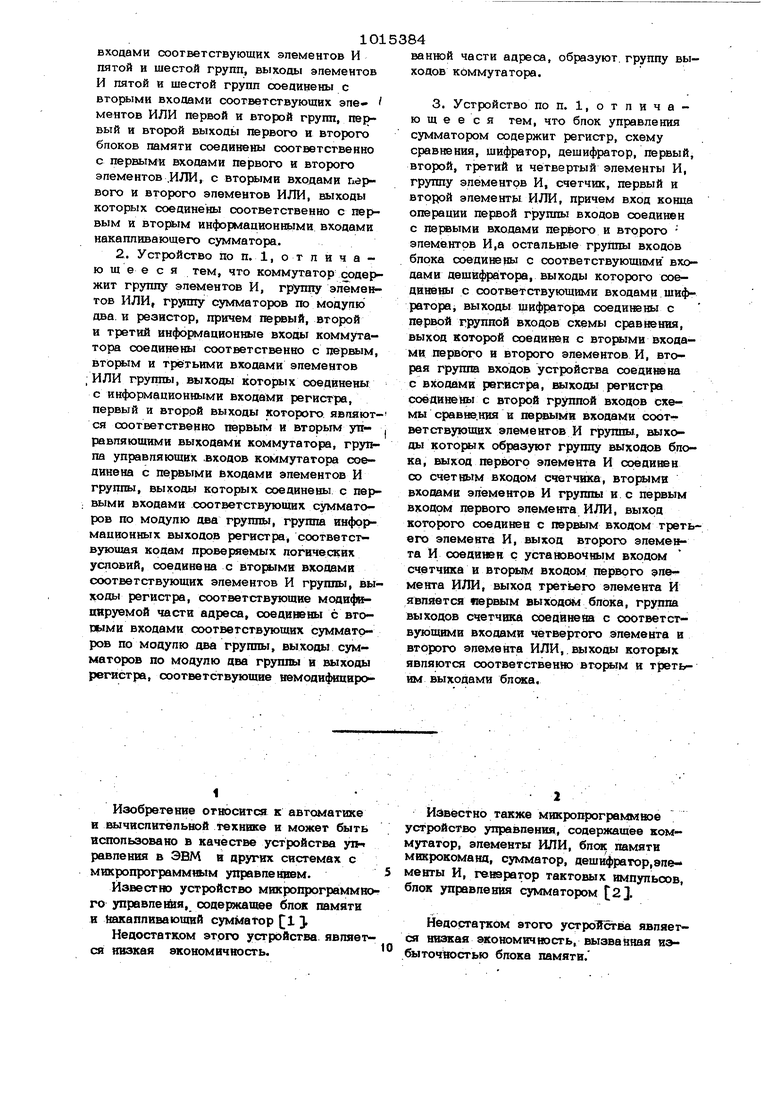

1 Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве устройства yn-t равления в ЭВМ в других системах с микропрограммным улравленвем. Известно устройство микропрограммно го упрввлешя, содеришшее блок памяти и накапливающий сумматор 1 3 Недостатком этого устройства, является низкая экономичность. Известно также микропрогрвмм юе устройство управления, содержащее коммутатор, элементы ИЛИ, блсж памяти микрокоманд, сумматор, деш1«{)ратор,9пе- меиты И, геаэратор тактовых импульсов, блок управления сумматором 2. Недостатком этого ycTpoHictBa является низкая экономичность, вызванная точностью блока памяти. Наибопее близким к предпвгаемому по технической сушностк и достигаемому эффекту является микропрограммное устройство управления, содержащее коммутатор, накаппиваюший сумматор, бпок . упрввпения сумматором, первый и второй блоки памяти., первый и второй блоки элементов ИЛИ, 1юрвый и второй блоки элементов И, генератор тактовых импульсов, причем выходы группы .выходов первого блока памяти.соединены через эпе менты ИЛИ nepsoix и .второго блоков элементов ИЛИ с соответствующими входами первой и второй групп информацион ных входов накапливающего сумматора, управляющий вход которого соединен с первым выходом блока управления сумма тором,а выходы группы выходов соединены с первыми входами элементов И,второго и первого блоков эпёмевтов И,вторые входы которых: соединены с выходом генератора тактовых импупьоов, выходы эпементов И первого блсжа элементов И соединены с выходами микроопераций устройства и входами первой группы входов бпока управлещ1я сумматором, второй выход которого соединен с первым выходом устройства, а третий выход соединен с третьими входами эцементов И первого и второго блоков эле ментов И и третьим выходом устройства, входь первой г руш1Ы входов коммутатора соединены с выходами соответствующих элементов И второй группы элементов И, входы второй группы входов соединены с входами второй группь входов бпбка угфавления сумматором н входами первой группы входов устройства, входы .третьей группы входов соедижны с входами второй группы входов устройства з Недостатком известного устройства является низкая экономичность, обуспсепенная избыточностью кодов микрокоманд записанных в Еюрвом блоке памяти. В прототипе реализована идея дифференциального микропрограммирования, состоящая в том, что в бпокё памяти укаэыва1отсй не коды микрсжоманд, а прв рашения (дифференциалы) кодов. Это позволяет снизить разрвдв0сть микрокоманд, а олеооввтепьно, повысить экономичность устройства. Однако дифферештапы кодов во многи случаях содержат неип рмативные (ну левые) части в младших разрядах (нвпример, при соседнем кодиравании) что позволяет исключить из рассмотрения ух. младшие разряды. В прототипе такая возможность не |реапиарва|ш. Кроме того, недостатком прототипа вляется его низкая достоверность функионирования, что обусловлено отсутствигм проверки соответствия реализованной микропрограммы коду операции. Это из позволяет использовать результаты выполнения микропрограммы объектом управления без их предварительной проверки, что требует введения дополнительной .временной избыточности. Спедовательш, низкие экономичность и достоверж)сть прототипа существенно снижают -его функциональные возможности и надежность. Цель изобретения - снижение избыточ-ности первого блока памяти и повышение достоверности функционирования устройст ва. Поставленная цель достигается тем, что в микропрограммное устройства управления, содержашее коммутатор, нака1Ьпивающий сумматор, бпок управления сумматором, первый и второй блоки Памяти, перьую и вторую группы эпементов ИЛИ, первую и вторую группы эпементов И, генератор тактовых импульсов, причем группа информационных выходов первого блока памяти соединена с первыми входами соответствующих элементов ИЛИ первой и второй групп, ВЫХО.ДЫ которых соединены соответственно с входами первого и второго операндов накаппиваюшего сумматора, информационные выходы которого соединены с первыми входами эле ментов И первой и второй групп, выход генератора тактовых импульсов соединен с входами эпемеитов И первой и второй групп, первый и второй управляющие выходы блока управления сумма тором соединены соответственно с управляющим выходом устройства и управляющга«1 входом ткаппивак щего сумматора, третий блока yI равдения сумматором соединен с ивверс - . выми входами эпементов И первой и второй групп р является вторым управляющим выходом устройства,выходы элементов И первой группы образуют группу выходов микроопераций устройства и соединены с первой группой входов бпока управпевия сумматором, выходы .эпемеитов И второй группы соединены с первой группой унформационных входов к яъ1мутатора, первая .группа информационных входов устройства соединенна с второй группой ивформа- пноиных входов коммутатора в вто группой входов блока управпевпв сумматора, вторая группа информационных входов устройства соедивэва с третьей группой информационных входов коммутатора, введены третья, четвёртая, хютая, шестая группы элементов И, одновибратор первый и второй элементы ИЛИ, причем группа управпяюпгах выходов блока управпения сумматора соединена с группой управляющих входов коммутатора, первый управпяющий выход которого соединен с первыми входами элементов И третьей н четвертой групп, второй управляющий выход коммутатора соединен с первыми входами элементов И пятой и шестой групп, инфорлашюнные выходы коммутатора соединены с вторыми входами соответствующих элементов И третьей и четвертой групп, выходы которых соединены с rpyitпами адресных входов 1Юрвого и второго блоков 1ЮМЯТИ соответственно, выход генератора тактовых импульсов соединен с входом оановибратора, выход которого соединен с управпяющими входами первого и второго блоков памяти, группа информационных выходов второго блока памяти соединена с вторыми входами . соответствующих элементов И пятой и шестой групп, выходы элементов И пятой и шестой групп соединены с вторыми входами соответствующих элементов ИЛИ первой и второй групп, первый и второй выходы первого и второго блоков памяти соединены соответственно с первыми входами первого и второго элементов ИЛИ, с вторыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с пвреым и информационными входами накапливающего сумматора. Ксж мутатор содержит группу элементов И, группу элементов ИЛИ, группу сумматоров по модулю два и резистор, причем первый, второй и третий информационные входы коммутатора соединены со ответственно с , вторым и третьим входами элементов ИЛИ группы, выходы которых соединены с авфа1 ационщ 1МИ входами регистра, первый в второй выходы которого являются соогветствевао пер вым и вторым управпяюпшми выходами коммутатора, группа управляющих входов коммутатора соединены с вхооа ми элементов И группы, выходы которых соединены с входами соответствующих сумматоров по модулю два груп«г пы, группа информаиионных выходов регистра, соответствующая кодам проверяемьрс логических усповий, схэедииет с вторыми входами соответствующих элементов и группы, выходы регистра, оютветствующие модифицируемой части , соединены с вторыми входам соответствующих сумматоров по модулю два группы, выходы сумматоров по модулю ; два групга.1 и выходы регистра, соответствующие нвмодифицированной части адре« са, образуют группу выходов коммутато- ра, Крсале того, блок управления сумма,тором содержит регистр, схему сравнения, шифратор, дешифратор, первый, второй, третий и четвертый элементы И, rpyrtny элементов И, счетчик, первый и второй элементы ИЛИ, причем вход коша операции первой группы входов соединён с первыми входами первого и второго эле« ментов И, а остальные группы входов блока соединены с соответствующими входами дешифратора, входы которого соединены с соответствующими входами шифратора, выходы шифратора соединены с первой группой входов схемы сравнения, выход которой соединен с вторыми входами первого и второго элементов И, вторая группа входов устройства соединена с входами регистра, выходы регистра соединены с второй группой, входов схемы сравнения и первыми входами соответст вующих элементов И группы, выходы которых образуют группу выходов блока, выход первого элемента И соединен со счетным входом счетчика, вторыми входами элементов И группы и с первым входом первого элемента ИЛИ, выход которого соединен с шрвым входом третьего элемэнта И, выход второго элемента И соедввэв с установочш 1М входом счетчика и вторым входом nejffioro элемента ИЛИ, выход третьего элемента И является первым выходом блсжа, группа . ш 1ходов счетчика соесшнена с соответствуютаимв входамв четвертого элемента и второго элемента ИЛИ, выходы которых являются соответственно вторым и третьим выходами блока. Сущность изобретения состоит в повышении аковомичности устройства путем , выделения кодов микрокоманд, содержащих веинформатнвные части в младших разря дах, хранения во втором блоке п 1мяти старших разрядов этих кодов и управления их в накапливающий суммаTopi .а также в повышении достоверности функционирования- путем проверсв соответствия кода операции выполненной микропрограммы, признаком которой является остаточный дифференциал (код) послепней микрокомандьт данной микропрограммы в повторного выполнения мвкро7 1О1 программы в случае отрицательного исхо да проверки. Таким образом, введение третьегошестого бпоков эпементов И, одновибра. тора, первого и второго элементов ИЛИ и укаэаннь1х связей лозвопяет снизить избыточность бпоков памяти и повысить достоверность фуккцнонирования устройства. Hte фкг. 1 щ дставлена функционал наяСхема предлагаемого устройства; на фиг. 2 - 4 нкиионалышя схема комму - татора; на фяг. 3 - функциональная схема блсжа управления сумматором; на . фиг. 4 - структура формата микрокоманды, формируемой ш накапливающем сумматоре. Функциональная схема устройства (фиг. 1) содержит третью группу элементов И Г, первый блок 2 памяти, пятую группу элементов И 3, первую группу элементов ИЛИ 4, выходы 5 микроопераций, первую группу элементов .И 6, Вторую группу элементов И 7, вторую труппу 8 входов, первую группу 9 входов, коммутатор 10, четвертую группу эпементов И 11, второй бпок 12 памяти, пэршый 13- и второй 14 элементы ИШ, накапливающий с лматор 15, шестую группу элементов И 16, вторую/группу элементов ИЛИ 17, блок 18 уп)равления сумматором, первый 19 и второй 2О выходы устройства, генератор . 21 тактовых импульсов, одновибратор 22 На фнг. 2 показаны вторая группа 23 входов коммутатора, г{)уппа элементов ИЛИ 24, регистр 25, пэрмлй 26, второй 27 выходы, четвертая группа входов 28, первая группа входов 29, третья грушш входов 30, группа элементов И 31, группа сумматоров 32 .по модулю , два, группа выходов 33. На 4иг. 3 обозначены вторая группа входов 34, регистр 35, схема 36 сравнения, группы .элвменто И 37, группа выходов 38,-первая групш входов 39, дешифратор 4О, 41, первый элемент И 42., второй элемент И 43, 44, второй элемент ИЛИ 45, четвертый элемент И 46, переый элемент ИЛИ 47, третий элемент И 48, второй 49, третий 5О и первый 51 выходы блока. На фиг. 4 используются следующие обоэвачётш: Л - разряды микроонер авй; (3. - разряды кода адреса приращения (дифференциала) для формнровйнва следуюпюй микрокоманды; - служебные разряды, используемьге для фор 4 .8 мирования выходных сигналов на первом и втором управляюишх выходах коммутаIopa 10 соответственно. Назначение основных функаионалышх , элементов устройства состоит в следующем. В блоках 2 и 12 памяти хранятся коды микрокоманд, причем в первом блоке 2 памяти записаны полные длиной г , а во втором блоке 12 памяти- половинные коды микрокоманд, имеющих не информативные или младшие разряды. Накапливающим сумматором 15 осуществляется формирование кодов микрокоманд путем суммирования кода, полу-ченвого в предыдущем такте, с кодом (дифференниалом), считанным из блоков памяти в данном такте. Шрвый 13 и второй 14 элементы ИЛИ предназначены для формирования по сигналам с первого и второго выходов первого 2 или второго 12 блоков памя. ти сигналов управления формированием в сумматоре 15 служебных разрядов очередной микрокоманды, Коммутатор 10 предназначен для мврованвя адреса очередной микрокоманды н, в завосимосги от значения спужеб1юго разряда предыдущей микрокоманды I , выдачи этого адреса через третью группу элементов И 1 на вход первого блока 2 памяти при , либо через четвертую группу элементов И 11 на вход второго бтюка 12 памяти прт Пятая 3 и шестая 16 группы элеме тов И предвазвачены для управления за « писью, считанной вз второго блока 12 памяти информации либо в старшие разряш 1 сз лматора 15 через первую группу элементов ИЛИ 4 ( -уо 0)t пибо в млад шве разряды сумматора 15 через вторую группу элементов ИЛИ 17 ( Оэрвая 4 и вторая 17 группы элементов ИЛИ нредназначевы для передачи в сумматор15 информации, считанной с первого блока 2 памяти, либо с выходов соответствевво пятой 3 в шестой 16 .групп апемевтов И. Первая группа элементов И 6 преавазвачева для управления выдачей ciii валов микроопераций (06, шдходоБ сумматора 15 на выходы микроопераций 5 устройства. Вторая группа элементов И 7 предназвачева для управления выдачей адресной; информации 1 , f%2t I Р и служебных првзваков 1., в сумматора 15 на 4 я««мутатор 10. 910 Бпок 18 управления сумматором предназначен для формирова шя сигнала обну. , пения сумматора 15 после формирования устройством последней микрокоманды микропрограммы.а также для проверки соответ стБия реализованной микропрограммы заданному коду операции и в случае отрицательного исхода проверки {реализованная микропрограмма не соответствует заданно му коду операции) выдачи на выход 1 & устройства блокировки я на четвертую группу входов коммутатора 1О кода опера иии,а при возникновении устойчивого отказ вышчи сигнала отказа микропрограммного устройства управления на выход 2О устройства и на третьи входы элементов И гругшы элементов И 6 и 7. Генератор 21 тактовых импульсов предназначен для формирования импул1гсов, управляющих выдачей операционной и адресной частей микрокоманды с сумма тора 15 соответственно череэ первую 6 и вторую 7 группы элементов И, и управ ляющих через одновибратор 22 считываиз первого 2 либо второго 12 блоКОВ памяти кода дифференциала очередной микрокоманды. Назначение основных функциональных элементов коммутатора 10 (фиг. 2) состоит в следующем. Группа элементов ИЛИ 24 предназначена для передачи адресной информации н на регистр 25 пибо о первой 29, либо . со второй 23, либо с четвертой 28 групп входов коммутатора 10. Регистр 25 предназначен для хранения немодифицнроваиного адреса очередной микрокоманды, кода прове{М1ем0го яогшеского условия п служебных приэнаков ТГ-т 2Г2 микрокоманды. Группа элементов И 31 преаназначена для формирования результатов проверки логических условий по значениям погичео ких сигналов, поступающих на третыо группу входов j3Oj коммутатора, и значениям разрядов кода проверяемого погвчео кого усцоввя, поступающего по выходам кода, проверяемого логического условия группы выходов регистра 25. Группа сумматоров 32 по модулю два предназначена дпя формирования по шлам с выходов элементов И группы элементов И 31 и по коду модифицируемой части адреса (модифициро) и выдачи ее на выходы.модифицированной части адреса группы выходов 33 коммутатора 10. Коммутатор 10 функционирует следук шим образом. 84 На регнстр 25 через группу эл.емейтов ИЛИ 24 поступает из одной из групп входов 23,28 и 29 код адреса прирашения для формирования очередной микрокомандыА.-(, TiTTy где А - попе кода постоянной части адреса;Art - попе кода: модифицируемой чаСУТИ адреса; А- - поле кода проверяемого логического условия; ff ТГп служебные (одноразрядные) признаки. Коммутатор в зависимости от содержимого поля А, функционирует в двух реж({мах. 1)В попе А., записан нзглевой код. 2)В поле А а записан код, отличный от нуля. Первый режим соответствует работе i микроп{Х)Граммного устройства управления на линейных участках MHKponporpaN:мы, а второй - в точках ее ветвления. В. первом режиме работы, независимо от значений сигналов логических успогкй на третьей группе входов ЗО коммутатора, сигналы на выходах блока элементов И 31 отсутствуют. При этом на группе выходов 33 код А появляется непосредственно с выходов немодифицируемой части адреса группы выходов регистра 25, а код АЯ с группы выходов модифицируемой части адреса группы №1ходов регистра 25 поступает через группу сумматоров 32 по модулю два на группу выходов модифицированной части адреса группы выходов 33. Сшнапы, соответствующие значениям служебных признаков у и 2 первого и второго выходов регистра 25 поступают соответственно на первый 26 н второй 27 выходы. Во втором режиме работы коммутатор 1,О функционирует еле дующим, образом. Код А фо{ 4ируется на выходах немодцфвцируемой части адреса группы выходов 33 аналогично его формированию в паркам, режиме. Код А 2 поступает на первые входы группы сумматоров 32 по модулю два. Коя А J поступает на первые входы элементов И группы элементов И 31, на вторые входы которых поступают логические сигналы с соответствующих входов третьей группы входов ЗО X,- . Выходные сигналы блока элементов И 31 поступают ш входы второй группы 11101 входов группы сумматоров 32 по модулю два, которые т своих выходах формируют сигналы, соответствуюише значениям ра рядов модифицированной части адреса в выайют их нв выходы модифицированной части адреса группы выходов 33. Назначение основных функциональных элементов блока 18 управления суммат ром (фиг. 3) состоит в следующем. Регистр 35.предназначен дпя хранения в течение выполнешя микропрограммы кода операций Последовательно соединенные дешифратор 4О и шифратор 41 осуществляет преобразование остаточного кода сумматора 15, который соответствует фактичео ки реализованноймикропрограмме, в код операции К. Так как число кодов операции ограничено, то каждому коду операции можно взаимно однозначно сопоставить соответст вующие значения остаточного кода сумматора 15 для каждой микропрограммы. CxeMia 36 сравнения осуществляет сравнение кодов КЛ и К . .Труппа эпементов И 37 предназначена для управления передачей кода К с регистра 35 на выходы групгал выходов 38. Первый 42 И второ б 43 элементы И предназначеш для формирования сигнала соответственйо неправильиогю и правильгногоформироващш микропрограммным уст ройством управления микропрограммы по заданному коду оперений. Шрвый элемент ИЛИ 47 и третий элемент И 48 гфедназнанессы апя фо1я 1ировавия сигнала ния накапливающего сумматора 15 и выдачи его на выход 51. Четвертый элемент И 46 предназначен Для формирсмвания сигнала отказа микропрограмм ч) устройства уп равпёния и вы дачи его на выхо11..5О. Второй элемент ИЛИ 45: предназначен для формирования сигнала бпокировки работы управнаемого объекта и выдачи его на выход 49. Блок 18 у1фавления сумматором 4 икционирует спеаующим образс 4. После выполнения щхследней микрокоманда микропрограммы, заданной кодом операции, на входе конца операции первой группы входов 39 появляется -сягнап, открывающий по первому входу первый 42 и второй 43 элементы И. Схема 36 срав нения осуществляет сравнение заданного кода операции, с выходов регистра 35 н величиной К с выходов шифратора 41 Если К кТР, го на выходе схемы 36 сравнения, а спёдоватепьно, и на выходе 412 второго элемента И 43 появляется сигнал, который поступает через первый элемент ИЛИ 47 и третий элемент .И 48 на первый 51 выход блока управления. По этому сигналу сумматор 15 обнуляется и микропрограммное устройство управления переходит к формированию микрокоманд следующей микропрограммы по очередному коду операции. ЕСЛИ кТР ч Кт , то сигнал появляется на выходе первого элемен И 42. При этом в счетчик 44 записывается единица. На выходе 49 появляется сигнал блокировки, по которому работа упгравляемого объекта прекращается. Си1 налом с аь1хода 51 сч&тчик 15 обкупя- ется, по первым входам открываются элементы И группы элементов И 48. Через него код операции поступает с рв. гистра 35 на выходы .группы выходов ЗВ, При этом микропрограммюе устройство управления енот выполняет микропро Грамму, соответствующую коду операции; к В конце ее выполнения снова в ме 36 сравнения осущертвляется cpajEt iie-. ние кТР и К, Если KJP К, то с)Рг налом с выхода второго элемеита И,43. счетчик 44 обнуляется сумматор н: ретйг и микропрограммное устройсясао::. управления переходит к выполнению piierдующей микропрограммы,:v ;Если кТР К, то содержимое счет ; чика свова увеличивается на единиау вис микропрограммное устройство управпенвя функционирует аиапогичво функдиоКированию при первом возвиквовении сбоя. Еспи после заце1нвого числа повторений выполнения микропрограммы, соответ.ствуютаей коду операции К , сбой не . исяезает (что соответствует факту тиичия отказа в устройстве), то содержимое счетчика становится равным заданному чвопу повторе шй. При этом т выходе четвертого эпемента 46 появляется свгаал отказа, который ;закрывает по входу третий элемент И 48 (запрещая тем самым обнуление сумматора 15) и поступает на выход 5О бпоКа 18 управпенвя сумматором... Микропрограммное устройство упра пеняя работает следующим образом. После пфнхода кода операции ва группу входов 9 устройства коммутатор 10 формирует адрес первой микрокоманды. Если дифференциал кода первйй микрокоманды имеет информативные младшие и старшие,равря№, то на первом выходе коммутатора 1О сигнал отсутствует. Импульсом с выхода одновибратора 22 1ю сфо{ «1ровавному в коммугагоре 10 адресу из блока 2 памяти считывается код, котора.1й через группы эпемевтов ИЛИ 4 и 17 поступает на сумматор/15, где поразрядно суммируется с ну71ввым кодом.Таким образом в сумматоре 15 форм руется код первой микрокоманды V, рав ный ДУ:,. При поступлении очередного тактового импульса, с.выхода генератора 21 .мик роопераиионная часть микрокомашця У о(., ( поступает через элементы И группы элементов И 6 иа вы ходя микроопераций 5 устройства и на первую группу входов блоки 18 управлени Адресная часть микрокомашхы f. .,.,р( и служебные признаки чере грущю элементов И 7 тюступают на коммутатор 1О, где при этом формируется адрес следующей микрокоманды V . Если дифференциал кода второй микрокоманды дУл iBvfeeT информативные старшие и младшие разряды, то в сумматор 15 код записывается аналогично записи кода ЛЧ, Таким образом производится получение кода второй микроксяланды 2 Если же код ЛУ имеет информатив ные старшие (младшие) разряды, то служебные признаки адреса этого кода тлвгют значение , (1). Так как тг «1, то по пб ряллм входам . открыты элементм И блока элементов И 11. Адрес кода выходов коммутатора id поступает через элементы И группы элементов И 11 на адресшле . входы второго блока 12 памяти. При поступлении импульса с выхода одновибрато ра 22 ой управляющий вход блока 12 памяти, с его выхода считывается код ЛУ и поступает на первые входы элемен тов И пятой 3 и шестой 16 групп элемевтов И... Если код дУ2 нужно записать в старшие рвзртды сумматора 15, то на втором щдАоде К(я«1мутатора 10 появляетфя звачеиие служебного признака При этом по вторым входам элементы И группы элементов И 3 открываются и код лУ2 с выходов блока 12 памяти через группу елемевтов И 3 и группу элементов ИЛИ 4 записывается в старшие разряды сд мматора 15, формируя таким образом третью мвкрсясоьюиоу. Еспи код дУ2 нужно запись гь в младшие разряды сумматора 15, то на вторс выходе коммутатора 10 появляется значение служебного признака Пра этом открываются по вторым вхс дам элементы И группы элементов И 16 и код /iY2 с выходов блока 12 памяти через элементы И группы элементов И 16 и элементы ИЛИ группы элементов ИЛИ 17 записывается в младшие | эряды сумматора 15, формируя таким обра- зом четвертую микрокоманду. Служебные признаки gT-j 2 ° ®Р® ° микрокоманды формируются в сумматоре 15 по сигналам с выходов соогветсгввнно первого 13 и второго 14 элементов ИЛИ, на входы которых поступает информация д/ш модификации служебных признаков соответственно с первого и втброго выходов либо блока 2 памяти, при считывании из него кода либо блока 12 памяти, при считывании из него кода dV2. Например, если п 8, й,, Г О01011} Х 1001ОООО). У {OlOOllOlJ, . то в блоке 12 памяти хранится половив иый код ({iOOi). Этот Код считывается из блока 12 памяти и через группу элементов И 3(16) и группу элементов ИЛИ 4(17) в старшие (младшие) разряды сумматора 15, где осуществляется Суммиров1ание кода V с кодом лУ2 2 ®лу {110111015({01000110)) Код следующей микрокоманды У, формируется аналогично описанвому выше и устройство продолжает фувкциовировать таким образом до выполнения последвей микрокоманды. После ее выполнения блок 18 управлешя сумматором осуществляет проверку соответствия кода операции кТ фактически реализованной микропрограмме, которая характе;шзуе11 ся кодом К .. Этот код формируется в блоке 18 управления по коду последней микрокомавды выполвенвой мшсропрограммы, хранящемуся в сумматоре 15. ЕСЛИ («КТР то на пбрвом выходе , блока 13 управления сумматором появляется сигнал, по которому сумматор 15 обнуляется и устройство переход| т к выполнению следующей микропрограммы.. При k| # кТ блок 18 управления сумматором форь ирует сигнал блокировки, который поступает ва первый выход 19 устройства и разрешает выдачу кода операции л с группы выходов блока 18 управлевия-cyiviMaTOpoM ва четвертую группу 1эходов коммутатора 10. Далее осуществляется восставовлевие микропрограммы путем повторного ее выпопнения микропрограммным устройством управпенвя. Еспи после выпопнения поспедней микрокоманды микропрограммы сигна с первого 1хода блока 18 управления обнуляет сумматор 15, сигнал на первом выходе 19 устройства исчезает и устройство переходит к выполнению следующей микропрог раммы. ЕспиК КТР то снова микропрограммное устройство управления выполняет микропрограмму. Если после заданного числа повторных выполаений микропрограммы (;ТРт К , то на втором выходе 2О устройства с третьего выхода блока 18 управления сумма.тором появляется сигнал отказа микропрограммного устройств ва управления. При этом элементы И группы элеме тоё И 6 и 7 ;эакр 1ваются и микроорограммиое устройство управления прекращает работу до восстановлеивя отказа. Предлагаемое устройство превосходит прототип по достоверности функционирования, поскольку позволяет проверить; соответствие полученного остаточного кода, а следовательно, и реализованной микропрограммы, заданному коду onepeutra. Существенно повышается экономичность устройства путем хранения во втором блоке памяти микрокоманд, содержащих неинформативные части в млашпих раэрядах. Повышается надёжность устройства за счет упрощения его структуры. ПЬвышается достоверность функцио18 ровавия устройства путем проверки соответствия кода операции выпблненеюй микропрограмме. Указанные преимутаества предлагаемого устройства позволяют расширить 66- ласть его целесообразного применения в строить более надежные микропр граммные устройства управления.

tt

IS

ЖО

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-04-30—Публикация

1981-12-05—Подача