Изобретение относится к запоминаклдим устройствам.

Известно запоминающее устройство с самоконтролем, в котором контроль правильности работы дешифраторов и адресных цепей осуществляется методом шифрации выбранных адресных шин в код адреса 1 .

Недостатками указанного устройства являются большая избыточность и малое быстродействие, являкядиеся следствием сложности шифратора.

Наиболее близким к изобретению является запоминающее устройство с самоконтролем, содержащее основной накопитель J.

Недостатком этого устройства является низкая надежность из-за того, что в устройстве оперативно не контролируются входные адресные цепи, тракт дешифрации и исправность адресных шин основного накопителя, а кроме того, сложна диагностика программируемого постоянного накопителя.

Цель изобретения - повышение надежности, а также точности контроля запоминающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее основной

накопитель, входы которого соединены с выходами адресного дешифратора, и первый программируемый постоянный с накопитель, введены второй программируемый постоянный накопитель, сумматор по модулю два, источники опорного напряжения,,, пороговые усилители, ключи, элемент И, элемент ИЛИ, менты ИЛИ-НЕ, управляющий дешифратор, нагрузочные элементы и переключатели, причем входы программируемых постоянных накопителей соединены соответственно с выходами основного накопителя, а первые выходы подключены к

15 шине нулевого потенциала, вторые выходы программируемых постоянных на-, копителей соединены соответственно со входом первого переключателя и выходом первого ключа и со входом

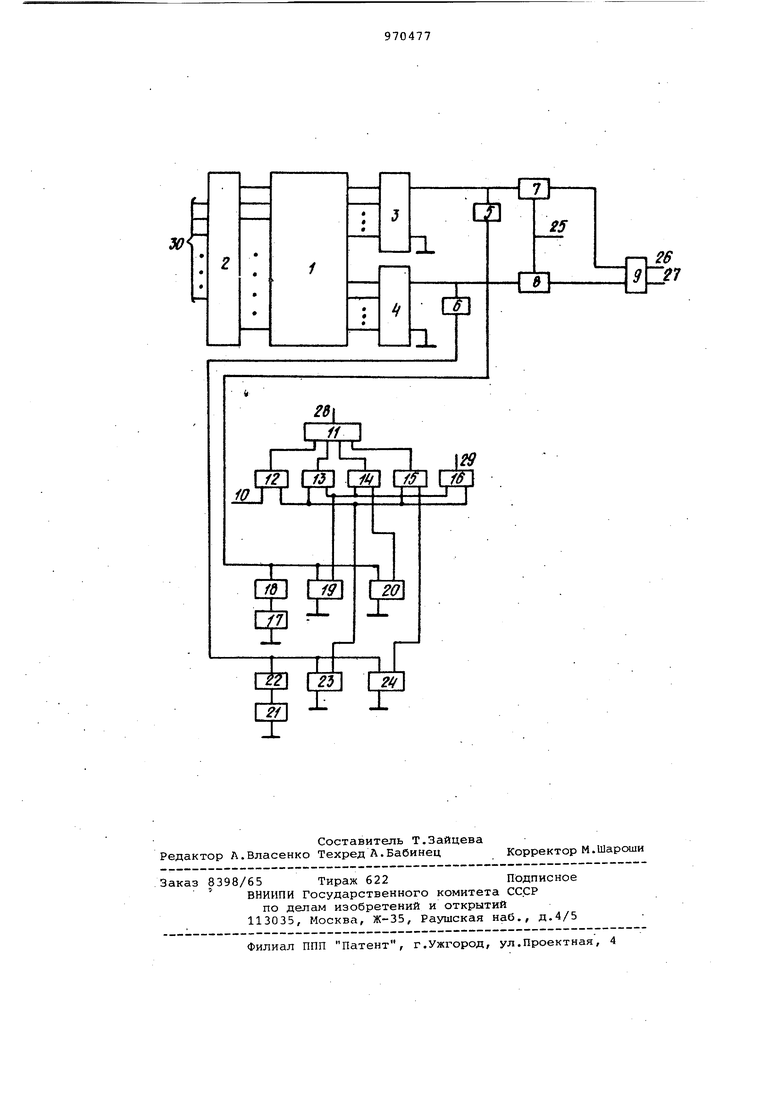

20 второго переключателя и выходом второго ключа, первые входы .-лючсй соединены с выходами управляющего дешифратора, выход первого переключателя подключен к первым входам первого и второго пороговых усилителей и первому выводу первого нагрузочного элемента, второй вывод которого соединен с первым выходом первого источника опорного напряжения, вы30ход второго переключателя подключен к первым входам третьего и четвертого пороговых усилителей и первому выводу второго нагрузочного элемента второй вывод которого соединен с пер вым выходом второго источника опорно го напряженияf вторые выходы источников опорного напряжения и вторые входы пороговых усилителей подключены к шине нулевого потенциала, выход первого порогового усилителя сое динен с первыми входами первого и второго элементов ИЛИ-НЕ и элемента И, выходы второго и четвертого пороговых усилителей подключены соответственно ко второму входу второго эле мента ИЛИ-НЕ и к первому входу третьего элемента ИЛИ-НЕ, выход третьего порогового усилителя соединен со вторыми входами первого и третьего элементов ИЛИ-НЕ и элемента И и первым входом сумматора по модулю два, выход которого и выходы элементов ИЛИ-3НЕ подключены ко входам элемента ИЛИ, выход которого и выход элемента И являются контрольными выходами устройства, одними из входов которого являютйй соответственно второй вход сумматора по модулю два и входы управляющего дешифратора, вторые входы ключей объединены и являются другим входом устройства, На чертеже приведена функциональная схема предлагаемо4 о устройства. Запоминающее устройство содержит основной накопитель 1, адресный дешифратор 2, первый 3 и второй 4 программируемые постоянные накопители, выполненные из электрически программируемых элементов памяти, например, из полевых транзисторов с плавкой перемычкой, первый 5 и второй б пере ключатели, первый 7 ивторой 8 ключи, управляющий дешифратор 9. На чертеже обозначен вход 10 устройства, предназначенный для подачи контрольного кода адреса. Устройство содержит также элемент ИЛИ 11, сумматор 12 по модулю два, первый 13, второй 14 и третий 15 эле менты ИЛИ-НЕ, элемент И 16, первый источник 17 опорного напряжения, пер вый нагрузочный элемент 18, первый 19 и второй 20 пороговые усилители, второй источник 21 опорного напряжения, второй нагрузочный элемент 22 третий 23 и четвертый 24 пороговые усилители. На чертеже обозначены также вход 25-27, выходы 28 и 29 и входы 30 устройства. Предлагаемое устройство работает следующим образом, Работа устройства рассматривается при следующих условиях. Число входов накопителя 1 равно числу выходов (числу адресных шин (А строк накопителя 1). При подаче на входы 30 определенной комбинации кода адреса (КА), на соответствующем выходе дешифратора 2 формируется положительный потенциал, а остальные его выходы имеют нулевой потенциал. Положительный потенциал с выхода дешифратора 2 подается на соответствующий вход накопителя 1, с которого по адресной шине передается на соответствующий выход накопителя 1, На одном из входов накопителя . 3, подключенных к накопителю 1, появляется положительный потенциал,если- на входы дешифратора 2 подается комбинация КА, содержащая нечетное число единиц. На одном из входов накопителя 4, подключенных к накопителю 1, появляется положительный потенциал, если на входы дешифратора 2 подается комбинация КА, содержащая нечетное число единиц. Рассматриваются режимы работы устройства в трех случаях. Первый случай. При отсутствии обращения и дефектов в устройстве потенциал на всех выходах накопителя 1 равен нулю. Через соответствующие нагрузочный элемент 18 или 22, накопитель 3 или 4, переключатель 5 или б, включенный для соответствующего источника 17 или 21 опорного напряжения в прямом направлении, протекает пренебрежительно малый ток, в результате чего на входы каждого из пороговых усили телей 19 и 20 или 23 и 24 подается практически полное напряжение соответствуквдего источника 17 или 21, превышающее порог усилителей 19, 20, 23 и 24, и на выходах всех усилителей 19, 20, 23 и 24 имеется единичный положительный уровень потенциала. Второй случай. На одном из выходов накопителя 1 (при обращении к устройству) имеется положительный потенциал правильная работа устройства) ,: ел и положи тельный потенциал имеется на одном из входов накопителя 3, то через нагрузочный элемент 18, переключатель 5 и накопитель 3 от источника 17 протекает ток много больший, чем в первом случае. В результате на входах усилителей 19 и 20 устанавливается напряжение, меньшее порога усилителя 19, но больше порога усилителя 20, и тогда на выходе гсилит€шя 19 - нулевой уровень, а на выходе усилителя 20 - единичный уровень положительного потенциала. Если же положительный потенциал имеется на одном из входов накопителя, 4 то через нагрузочный элемент 22, переключатель 6 и накопитель 4 от источника 21 протекает ток много больший, чем в первом случае, В результате на входах усилителеп 23 и 24 устанавливается напр жение, меньшее порога усилителя 23, но большее порога усилителя 24, и тогда на выходе усилителя 23 - нулевой уровень, а на выходе усилителя 24 - единичный уровень положительного потенциала. Третий случай. При обращении, вследствие сбоя ил постоянной неисправности более чем на одном из входов накопителя 3 (или накопителя 4), подключенных к вьлхода накопителя 1, имеется положительный потенциал. Если положительный потенциал имеется более чем на одном из входов накопителя 3, то через нагрузочный элемент 18, переключатель 5 и накопитель 3 от источника 17 проте кает ток больший, чем во второмслучае. В результате на входах усилителей 19 и 20 устанавливается напряжение, меньшее порога усилителей 19 и 20, и Яа их выходах - нулевой уровень потенциала. Если положительный потенциал имеется более чем на одном из входов накопителя 4, то через нагрузочный элемент 22, переключатель и накопитель 4 от источника 21 проте кает ток больший, чем во втором случае. В результате на входах усилителей 23 и 24 устанавливается напряженир, меньшее порога усилителей 23 и 24, и на их выходах будет нулевой уровень потенциала. Правильность обращения к АШ строки накопителя 1, исправность выходных адресных целей и правильность приема КА осуществляется проверкой на совпадение контрольного КА, подаваемого по входу 10 на второй вход сумматора 12, и признака четности фактически выбранной АШ строки накопителя 1, подаваемого с выхода усилителя 23 на первый вход сумматора 1 Сигнал на входе 10 имеет нулевой уровень потенциала, если число единиц в комбинации КА, подаваемой на входы 30, четное, и единичный в противном случае. Сигнал с неправильной адресацией выдается на выход 28 устройства с выхода элемента ИЛИ 11. Не имеется ошибки в адресации АШ строк накопителя 1, если во время обращения на выходе 28 устройства нулевой потенциал, либо имеются четные ошибки в комбинации КА, поданной на входы 30, или вместо нужной АШ строки накопителя 1 выбирается другая АШ строки, имеющая одинаковый признак четности. Все остальные возможные отказы и сбои, составляющие большую часть от общего числа возможных отказов и сбоев, выделяются по соответствующим сигналам на вькодах усилителей 19, 20, 23 и 24 соответствующими элементами ИЛИ-НЕ 13, 14 и 15, сигналы с выходов которых объединяются элементом ИЛИ 11. Элемент ИЛИ НЕ 15 формирует сигнал об неправильной адресации, заключающей:я в выборке более одной четной АШ :;троки накопителя 1. Элемент ИЛИ-НЕ 14 формирует сигнал о неправильной адресации, заключающейся в выборке более одной нечетной АШ строки накопителя 1. Элемент ИЛИ-НЕ 13 формирует сигнал о неправильной адресации, заключающейся в выборке нескольких АШ строк накопителя 1 с разными признаками четности. Элемент И 16 формирует сигнал с единичным уровнем потенциала, если производится обращение к неисправной АШ строки накопителя 1, и выдает его на выход 29 устройства. Рассмотрим программирование накопителей 3 и 4 на примере программирования накопителя 3. Прогрс1ммирование накопителя 4 осуществляется аналогично. Допустим, что в результате диагностирования устройства обнаружено, что при некоторой комбинации КА на входах 30 во время .обращения: более чем на одном из входов накопителя 3, подключенных к накопителю 1, появляются положительные потенциалы, т.е. имеет место межзамыкание АШ строк накопителя 1, либо неисправность дешифратора 2. В этом слу чае необходимо запрограммировать накопитель 3 таким образом, чтобы при обращении по данной комбинации КА формировался сигнал об обращении к неисправной АШ строки накопителя 1. Программирование накопителя 3 осуществляется в следующей последовательности. Со входов 26 и 27 устройства на соответствующие входы дешифратора 9 подается код, по которому на выходе дешифратора 9, подключенном ко входу ключа 7, формируется разрешающий потенциал, и при этом потенциал программирования Со входа 25 через ключ 27 подается на вход накопителя 3. Потенциал программирования обычно имеет большую величину, чем напряжение источника 17, однако переключатель 5 включается для потенциала программирования в обратном направлении , и поэтому потенциал программирования не поступает на входы усилителей 19 и 20, предупреждая тем самым ИХповреждение. После этого производится обращение по той комбинации КА, при которой более чем на одном из входов накопителя 3 появляются положительные потенциалы, по которым и производится программирование соответствующих электрически программируемых элементов памяти в накопителе 3. По окончании обращения со входов дешифратора 9 снимается соответствующий код, ключ 7 закрывается и со входа накопителя 3 снимается потенциал программирования. При последующей работе, в, случае обращения по данной комбинации КА На входах 30, элементом И 16 формируется сигнал об обращении к неисправной АШ строки накопителя 1, который может быть использован для уп равления устройством, осуществляющим подключение вместо неисправной АШ строки накопителя 1 исправной на резерве. Таким образсям, устройство поз воля ет производить оперативньа контроль исправности АШ строк накопителя 1, дешифратора 2, -входных ад1эесных цепе и правильность приема КА на входах 30, а также оперативно формировать, сигнал об обращении к неисправным строкам накопителя 1, пов1;1шая тем самым надежность и точнос7гь контроля устройства. Технико-экономическое преимущество предлагаемого запоминакадего устро ства заключается в его более высокой надежности по сравнению с прототипом Формула изобретения Запоминающее устройство с самокон ролем, содержшцее основной накопител входы которого соединены с выходами адресного дешифратора, и первый програ .г4ируег ;й постоянный нз.копитель, о т л и ч гг ю щ е е с я тем, что,, с целью повышения надежности устройстBS, в него введены второй программируемый постоянный накопительJ сумматор по МОХ1УЛЮ лва, источники опорног напряжения, пороговые усилители, клю чи,, элемент И, элемент ИЛИ, элементы ИЛИ-НЕ, управляющий дешифратор, нагрузочные элементы и переключатели причем входы пpoгpaм етpyeмыx постояв нкпс накопителей соединены соответстй-энно е выкодами основного накопителя а первые выходы подключены к шин нулезого потенциала, вторые выходы про.гра1-й.шруемБ1Х постоянных накопителей соединены соответственно с входо лервого переключателя и выходом первого ключа и с входом второго переключателя и выходом второго ключа, первые входы ключей соединены с выходами управляющего дешифратора, выход первого переключателя подключен к первым входам первого и второго пороговых усилителей и первому выводу первого нагрузочного элемента, второй вывод которого соединен с первым выходом первого источника опорного напряжения, выход второго переключателя подключен к первым входам третьего и четвертого пороговых усилителей и первому выводу второго нагрузочного элемента, второй вывод которого соединен с первым выходом второго источника опорного напряжения, вторые выходы источников опорного напряжения и вторые входы пороговых усил15,телей подключены к шине нулевого потенциала, выход первого порогового усилителя соединен с первыми входами первого и второго эле- , ментов ИЛИ-НЕ и элемента И, выходы второго и четвертого пороговых усилителей подключены соответственно к второму входу второго элемента ИЛИ-НЕ и к первому входу третьего элемента ИЛИ-НЕ, выход третьего порогового усилителя соединен с вторыми входами первого и третьего элементов ИЛИНЕ и элемента И и первым входом сумматора по модулю два, выход которого и выходы элементов ИЛИ-НЕ подключены к входам элемента ИЛИ, выход которого и выход элемента И являются контрольными выходами устройства, одними из входов которого являются соответственно второй вход сумматора по модулю два и входы управляющего дешифратора, вторые входы ключей обЬединены и являю ся другим входом устройства. Источники информации, принятые во внимание при экспертизе 1.Самофалов К.Г., Корнейчук В.И., Тородный А.В. Структурно-логические методы повышения надежности запоминаюЕЩх устройств. М., 1976, с.65-68, рис. 22-25. 2.Патент США № 3422402, кл. 340/173, опублик. 1968 (прототип),

х

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1982 |

|

SU1023393A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU959168A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Программируемое постоянное запоминающее устройство | 1980 |

|

SU886055A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-10—Подача