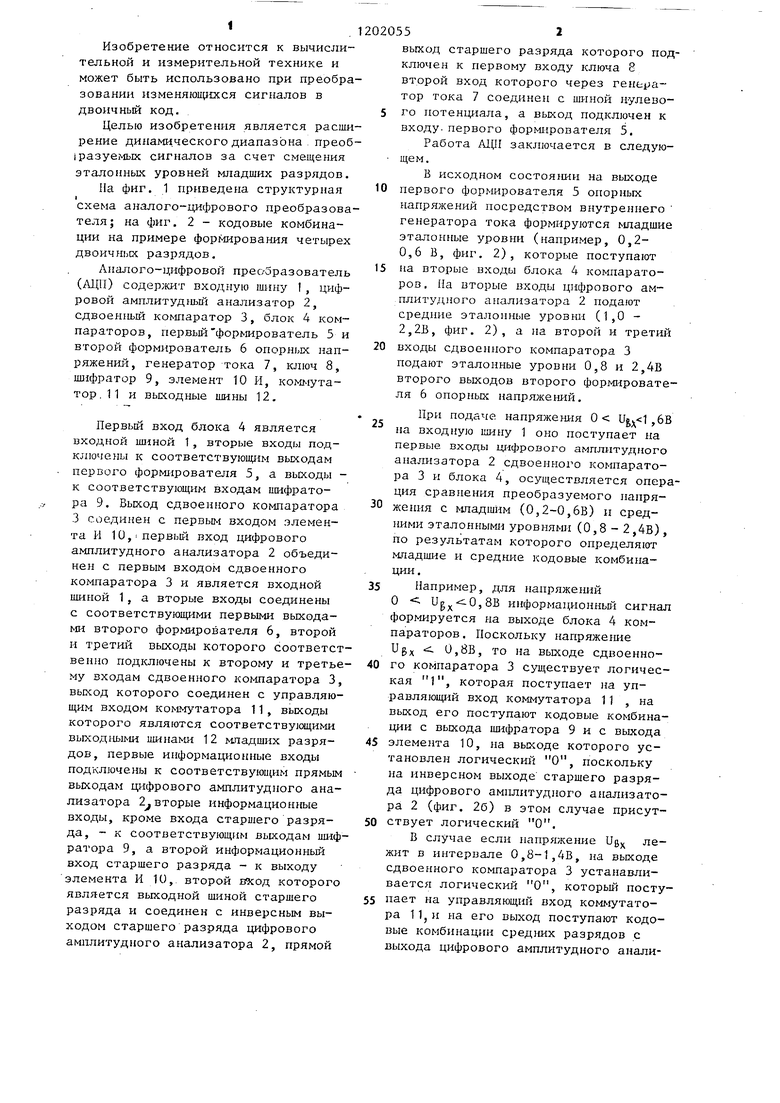

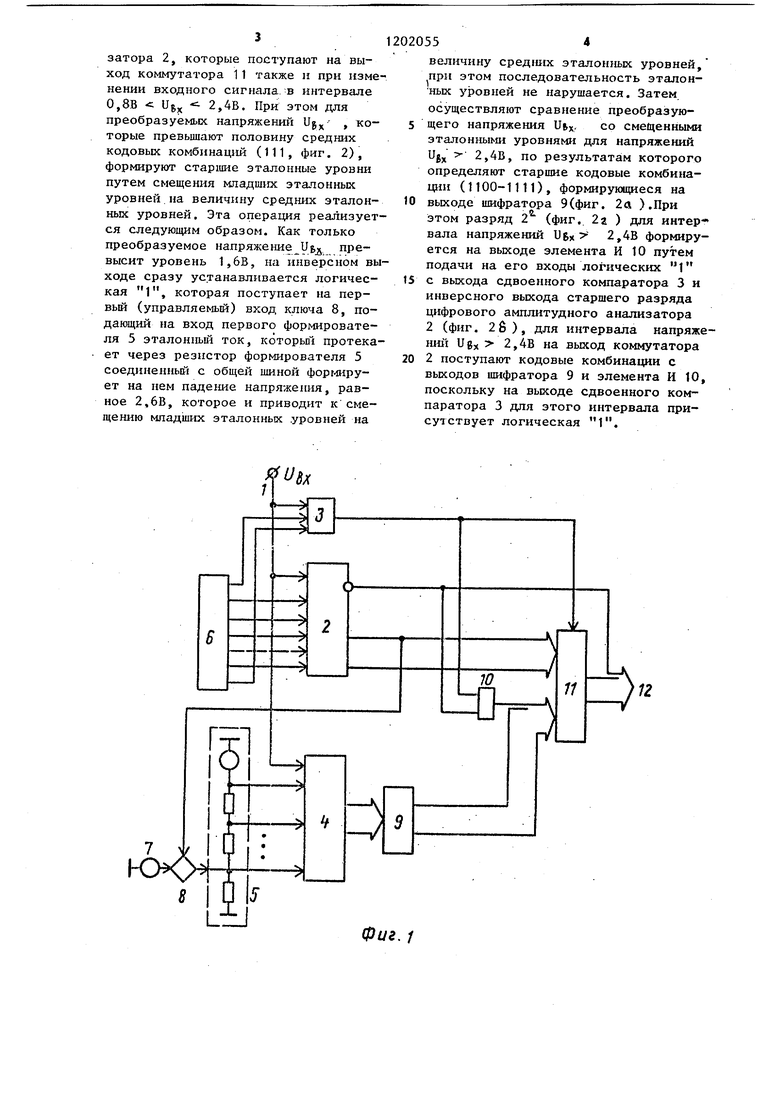

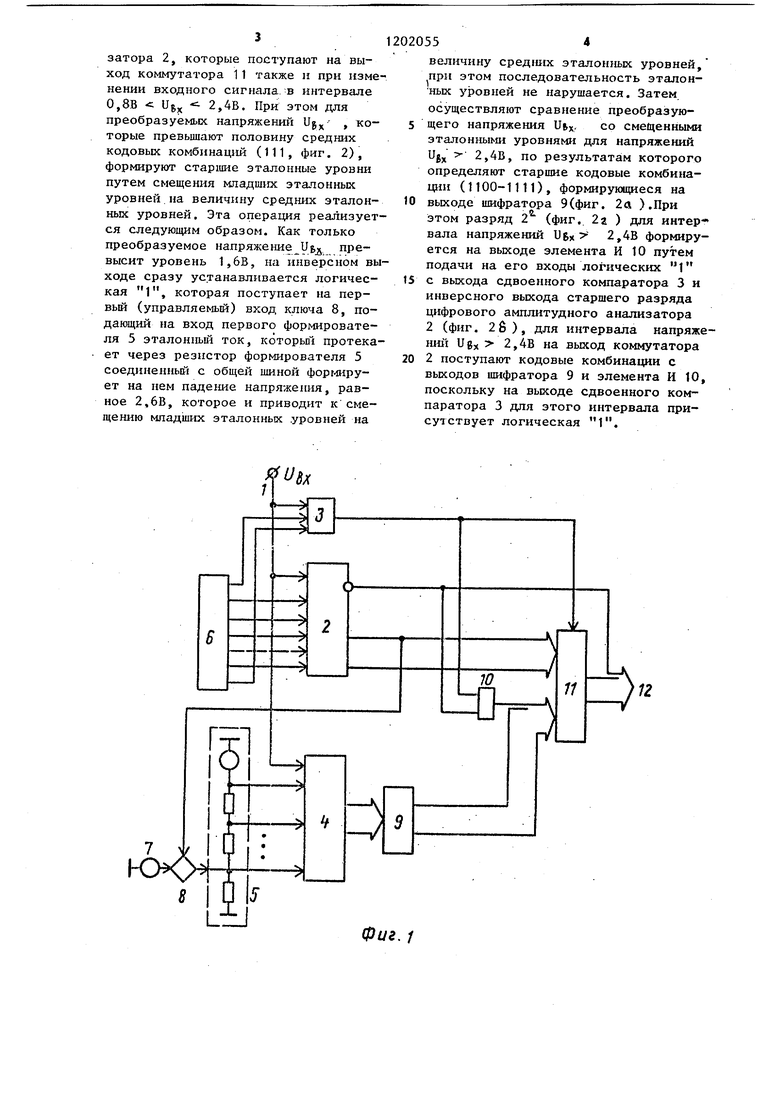

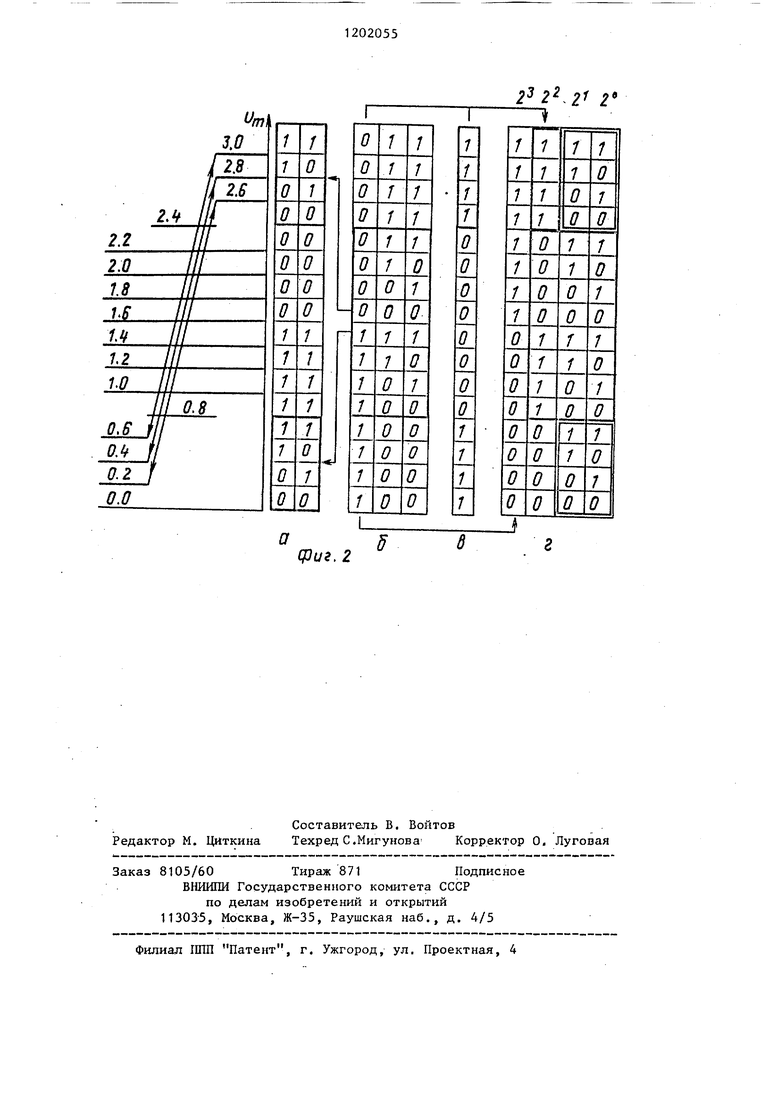

Изобретение относится к вычисли тельной и измерительной технике и может быть использовано при преобр зовании изменяюпцссся сигналов в двоичньй код. Целью изобретения является расш рение динами.ческого диапазона прео 1разуемых сигналов за счет смещения эталонньк уровней младших разрядов Па фиг. 1 приведена структурная схема аналого-цифрового преобразова теля; на фиг. 2 - кодовые комбинации на примере формирования четырех двоичных разрядов. Аналого-цифровой прес-оразователь (АЦП) содержит входную шину I, цифровой амплитудный анализатор 2, сдвоенный компаратор 3, блок 4 компараторов, первыйфop иpoвaтeль 5 и второй формирователь 6 опорных напряжений, генератор тока 7, ключ 8, шифратор 9, элемент 10 И, коммутатор . 11 и вьЕсодные шины 12, Первый вход блока 4 является входной шиной 1, вторые входы подключены к соответствующим выходам первого формирователя 5, а выходы к соответствующим входам иифратора 9. Выход сдвоенного компаратора 3 соединен с первым входом элемента И 10,iпервый вход цифрового амплитудного анализатора 2 объединен с первым входом сдвоенного компаратора 3 и является входной шиной 1, а вторые входы соединены с соответствуюш;ими первыми выходами второго формирователя 6, второй и третий вькоды которого соответст венно подключены к второму и третье му входам сдвоенного компаратора 3 вькод которого соединен с управляющим входом KOMJ-гутатора 11 , выходы которого являются соответству с«цими выход11ыми шинами 12 младших разрядов, первые информационные входы подключены к соответствующим прямым выходам цифрового амплитудного анализатора 2 вторые информационные входы, кроме входа старшего разряда, - к соответствующим выходам шиф ратора 9, а второй информационный вход старшего разряда - к выходу элемента И 10, второй вход которого является выходной шиной старшего разряда и соединен с инверсным выходом старшего разряда цифрового амплитудного анализатора 2, прямой 52 выход старшего разряда которого подключен к первому входу ключа 8 второй вход которого через генератор тока 7 соединен с шиной нухшвого потенциала, а выход подключен к входу.первого формирователя 5. Работа А1Ц1 заключается в следующем. В исходном состоянии на выходе первого формирователя 5 опорных напряжений посредством внутреннего генератора тока формируются младшие эталонные уровни (например, 0,20,6 В, фиг, 2), которые поступают на вторые входы блока 4 компараторов . На вторые входы цифрового амплитудного анализатора 2 подают средние эталонные уровни (1,0 2,2В, фиг, 2), а на второй и третий входы сдвоенного компаратора 3 подают эталонные уровни 0,8 и 2,4В второго выходов второго формирователя 6 опорных напряжений. При подаче напряжедаш 0 Ujj,1 ,6В на входную шину 1 оно поступает на первые входы цифрового амплитудного анализатора 2 сдвоенного компаратора 3 и блока 4, осуществляется операция сравнения преобразуемого папряжения с младшим (О,2-0,6В) и средними эталонными уровнями (0,8 - 2,4В), по результатам которого определяют младшие и средние кодовые комбинации, Например, для напряжений О ,8B информационньй сигнал формируется на выходе блока 4 компараторов , Поскольку напряже1ше Ugx то на выходе сдвоенного компаратора 3 существует логическая 1, которая поступает на управляющий вход коммутатора 11 , на выход его поступают кодовые комбинации с выхода шифратора 9 и с выхода элемента 10, на выходе которого установлен логический О, поскольку на инверсном выходе старшего разряда цифрового амплитудного анатшзатора 2 (фиг, 2б) в этом случае присутствует логический О. В случае если напряжение Ug лежит в интервале 0,8-1,4В, на выходе сдвоенного компаратора 3 устанавливается логический О, который поступает на управляющий вход коммутатора 11, и на его выход поступают кодовые комбинации средних разрядов с выхода цифрового амплитудного анализатора 2, которые поступают на выход коммутатора 11 также и при изменении входного сигнала.-в интервале 0,8В « и,5 2,4В. При этом для преобразуемых напряжении , которые превьшают половину средних кодовых комбинаций (111, фиг. 2), формируют старшие эталонные уровни путем смещения младших эталонных уровней.на величину средних эталонных уровней. Эта операция реализуется следующим образом. Как только преобразуемое напряжение Уг, превысит уровень 1,6В, на инверсном вы ходе сразу устанавливается логическая 1, которая поступает на первый (управляемый) вход ключа 8, подающий на вход первого формирователя 5 эталонньй ток, которьп протекает через резистор формирователя 5 соединенный с общей шиной форг-йфует на нем паде1ше напряжения, равное 2,6В, которое и приводит к смещению мпадших эталонных уровней на

2020554

величину средних эталонных уровней, при этом последовательность эталонных уровней не нарушается. Затем осуществляют сравнение преобразую5 щего напряжения иь, со смещенными эталонными уровнями для напряжений Ug 2,4В, по результатам которого определяют старшие кодовые комбинации (1100-1111), формирующиеся на

10 выходе шифратора 9(фиг. 2а ).При

этом разряд 2 (фиг. 2г ) для интер вала напряжений Ubx 2,4В формируется на выходе элемента И 10 путем подачи на его входы логических 1

15 с выхода сдвоенного компаратора 3 и инверсного выхода старшего разряда цифрового амплитудного анализатора 2 (фиг. 2б), для интервала напряжений Ugx 2,4В на выход коммутатора

20 2 поступают кодовые комбинации с выходов шифратора 9 и элемента И 10, поскольку на выходе сдвоенного компаратора 3 для этого интервала присутствует логическая 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Биполярный цифровой амплитудный анализатор | 1983 |

|

SU1208605A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Способ преобразования напряжения в код и устройство для его реализации | 1980 |

|

SU892706A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1193809A1 |

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок компараторор, первьпЧ вход которого является входной шиной, вторые входы подключены к соответствующим выходам первого формирователя опорных напряжений, а выходы - к соответствующим входам шифратора, сдвоенный компаратор, выход которого соединен с первым входом элемента И, отличающийс я тем, что,с целью расширения динамического диапазона преобразуемых сигналов, в него введены генератор тока, ключ, коммутатор, второй формирователь опорных напряжений и цифровой амплитудный анализатор, первый вход которого объединен с первым входом сдвоенного компаратора и является входной шиной, а вторые входы .соединены с соответствую1Ц11ми первыми выходами второго формирователя опорньк напряжений, второй и третий выходы которого соответственно подключены к второму и третьему входам сдвоенного компаратора, выход которого соединен с управляющим входом коммутатора, выходы которого являются соответствующими выходными шинами младших разрядов, первые информационные входы подключены к соответствующим прямым выходам цифрового амплитудного анализатора, вторые информационные входы, кроме входа старшес го разряда,:- к соответствующим б выходам шифратора, а второй информа(Л ционньй вход старшего разряда - к выходу элемента И, второй вход которого является выходной шиной старшего разряда и соединен с инверсным выходом старшего разряда цифрового амплитудного анализатора,прямой выход старto шего разряда которого подключен к первому входу ключа, второй вход которого to через генератор тока соединен с шиной нулевого потенциала, а выход о подключен к входу первого формироваСП теля опорных напряжешп. ел

ffUi

-

Гх1

toCH-F-

I О ш

LN

;/

1г

г/

-

-У

Фиг. 1

а

сриг.2

| Патент США № 3142056, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU651475A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-30—Публикация

1983-08-31—Подача