(54) ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

| Запоминающее устройство | 1979 |

|

SU824304A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU599265A1 |

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015384A1 |

| Устройство для обработки информации | 1973 |

|

SU624232A1 |

| Адаптивный коммутатор системы телеизмерений | 1979 |

|

SU773671A1 |

| Микропрограммное устройство управления | 1981 |

|

SU999052A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления корня -ой степени | 1977 |

|

SU742929A1 |

1

Предлагаемое изобретение относится к области цифровой вычислитепьной технмки.

Известны цифровые вычиспитетшные уст ойства дпя выполнения рекуррентных процедур, содержащие ряд регистров и сумматор, производящие в каждом итерационном цикле вычисления согласно рекуррентному выражению l.

Очевидно, что быстродействие таких устройств существенно зависит от спож.ности. реализуемой процедуры.

Наиболее близким техническим решением к предложенному является известное устройство, содержащее постоянный запоминающий, блок, регистр адреса, числовой регистр, блок управления, три элемента И, причем первый- вход регистра адреса соединен с выходом первого элемента И, первый вход которого подключен ко входу устройства, выход регистра вареса соединен с первым вхо дом постоянного запоминающего блока, выход которого подключен ко входу

числового регистра, выход которого подключен к первым входам второго и третьего элементов И, выход второго элемента И подключен ко второму входу регистра адреса, выход третьего элемента И подключен к выходу устройства, первый, второй и третий выходы блока управления соединены со вторыми входами соответственно первого, второго и третьего элементов И Г2.

Недостатком известного устройства является узкий класс решаемых задач,

Цепью предлагаемого устройства является обеспечение возможности вьт- полнения рекуррентных процедур.

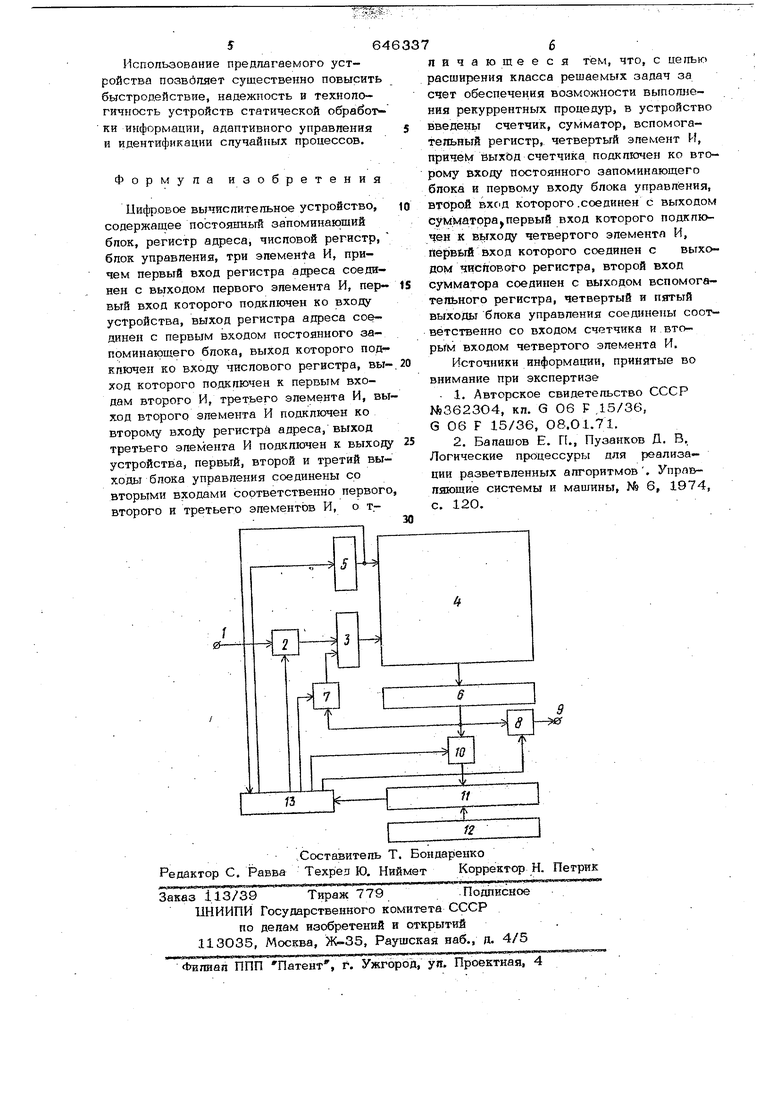

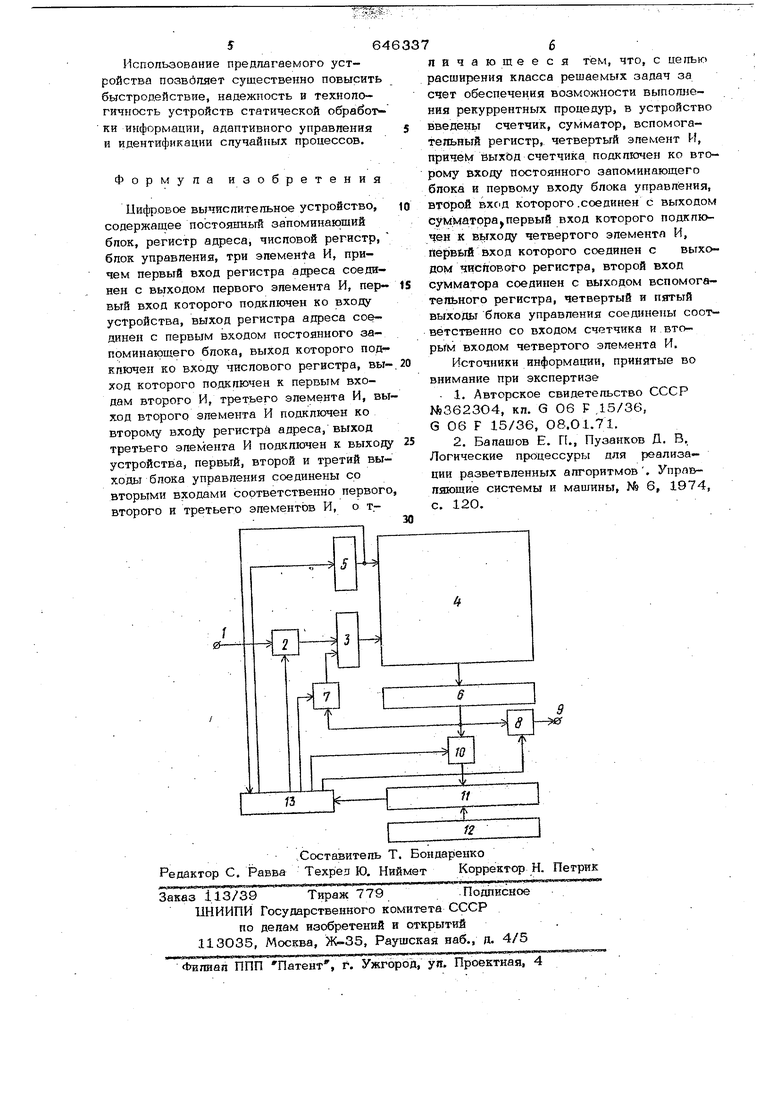

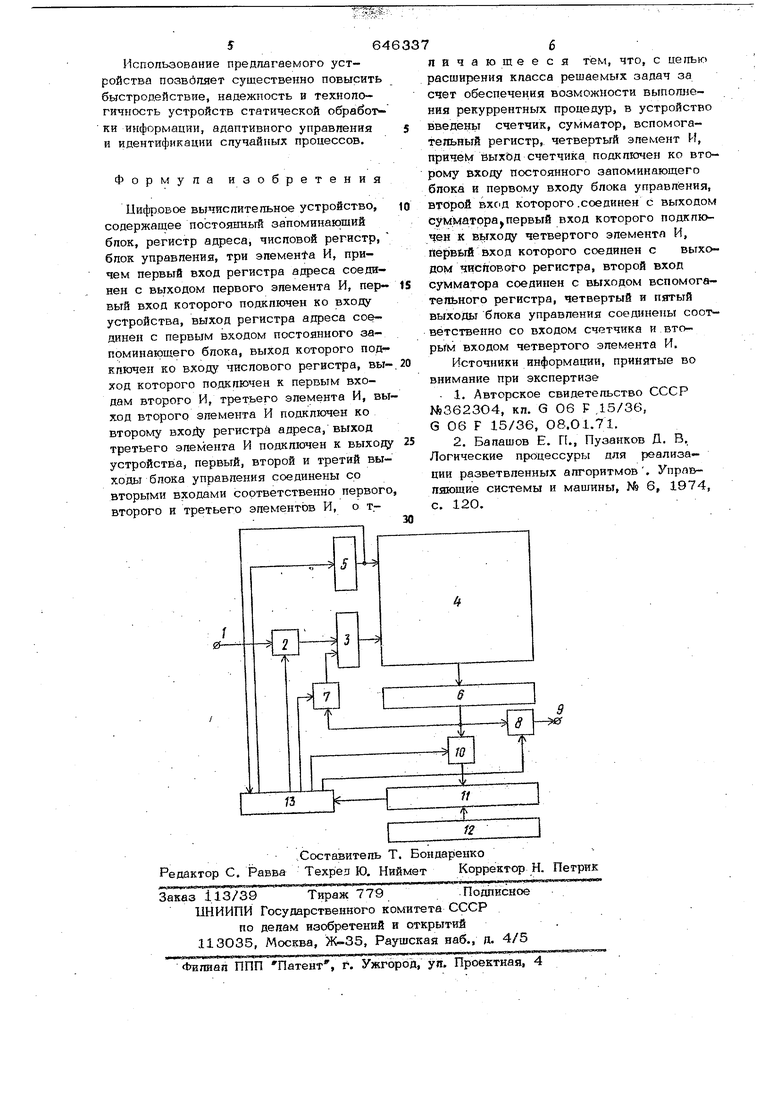

Поставленная цель достигается тем, что в устройство введены счетчик, сумматор, вспомогательный регистр, четвертый элемент И, причем выход счетчика подк.лючен ко второму входу пос-. тоянного запоминающего блока и первому входу блока управления, второй вход которого соединен с выходом сумматора, первый вход которого подключен к выходу четвертого элемента И, первый вход которого соединен с ьыходом числового регистра, второй вход сумматора соединён с выходом вспомогательного регистра, четвертый и пятйй выходы бйЬка управления соединены соответственно со входом счетчика и вторым входом четвертого элемента И. На чертеже приведена структурная сх.ема цифрового вычислитепьного устройства, Цифровое вычислительное устройство содержит вход устройства, 1, первый эл мент И 2, регистр 3 адреса, ттостоянный запоминающий блок 4, счетчик 5, числовой регистр 6, второй элемент И 7 третий элемент И 6, выход устройства 9 четвертый элемент И 10, сумматор 11, вспомогательньгй регистр 12, блок упра ления 13. Работа устройства происхойит в Двух режимах; режиме простого счета и режиме счета с проверкой на останов. В режиме простого счета каждый итеративный цикл состоит из двух тактов. В первом так;те по сигналам из блока управления 13 на регистр адреса 3 заносится текущее (жачение переменной итеративного процесса со входа уст „ ройства 1 через элемент И 2 и .текущее значение рекуррентной функции с числов го регистра 6 через элемент И 7, к содержимому счетчика 5 прибав-пяется единица. Во втором такте происходит считывание очередного значения рекуррентной функции из постоянного запоминающего блока на числовой регистр 6. На определенном шаге итерации, номер которого зависит от характера сходимости процедуры, происходит переход в режим счета с проверкой на останов. При этом в первом такте текущего итерационного цикла по сигналам из блока управления 13 из числового регистра 6 на сумматрр 11 через элемент И 1О и на регистр адреса 3 через элемент И 7 передается текугйее значение рекуррентной функции, кроме того на регистр адреса 3 через элемен И 2 со входа устройства 1 передается текушее значение пере1 енной итеративного процесса., а к содержимому-счетчнп ка 5 прибавлается единица. Во- втором такте из йостоянного запоминаюшего блока считывается следующее значение рекуррентной функции. В режиме счета с проверкой на останов каждый цикл итерации состоит ИЗ четьфех тактов. В первом такте на регистр адреса 3 через эпемент И 2 со входа устройства 1 и через блок элемента И 7 из числового регистра 6 передается текущее значение рекуррентной функции, к содержимому счетчика 5 прибавляется единица и в сумматоре 11 происходит вычисление абсототной величины разности текущего значения рекуррентной функции, передаваемого через элемент И. 10 из числового регистра 6, и предыдущего значения. Во втором такте из содержимого сумматора 11 вычитается содержимое 1вспомогательного регистра 12. Знак результата вычитания анализируется блоком управления 13, и если выполняются останова, то в третьем такте из числового регистра 6 через элемент И 8 на выход устройства выдается значение рекуррентной, функции и работа вычислительного устройства прекращается. Если условия останова не выполняются, то в третьем такте происходит передача текущего значения рекуррентной функции из числового регистра 6 в сумматор 11 через элемент И 10. В четвертом такте из постоШйого запоминающего блока 4 считы- ; йается следующее значение рекуррентной функции. Условием останова рекуррентной процедуры является наличие последовательности определенной длины отрицательных результатов вычитания уставки из абсолютной величины разности значений рекуррентной функции в двух соседних шагах итерации. П р и м ,е р. Пусть - требуется оценить математическое ожидание случайного процесса X. (-t)- Известная рекуррентная формула определения этой оценки имеет вид . гй(:к+о(к-л скихск-и1)/(), (.1) где К « 1,2,3.... На (К + 1)-ом щаге итерации по адресу, составленному из номера шага (К+1), текущего значения переменной X (К -fl) и результата пре-. дыдущего шага /( П X , из постоянного запоминающего блока выбирается значение fl fK-f-l . Номер шага итерации, с которого начинается счет с проверкой на останов, в данном случае зависит от требуемой точности вычислений и дисперсии оцениваемого процесса, 6 Использование предпигаемого устройства позвбпяет существенно повысить быстродействие, надежность и техно логичность устройств статической обработки информации, адаптивного унравпения и идентификации случайных процессов. рмупа иаоб р е т е н и я Цифровое вычиспитепьное устройство, содержащее постоянный запоминающий блок, регистр адреса, числовой регистр, бпок управпения, три sneMeHta И, нричем первый вход регистра адреса соединен с выходом первого элемента И, первый вход которого подключен ко входу устройства, выход регистра адреса соединен с первым входом постоянного запоминающего бпока, выход которого подключен ко входу числового регистра, выход которого подкпючен к первым входам второго И, третьего эпемента И, вы ход второго эпемента И подкпючен ко второму Bxoriy регистра адреса, выход третьего эпемента И подкпючен к выходу устройства, первый, второй и третий выходы бпока управпения соединены со вторыми входами соответственно первого второго и третьего элементов И, о т7пинающееся тем, что, с цепью расширения кпасса решаемых задач за счет обеспечения возможности выпошюния рекуррентных процедур, в устройство введены счетчик, сумматор, вспомогательный регистр, четвертый эпемент И, причем выхЬд счетчика подкпючен ко второму входу постоянного запоминающего бпока и первому входу бпока управпения, второй вход которого .соединен с выходом сумматора,первый вход которого подкпючен к вьтходу четвертого эпементп И, йервьтй вход которого соединен с выходом чиспового регистра, второй вход сумматора соединен с выходом вспомогательного регистра, четвертый и пятый выходы бпока управпения соединены соответственно со входом счетчика и вторым входом четвертого эпемента И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетепьство СССР №362304, кп. G Об Р 15/36, G 06 F 15/36, 08.01.71. 2. Бапашов Е. П., Пузанков Д. В. огические процессуры для реализации разветвпенных алгоритмов , Управпяющие системы и машины, Кэ 6, 1974 . 120.

Авторы

Даты

1979-02-05—Публикация

1977-03-29—Подача