(54) ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

| Цифровой интегратор | 1976 |

|

SU720427A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Цифровой интегратор | 1978 |

|

SU698017A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1977 |

|

SU734745A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

I

Изобретение относится к вычислительным устройствам систем управления и может быть использовано в системах числового программного управления станками и другим технологическим оборудованием.

Известно устройство, содержащее регистр подинтегральной функции, счетчик тактовых импульсов и комбинационный блок из элементов И-ИЛИ 1.

Недостатком такого устройства является наличие комбинационного блока, число элементов которого растет с увеличением разрядности регистра подинтегральной функции.

Наиболее близким к изобретению по технической сущности является цифровой интегчратор, содержащий блок преобразования подинтегральной функции, первый элемент И, блок итерации и программный блок, содержащий регистр сдвига, сумматор, первый вход которого подсоединен к выходу блока итераций, второй вход - к выходу регистра сдвига, а первый выход - к входу регистра сдвига, элемент задержки, входом соединенный с вторым выходом сумматора, второй элемент И, первый вход которого соединен с выходом элемента задержки, второй вход соединен с выходом блока итераций, а выход подсоединен к третьему входу сумматора, первый вход первого элемента И подсоединен к первому выходу сумматора, второй вход первого элемента И подсоединен к выходу регистра сдвига, третий вход первого элемента И подсоединен к выходу блока преобразования подинтегральной функции, а выход - к выходной шине. При этом второй элемент И включает непосредственно элемент И и элемент- НЕ 2.

Недостаток такого интегратора - большие затраты аппаратурных средств на реализацию программного блока, содержащего сумматор и сложные связи.

Целью изобретения является сокращение оборудования.

Указанная цель достигается тем, что в цифровом интеграторе, содержащем регистр подинтегральной функции, регистр сдвига, блок итераций, элементы И, НЕ, задержки, причем первый вход первого элемента И соединен с выходом регистра подинтегральной функции, а выход является выходом интегратора, второй вход первого элемента И, первый вход второго элемента И и вход блока итераций соединены с выходом

элШёнта задержки, вход которогочерез элемент НЕ соединен с выходом регистра сдвига, выход и второй вход второго элемента И соединены соответственна с входом первого разряда регистра сдвига и первым выходом блока итераций, второй выход которого соединен с управляющими входами регистра подинтегральной функции и регистра сдвига, выход которого соединен с его информационным входом.

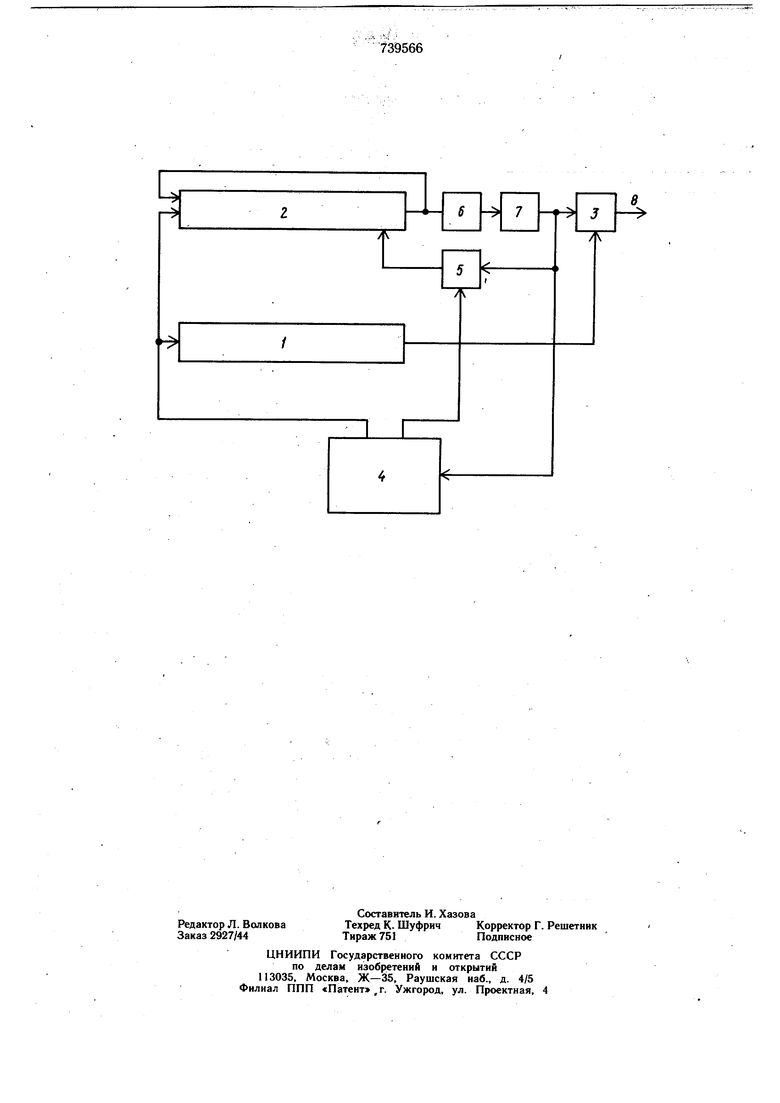

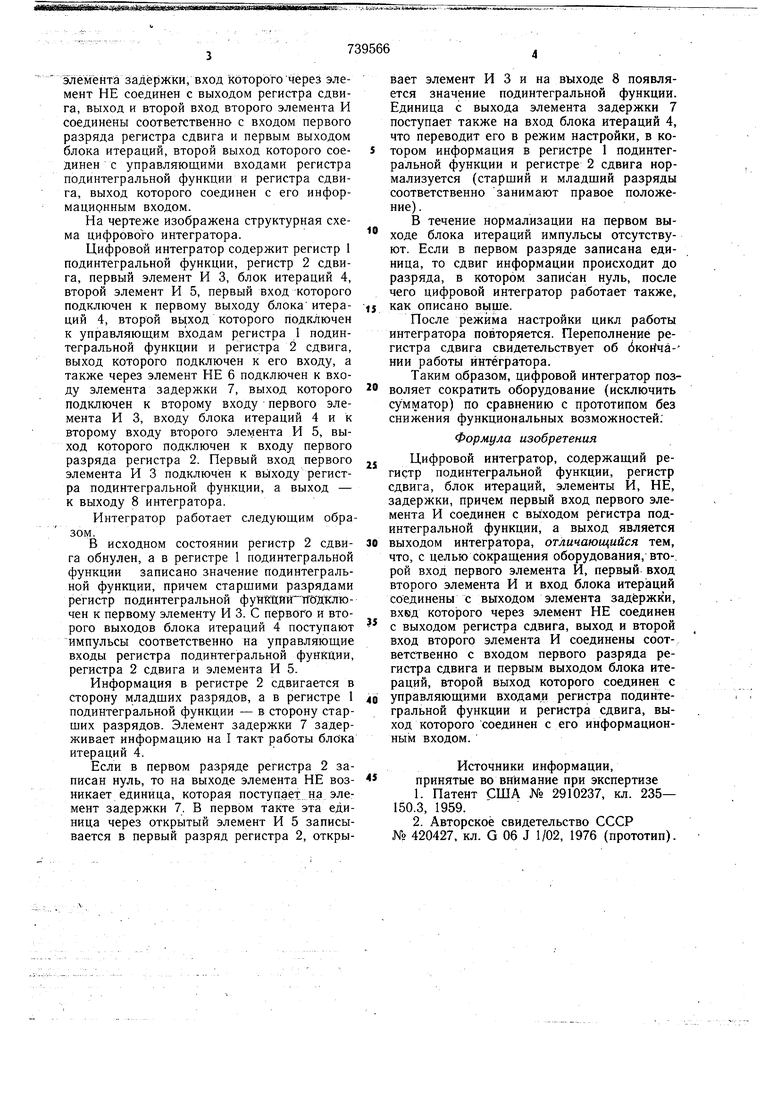

На чертеже изображена структурная схема цифрового интегратора.

Цифровой интегратор содержит регистр 1 подинтегральной функции, регистр 2 сдвига, первый элемент И 3, блок итераций 4, второй элемент И 5, первый вход которого подключен к первому выходу блока итераций 4, второй выход которого подключен к управляющим входам регистра 1 подинтегральной функции и регистра 2 сдвига, выход которого подключен к его входу, а также через элемент НЕ 6 подключен к входу элемента задержки 7, выход которого подключен к второму входу первого элемента И 3, входу блока итераций 4 и к второму входу второго элемента И 5, выход которого подключен к входу первого разряда регистра 2. Первый вход первого элемента И 3 подключен к вь1ходу регистра подинтегральной функции, а выход - к выходу 8 интегратора.

Интегратор работает следующим образом.

В исходном состоянии регистр 2 сдвига обнулен, а в регистре 1 подинтегральной функции записано значение подинтегральной функции, причем старщими разрядами регистр подинтегральной фунщт тг&дасяючен к первому элементу И 3. С первого и второго выходов блока итераций 4 поступают импульсы соответственно на управляющие входы регистра подинтегральной функции, регистра 2 сдвига и элемента И 5.

Информация в регистре 2 сдвигается в сторону младщих разрядов, а в регистре 1 подинтегральной функции - в сторону старщих разрядов. Элемент задержки 7 задерживает информацию на I такт работы блбка итераций 4.

Если в первом разряде регистра 2 записан нуль, то на выходе элемента НЕ возникает единица, которая поступает на элемент задержки 7. В первом такте эта единица через открытый элемент И 5 записывается в первый разряд регистра 2, открывает элемент И 3 и на выходе 8 появляется значение подинтегральной функции. Единица с выхода элемента задержки 7 поступает также на вход блока итераций 4, что переводит его в режим настройки, в котором информация в регистре 1 подинтегральной функции и регистре 2 сдвига нормализуется (старщий и младщий разряды соответственно занимают правое положение).

В течение нормализации на первом выходе блока итераций импульсы отсутствуют. Если в первом разряде записана единица, то сдвиг информации происходит до разряда, в котором записан нуль, после чего цифровой интегратор работает также,

как описано выше.

После режима настройки цикл работы интегратора повторяется. Переполнение регистра сдвига свидетельствует об бкойчаНИИ работы интегратора.

Таким образом, цифровой интегратор позволяет сократить оборудование (исключить сумматор) по сравнению с прототипом без снижения функциональных возможностей:

Формула изобретения

Цифровой интегратор, содержащий регистр подинтегральной функции, регистр сдвига, блок итераций, элементы И, НЕ, задержки, причем первый вход первого элемента И соединен с вьгходом регистра подинтегральной функции, а выход является

выходом интегратора, отличающийся тем, что, с целью сокращения оборудования, вто-. рой вход первого элемента И, первый вход второго элемента И и вход блока итер;аций соединены с выходом элемента задержки, вхкд которого через элемент НЕ соединен с выходом регистра сдвига, выход и второй вход второго элемента И соединены соответственно с входом первого разряда регистра сдвига и первым выходом блока итераций, второй выход которого соединен с

управляющими входами регистра подинтегральной функции и регистра сдвига, выход которого соединен с его информационным входом.

Источники информации, принятые во внимание при экспертизе

№ 420427, кл. G 06 J 1/02, 1976 (прототип).

t

Авторы

Даты

1980-06-05—Публикация

1978-01-04—Подача