I

Изобретение относится к области вычислительной техники и может быть использовано при построении цифровых интегрирующих машин на однородных структурах.

Известен интегратор 17. содержащий регистры, сумматоры и вентильные группы.

Низкое быстродействие такого интегратора обусловлено выполнением на шаге интегрирования трех последовательных по времени умножений.

Известен цифровой интегратор 2, содержащий регистры, сумматор и группы элементов И.

Недостатком устройства является низкое быстродействие, обусловленное нерациональньм способом обработки информации и малой совмещаемостью операций.

Наиболее близким по технической сущности к изобретению является цифровой - интеграторlE 32, содержащий регистр подинтегральной функции.

регистр 1-го приращения функции, регистр (i-fljt-ro приращения функции, регистр остатка, пять сумматоров, три элемента задержки, преобразоватетель кода, коммутатор, блок умножения, регистр суммы приращений. Выход регистра подинтегральной функции соединен с первым входом первого сумматора, выход которого соединен со входом регистра подинтеграпьной функции, и через элемент задержки с первым входом второго сумматора. Второй вход первого сумматора подклкл чен к выходу регистра Г-го приращения функции. Второй вход второго сумг матора соединен с выходом регистра (i +1)-го приращения функции. Выход регистра остатка соединен с первым входом коммутатора,, первый выход которого соединен со входом блока умножения, а второй - с первым входом третьего сумматора. Выход блока умножения соединен со вторым входом третьего сумматора, выход которого

соединен со входом регистра cystMbi приращений, выход которого соединен со вторым входом коммутатора. Вход преобразователя кода подключен к выходу l(i + l)-ro приращения, а выход - к третьему входу коммутатора. Выход второго сумматора соединен с первым входом второго сумматог ра и через второй элемент задержки - со вторым входом четвертого сумматора, выход которого через третий элемент задержки соединен с первым входом пятого сумматора, Выход регистра f-го приращения функции соединен со вторым входом пятого сумматора, выход которого соединен с четвертьш входом коммутатора.

В известном устройстве реализуется алгоритм численного интегрирования по методу квадратных парабол, который имеет следующий вид :

Y .

VH

vSrtUD / -NvNprtHi) .)).

дч -TV

: prc- ) .q,ri. .Emiiil&4ri.

дТ

AY

u4

f Sii+) -I iKiiiLLn Srrci D .

VV 7м; д Vo 111-ff +

+2М1 .2 к1111„„- jjH r -1 Mlmiiji. iv Ja ду -fir f ili:-- -

Недостатком этого устройства является низкое быстродействие, обусловленное в основном вычислением на шаге интегрирования трех последовательных во времени умножвний.

Цель изобретения является повьшение быстродействия.

Поставленная адль достигается тем, что в цифровом интеграторе, содержащем регистр подинтегральной функции, регистр -го приращения функции, регистр (п+1)-приращен функции, первый сумматор первый элемент задержки, второй сумматор, второй элемент задержки, третий сумматор и блок умножения, причем выход регистра подинтегральной функции соединен с первым входом cyMiiaropa, вход- с выходом первого сумматора, второй вход котого соединен с выхо- дом регистра 1-го приращения функции, а выход - со входом первого элемента задержки, выход которого подключен к первому входу второго сумм.чтора, выход которого со.адинен

со входом нт(1рс)гс- элемента задержки, выход которого соединен с первым входом третьего сумматора, вход регистра (п+1)-го приращения подклю-

чен ко входу приращения функции интегратора, первый вход блока умножения подключен ко входу приращений аргумента, выход первого сумматора соединен со вторым входом второго сумматора, выход регистра i-го приращения функции соединен со вторым входом третьего сумматора, а выход регистра (i+l)-ro приращения функции соединен со входом регистра

.i-ro приращения функции, третьим входом второго сумматора и третьим входом третьего сумматора, выход которого соединен со вторым входом блока умножения, выход которого является выходом интегратора.

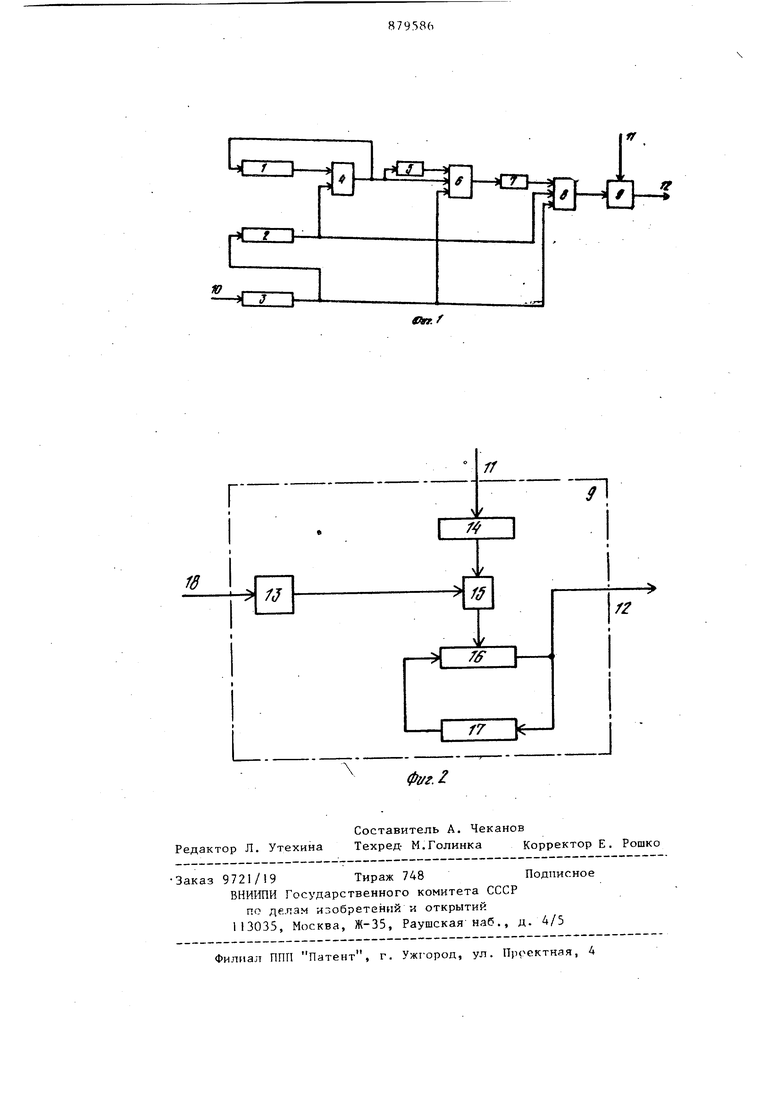

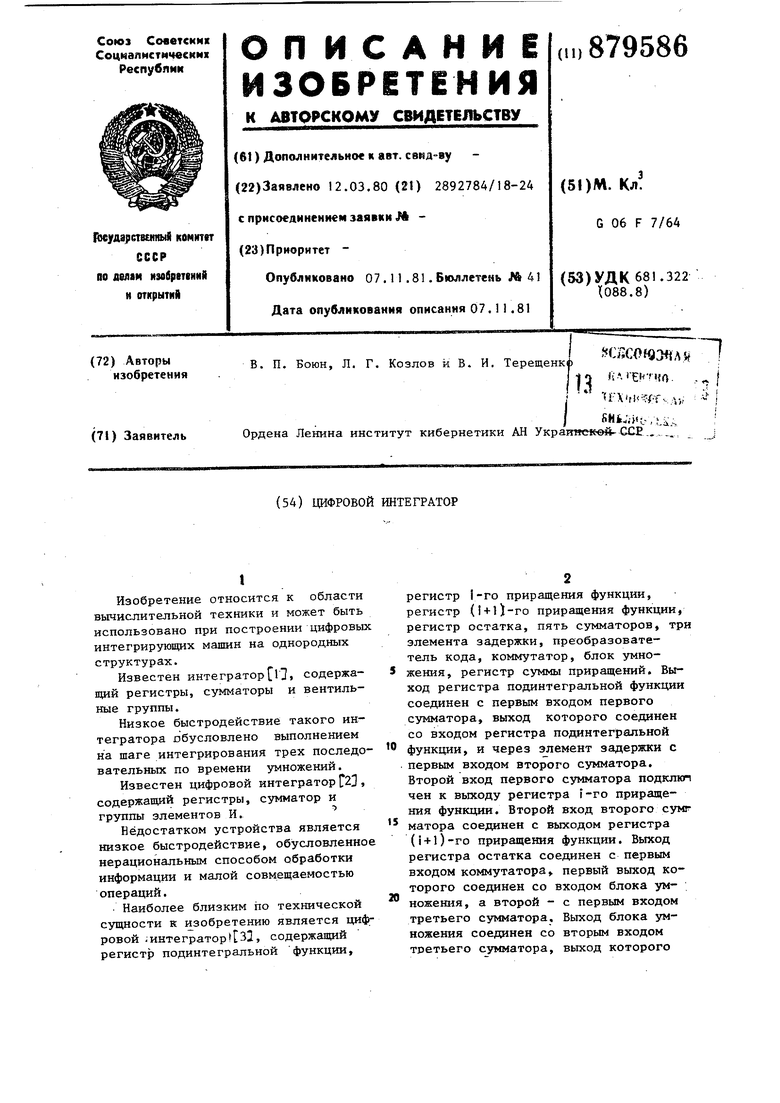

На фиг.1 представлена структурная схема цифрового интегратора ; на фиг. 2 - структурная схема блока , умножения.

Цифровой интегратор состоит из регистра 1 подинтегральной функции, регистра 2 i-ro приращения функции, регистра 3 (i+l)-ro приращения функции, первого сумматора 4, первого Элеменга задержки 5, второго сумматора б, второго элемента задержки 7, третьего сумматора 8 и блока умножен:, ния 9, вход 10 приращения функции, вход 11 приращения аргумента интегратора.

Блок умножения состоит из буферного регистра 13, регистра множимого 14, блока элементов И-НЕ 15, суммато: ра 16, регистра остатка 17, первый вход 18 блока умножения.

Предлагаемое устройство выполняет интегрирование по формуле квадратичных парабол :

Av,f((W-T

гдеДЗу и -приращение интеграла в г-м интеграторе в i-и точке интегрирования;

у -значение подинтегральной функции г-м интеграторе

в 1-й точке интегрирования; дУр. -приращение подинтегральной функции в г-м интеграторе в i-й точке ингегрирования;

дх -шаг интегрирования. Устройство работает следующим образом.

Перед началом работы интегратора значение заносится в регистр множимого блока умножения 9, в регистр подинтегральной функции 1 заносит-гся значение подинтегральяой функции регистр i-ro приращения функции 2 - приращение ДУу- в регистр (i+1)-приращения функции 3 - приращение )Величина у Ц егистра 1 и при-; ращение йу/,; с регистра 2 поступают на первый сумматор 4. На выходе сумматора 4 образуется новое значение подинтегральной функции yfn ..которое записывается в регистр 1. Величина Ууч поступает также на второй вход сумматора бис задержкой на.один такт через элемент задержки 5 на первый вход сумматора 6, на третий вход которого поступает приращение

).

На выходе сумматора 6 образуется

величинй(3 (, , которая с за держкой на два такта через элемент задеряЕки 7 поступает на первый вход сумматора 8. На второй вход сумматора 8 поступает с регистра 2 величина ДУр , а на третий -величина ЛУу.ь4)С регистра 3. На выходе сумматора 6 образуется величина

1

ni+iH 4 Х; Т«

(

h

Y(

которая поступает на второй вход блока умножения 9. В блоке умножения вычисляется приращение интеграла ./(j,

Во время вычислений код из регистра 3 переписывается в регистр 2. По окончании шага интегрирования величина приращения интеграла (4/() из блока умножения поступает на выход 12 интегратора. На следующем шаге интегрирования величина входа 10 интегратора поступает в регистр 3i Вычисления на всех последуютих шагах интегрирования повторяются аналогично .

В блоке умнсжнния 9 осуществляется умножение на Е разрядов множителя, так как обработка одного разряда множителя в блоке умножения 9 определяется быстродействием п-разрядного сумматора, а получение одного разряда этого множителя в предшествующем узле - быстродействием одноразрядного сумматора. Огуществляется умножение на Е разрядов множителя за счет введения в блок умножения буферного регистра. Верхний предел размера буферного регистра в битах определяется соотношением

«О

пбыстродейс твие

п.-разрядногдего сумматора; Г быстродействие

однор аз ряднго сумматора.

Буферный регистр 13 сотоит из дву разрядов. Два разряда множителя, находящиеся в регистре 13, считываются с него и поступают на блок элементов И-НЕ. Умножение осуществляется известным способом: умножение содержимого регистра множимого 14 на два раряда множителя. За время сложения в сумматоре 16 в буферном регистре накапливается два новых разряда множителя .

Регистр остатка 17 введен для повщения точности интегрирования. При сдвиге кода в сумматоре 16 сдвигается соответственно и код в регистре 1 младшие разряды которого записываются на место освободившихся разрядов в сумматоре 16, а младшие разряды результата из сумматора 16 - на место освободившихся разрядов в регистре 17.

Таким образом,за время получения произведения будут выполнены суммирование остатка интеграла с этим произведением и запись нового остатка в регистр 17. Значение приращения интеграла находится в сумматоре 16.

Определим быстродействие устройства прототипа и предлагаемого устройства.

Основное время затрачивается на операции умножения. В устройствепрототипа на щаге интегрирования выполняются три операции умножения, поэтому время выполнения шага интегрирования равно

Т.,

где п- разрядность множителя;

t- быстродействие сумматора. В предлагаемом устронстре на шаге интегрирования выполняется одно умножение. Умножение выполняется на 7 разрядов множителя. Время выпопне ния шага интегрирования равно Предлагаемое устройство позволит повысить быстродействие, например, при t 2 -в l..n-tc .ex3ex6pa4. Повышение производительности ста возможным благодаря введению новых связей, Формула изобретения 1, Цифровой интегратор, содержащий регистр подинтегральной функции, регистр -f-ro приращения функци регистр (1 + 0-го приращения функции первый сумматор, первый элемент задержки, второй ciiMMaTOp, второй элемент задержки, третий сумматор, и блок умножения, причем выход регистра подинтегральной функции соединен с первым входом первого сумма тора, вход - с выходом первого сумматора, второй вход которого соедикен с вьгкодом регистра, -го приращения фг.гнкции, а выход - с входом первого элемента задержки, выход ко ,торого подключен к первому входу в iporo суг-шатора выход которого сое.дивен с входом второго элемента задержки, выход которого соединен с первым входом третьего сумматора, вход регистра (I + l)-ro приращения ф кции подключен к входу приращения функции интегратора, первый вход бл ка умножения подключен к:входу 6 приращений аргумента интегратора, о т л н ч а ю ев, и и с я тем, что, с целью повышения быстродействия, выход первого сумматора соединен с вторым входом второго сумматора, выход регистра i-ro приращения функции соединен с вторым входом третьего сумматора, а выход регистра (i+l)-ro приращения функции соединен с входом регистра i-ro приращения функции, с третьим входом второго сумматора и с третьим входом третьего сумматора, выход которого соединен с вторым входом блока умножения, выход которого является выходом интегратора, 2. Интегратор по п. 1, отличающийся тем, что блок умножения содержит буферный регистр, регистр множимого, регистр остатка, блок элементов И-НЕ и сумматор., причем выход буферного регистра соединен с первьш Входом блока элементов И-НЕ, второй вход которого соединен с выхог. дом регистра множимого, а выход соединен с первым входом сумматора, второй вход которого соединен с выхо-/ дом регистра остатка, а выход сумматора - с входом регистра остатка к вьЕХОдом блока умножения, вход регистра множимого соединен с первым входом блока умножения, а выход буферного регистра - с вторым входом этого блока. Источники информахдаиS принятые во внимание экспертизе 1 Авторское свидетеольство СССР № 369590, кл. J 1/02, 1971. 2 Авторское свидетельство СССР № 637833 кл, G 06 J 1/02, 1977. 3, Авторское свидетельство-СССР № 4537Г1, кл. G Об J i/02, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

Авторы

Даты

1981-11-07—Публикация

1980-03-12—Подача