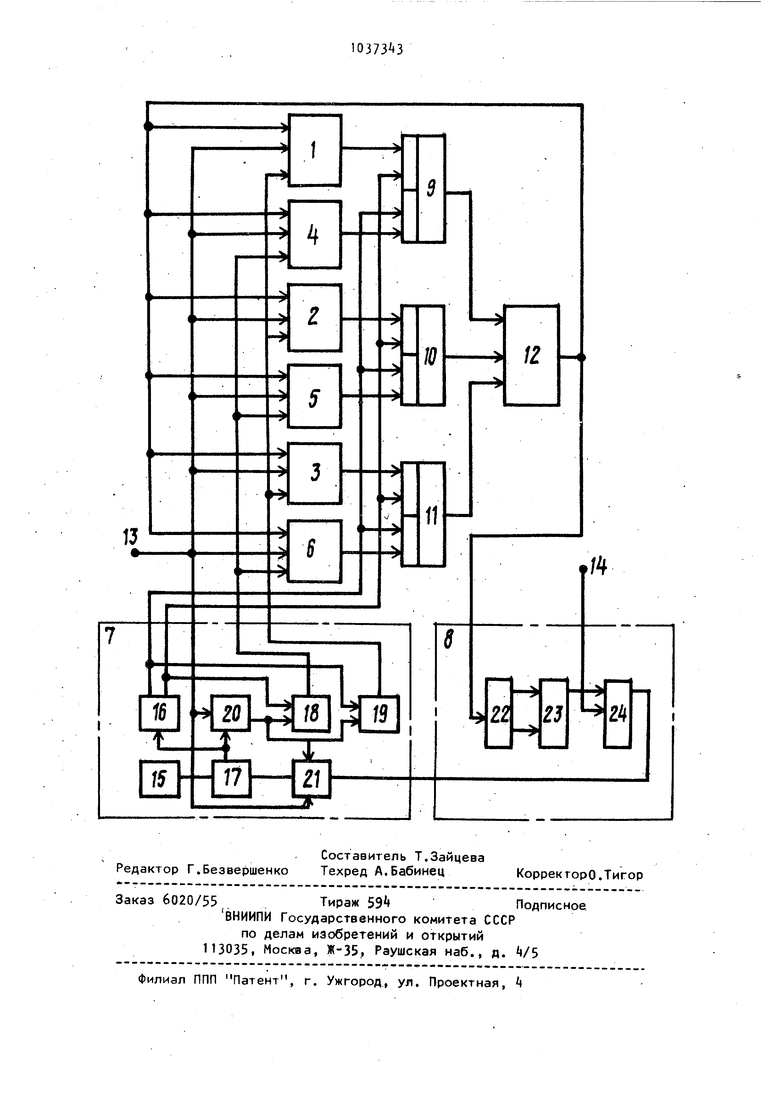

Изобретение относится к вычислительной технике и можег быть исполь зовано в цифровых управляющих систе мах и комплексах, к которым предъяв ляются высокие требования к их наде ности и безотказной работе в течени длительного срока эксплуатации. Известно резервированное запоми,нающее устройство, которое содержит три идентичных канала, выходы которых через мажъритарный блок подключены к исполнительным органам С1 J. Недостатком этого устройства является снижение надежности при длительном сроке эксплуатации. Наиболее близким техническим решением к изобретению является резер вированное запоминающее устройство, содержащее блоки памяти, выходы кот рых через мажоритарный блок подключены к входам регенерации блоков па мяти 2. Недостатками известного устройст ва являются недостаточное время непрерывной работы,возможность частич ной или полной потери информации пр выходе из строя элементов или п.ри возникновении однократного сбоя в в узлах регенерации информации блоков памяти, особенно при работе а тяжелых условиях эксплуатации,, резких изменениях климатических условий, условиях повышенных помех, что снижает надежность устройства. I , Дель изобретения - повышение надежности резервированного запоминающего устройства. Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее основные блоки памяти и мажоритарный блок,выход которого соединен с вхо дами регенерации основных блоков памяти, введены вычислитель контрольной суммы, блок пере(лючения каналов, дополнительные блоки памяти и элементы 2И-ИЛИ, первые и вторые входы которых подключены соответственно к выходам основных и дополнительных блоков памяти, выходы к входам мажоритарного блока, а третьи и четвертые входы - соответственно к первому и второму выхо-/ дам блока переключения каналов, тре тий и четвертый выходы которого сое динены соответственно с первыми управляющими входами основных и допол нительных блоков памяти, щ первый вход подключен к вторым управляющим входам основных и дополнительных блоков памяти и является входом обращения устройства, причем входы регенерации дополнительных блоков памяти соединены с выходом мажоритарного блока и входами вычислителя контрольной суммы, выход которого подключен к в-торому входу блока переключения каналов, а управляющий вход, является входом сигнала последнего адреса устройства. Кроме того, блок переключения каналов содержит регистр, первый три|- гер, элемент ИЛИ, элементы И и генератор временных сигналов, выход которого подключен к.первому входу элемента ИЛИ, выход которого соединен с установочным входом регистра и счетным входом первого триггера, выходы которого подключены соответственно к первым входам первого и второго элементов И, вторые входы которых соединены с выходом регистра и первым входом третьего элемента И, выход которого подключен к второму входу элемента ИЛИ, а второй вход соединен со счетным входом регистра и является первым входом блока, вторым входом которого является третий вход третьего элемента И, выходами блока с первого по четвертый являются соответственно первый и второй выходы первого триггера и выходы первого и второго элементов И При этом вычислитель контрольной суммы содержит второй триггер, элемент И-НЕ и сумматор по модулю два, входы которого являются входами вычислителя, а выходы соединены с входами элемента И-НЕ, выход которого подключен к первому входу второго триггера, второй вход и выход которого являются соответственно управляющим входом и выходом вычислителя. На чертеже представлена функциональная схема предлагаемого устройства. Резервированное запоминающее устройство содержит основные 1-3 и дополнительные 4-6 блоки памяти, блок 7 переключения каналов, вычислитель 8 контрольной суммы, первый 9i второй 10 и третий 11 элементы 2И-ИЛИ и мажоритарный блок- 12, вход 13 обращения и вход I сигнала последнего адреса. Блок переключения каналов содержит генератор 15 временных си|- налов, первый триггер 16, элемент 3 или 17, первый 18 и второй 19 эл менты И, регистр 20 и третий элемен И 21. Вычислитель контрольной суммы содержит сумматор 22 по модулю два, элемент И-НЕ 23 и второй триггер . Устройство-выполнено на стандарт ных элементах типа 1601РР26. Устройство работает следующим об разом. В исходном состоянии в блоки 1-6 по всем адресам записывается иденти ная информация. По последнему адрес записывается контрольное число. Три геры 16 и 2k и регистр 20 находятся в положении О. По первому сигналу Обращение на входе 13, поступающему на управляющие входы блоков 1информация из блоков 1-3 памяти через элементы 2И-ИЛИ и блок 12 поступает на вход сумматора 22, в к тором накапливается, и на информационные входы блоков 1-6. При этом на первые управляющие, входы блоков,1-6 с выходов элементо И 18 и 19 поступает сигнал О, запрещающий регенерацию информации. В случае если информация, считан ная ,из блоков 1-3 памяти, правильная, на выходах сумматора 22 будут единичные сигналы высокого уровня, которые через элемент И-НЕ 23, инве тируясь, поступают на первый вход триггера 2k, на второй вход 1 кото рого поступает сигнал последнего адреса. Таким образом, если информация, полученная с блоков 1-3 правильная, по последнему адресу подве ждается состояние О триггера 24, Сигнал О которого запрещает прохо дение второго сигнала Обращение с входа 13 через элементы И 21 и ИЛИ 17 на вход триггера 16. Второй сигнал Обращение переключает регистр 20 в положение Два, при котором сигнал с его выхода через элемент И 18 поступает на первые управляющие входы блоков -6, разрешая в них регенерацию информации сигналами из блоков 1-3 памяти. В случае, если информация, полученная с выходов блоков 1-3 неправильная, на выходах сумматора 22 по окончании опроса зафиксируется число, не соответствующее 1 во всех разрядах. Сигнал последнего адреса 1 переключает триггер 2k в состояние 1 Второй сигнал Обращение с входа 13 устанавливает регистр 20 в состоя ние О и через элементы И 21 и ИЛИ 17 переключает триггер 1б в протиаЪположное состояние. При этом информация с.выхо,.ов блоков+-6 поступает в вычислитель 8. Если информация правильная, следующий сигнал .Обращение переключает регистр 20 в состояние Два, причем сигнал с его выхода через элемент И 18 разрешает перезапись (регенерацию) информации из блоков -6 в блоки 1-3, т.е. вычислитель 8, зафиксировав ошибку в информации в блоках 1-3, с помощью блока 7 производит корректировкуинформации в этих блоках. Сигнал с выхода генератора 15 (период которого выбирвется исходя из условий эксплуатации и должен быть меньше времени, гарантирующего сохранность информации в блоках 1-6) через элемент ИЛИ 17 поступает на вход триггера 1б и установочный вход регистра 20, переключает триггер 16, который поочеред-. но разрешает регенерацию информации из блоков 1-3 в блоки «-6 и обратно. Таким образом, построение резервированного запоминающего устройства по данной структуре при первом обращении позволяет проконтролировать выходную информацию, по второму обращению осуществить - перезапись ( регенерировать) информацию в резервные блоки памяти, в случае выхода из строя узлов регенерации или какого-либо сбоя, и произвести запрет регенерации и переключение каналов блоков памяти. Это позволяет исключить потерю информации, увеличить время непрерывной работы и повысить надежность резервированного запоминающего устройства. Время непрерывной работы без потери информации увеличивается до времени гарантированного ресурса работы накопительного элемента (10000 ч) так как в каждом блоке памяти происходит обновление информации через время, равное периоду регенерации, задаваемому генератором 15, и при периоде регенерации до 100 ч время сохранности информации в блоках 1-6 УДб соответствовать времени максимальной наработки 10 ч (т.е. ресурсу работы накопительного элемента) при количестве циклов перезаписи информации, не превышающем заданное в ТУ на накопительный элемент. Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой надежности по сравнению с и звестным.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

Л

24

Авторы

Даты

1983-08-23—Публикация

1982-05-31—Подача