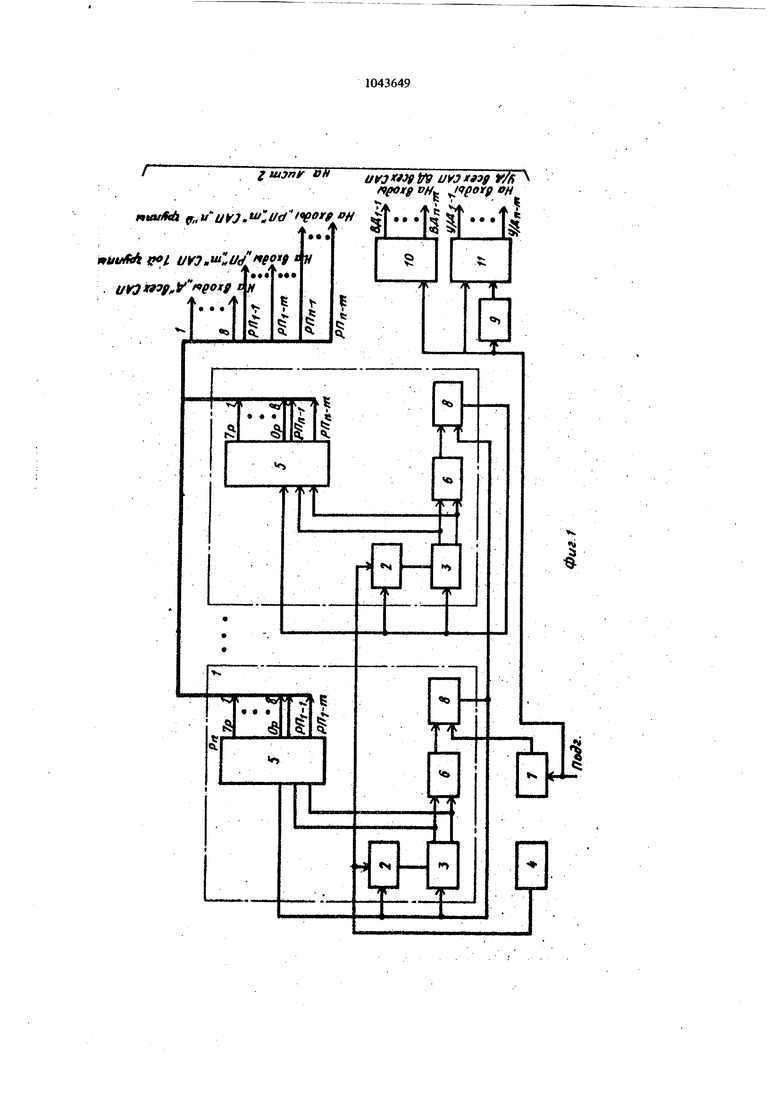

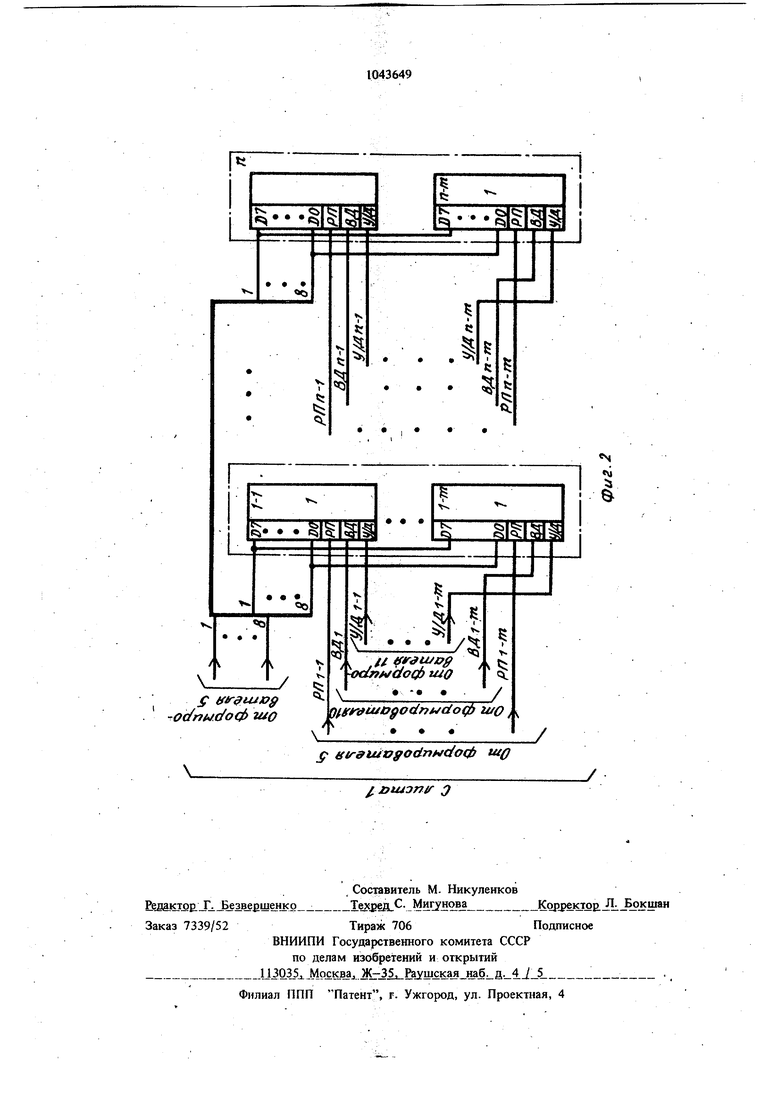

Изобретение относится к вычислительной. технике и предназначено для программировани синхронно-асинхронных приемопередатчиков, являющихся преобразователями последовательного кода в параллельной и параллельного в последовательный. Известен преобразователь последовательного кода в параллельный, представляющий собой обычный регистр сдвига 1 . Недостатком такого преобразователя является его малые функциональные возможности: преобразование кодовых слов с определенным шслом разрядов, равным числу разрядов регистра сдвига; невозможность проверки на четность принятых кодовых комбинаций. Наиболее близким к предлагаемому является вычислительное устройство, содержащее генератор тактовых импульсов, выход которого соединен с входом процессора, выход процессора соединен с выходами постоянных запоминающих устройств, оперативных запоминаю щих устройств и синхронно-асинхронных прие мопередатчиков, выходы постоянных запоминающих устройств, входы (выходы) оперативных устройств и первые (входы) выходы синхронно-асинхронных приемопередатчиков соединены с входом.;(выходом) процессора, BTOpbie (входы) выходы синхронно-асинхронных Приемопередатчиков являются входами (выходами) устройства. Процессор содержит первый буферный запоминающий блок, первый вход (выход) которого является (входом) выходом процессору, второй вход (выход) соединен с первыми входами первого регистра вход (выход) дешифратора соединен с входом (выходом) счетчика, выход счетчика соединен с первым входом второго буферного запоминающего блока, первый и второй выходы деи1ифратора соединены соответственно с входом блока управления и вторым входом первого регистра, выход первого регистра соединен с входами третьего и четвертого регистров и вторым входом второго буферного запоминающего блока, выход которого является выходом процессора, выходы третьего и четвертого регистров соеданены соответственно с первым и вторым входами арифметическо-логического блока, выход которого соединен с вторым входом (выходом) первого буферного запоминающего блока. В этом устройстве за счет использования синхронно-асинхронных приемопередатчиков расишряются функциональные возможности преобразования последовательного кода в параллельный и параллельного в последовательный 2.. Однако для программирования синхронноасинхронных приемопередатчиков на определенный режим работы используется процессор, что снижает эффективность (быстродействие) работы всего вычислительного устройства в целом и, в частности, программируемых синхронноасинхронных приемопередагшков. Цель изобретения - повыщение быстродействия работы программируемых синхронно-асинхронных приемопередатчиков. Поставленная цель достигается тем, что в устройство для программного управления синхронно-асинхронными приемопередатчиками, содержащее генератор тактовых импульсов и в каждом узле управления счетчик, дешифратор, введены формирователь импульсов, инвертор, первый и второй формирователи кодов и в каждом узле управления формирователь кода, делитель частоты и триггер, первый вход первого формирователя кода .объединен с входами формирователя импульсов, инвертора и второго формирователя кода и подключен к входу устройства, выход инвертора соединен с вторым входом первого формирователя кода, выход генератора тактовых импульсов соединен с первыми входами делителей частоты всех узлов управления, в каждом узле управления выход делителя частоты соединен с первым входом счетчика, первый и второй входы которого, соединены соответственно с первыми и вторыми входами дешифратора и формирователя кода, выход дешифратора соединен с первым входом триггера, выход триггера соединен с вторыми входами делителя частоты, счетчика и третьим входом формирЬвателя кода, выход формирователя импульсов соединен с вторым входом триггера первого узла управления, выход триггера каждого предыдущего узла управления соединен с вторым входом триггера каждого последующего узла управления, первые входы формирователей кода всех узлов управления объединены и подключены к первым выходам устройства, вторые входы формирователей кода ка одого узла подключены к в.торым вь1ходам устройства, выходы первого и второго формирователей кода соединены соответственно с третьим и четвертым выходами устройства. На фиг. 1 и 2 представлена структурная схема предлагаемого устройства. Устройство содержит программируемые синхронно-асинхронные приемопередатчики 1, делители 2 частоты, счетчики 3, генератор 4 .тактовых импульсов, формирователи 5 кода, дешифраторы 6, формирователь 7 импульсов, RS-триггер 8, инвертор 9, формирователи 10 и И кода. Устройство работает следующим образом. При включении устройства генератор 4 начинает генерировать импульсы. После отсчета трех импульсов на выходе счетчика 3 появится код 11, который вызывает срабатывание дешифратора 6, )кидываю1него триггер 8 в состояние 1. Формирователи 5, 10 и II устанавливаются в третье состояние (выходы их отключены). Для приведения приемопередатчиков 1 в рабочее состояние в ка-.дый из них должны быть последовательно записаны два кода: код № 1 - инструкция режима и код N 2 - инструкция команды, которые определяют режим работы преобразователей 1. Например, допустим, что приемопередатчики первого ряда должны работать в следующем режиме: число информационных бит в слове 8; производится контроль четности; длина стопбита равна двум битам; частота синхронизации в 64 раза больше скорости поступления информации из канала связи. Тогда код № 1 ЩПЩ ; код N 2 - ХОХХХ1ХХ ; где X - безразлично 1 или О.. Задаем код № 2 10111111. В шестом разряде сначала должна быть записана 1, а затем О. Те же условия - по три числа информационных бит в слове, равном 5, - будут вьшолняться при записи следующих кодов: код № 1 - 11110011 и код N° 2 - 10110111. Таким образом, программирование приемопередатчиков I сводится к записи в каких-либо разрядах сначала 1, а затем О или наоборот. i

Рассмотрим процесс программирования первой группы приемопередатчиков 1 для работы с 8-битовыми словами. Выход первого разряда счетчика 3 соединен р входом формирователя 5, имитирующего сигнал разрешения на прием (РП). Выход второго разряда счегшка 3 соединен с входом формирователя 5, обеспечивающим запись в шестой разряд приемоггередатчиков 1 сигнала О или 1. В качестве формирователей 5, 10 и И используются микросхемы К 564ЛН1, имеюише три состояния на выходе. По сигналу Под1-отовка, который

выдается, например, центральным процессором или другим внецшим устройством управления,

срабатывает одновибратор 7, вырабатывается короткий импульс, длительность которого меньше длительности импульса, снимаемого с выхода второго разряда счетчика 3. Импульсом одновибратора 7 опрокидывается триггер 8, открывая делитель 2 частоты и счегтк 3 для прохождения импульсов от генератора 4 и по1ц лючая входы формирователя 5 к. своим выходам. Одновременно по сигналу Подготовка подключаются входы, формирователей 10 и 11 к своим выходам, подавая сигналы выдачи данных (ВД) и управление/данныв (УД) на соответствующие входы приемопередатчиков 1. После отсчета трех импульсов срабатывает .дешифратор 6, возвращая триггер 8 первого узла управления в исходное состояние. При зтом срабатывает триггер 8 второго узла управления и режим записи повторяется для приемопередатчиков второй группы. В зависимости от коммутации входов формирователей 5 обеспечивается нужный режим работы приемопередатчиков 1. После программирования последней группьЕ приемопередатчиков, сигнал Подготовка снимается и формирователи 5 и 10 приводятся в третье состояние. Формирователь 11 обеспечнвает на выходах состояние логического нуля, что нужно для последующей работы приемопередатчиков 1 в режиме приема информации из каналов связи.

Коммутация входов формирователей 5, выполненных на интегральных микросхемах серии К564, к тому или иному потенциалу источника 1Штания и выходам счетчика 3 производится с помошью распаиваемых перемычек в зксплуатирующей организавди, что значительно упрощает перепрограммирование устройства при изменении режима работы приемопередатчиков 1. Применение отдельного устройства для программирования синхронно-асинхронных приемопередатчиков 1 освобождает центральный процессор от выполнения этой функции, повышая :)ффективность его работы и следовательно быстродействие преобразователей последовательного кода в параллельной и параллельного в последовательной.

ftaynir ON i/yjje jftfff иууя938 /K

nfOJffVf/ 9fOrfOH

A A

if ffiuoffOdnMdoftJ taff

V

/

f,JDUJ3nir 0

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВ | 1992 |

|

RU2040118C1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

УСТЮЙСТВО ДЛЯ ПЮГРАММНОГО УПРАВЛЕНИЯ СИИХЮН1НЮ-АСИНХЮННЫМИ ПРИЕМОПЕРЕДАТЧИКАМИ, содержащее генератор тактовых импульсов и в каждом узле управления счетчик и дешифратор, отличающееся тем, что, с целью повышения быcтpoдeйctвия работы устройства, в него введены формирователь импульсов, инвертор, . первый и второй формирователи кодов и в узле управления формирователь кода, делитель частоты и триггер, первый вход перк вого формирователя кода объединен с входами формирователя импульсов, инвертора и второго формирователя кода и подключен к входу устройства, выход инвертора соединен с вторым входом первого формирователя кода, выход генератора тактовых импульсов соединен с первыми входами делителей частоты всех узлов управления, в каждом узле управления выхдд делителя частоты соединен с парт вым входом счетчика, первый и второй выходы которого соединены соответственно с первыми и вторыми входами дешифратора и формирователя кода, выход дешифратора соединен с первым входом триггера, выход, тригю гера соединен с вторыми входами делителя частоты, счетчика и третьим входом формирователя кода, выход формирователя импульсов соединен с вторым входом триггера первого i узла управления, выход триггера каждого предыдущего узла управления соединен с вто(Л рым входом триггера каждого последующего узла управления, первые выходы формирователей кода всех узлов управления объединены и подключены к первым выходам устройства, вторые выходы формирователей кода каждого узла управления подключены к вторым выходам устройства, выходы первого и второго 4;: формирователей кода соединены соответственно СО с третьими и четвертыми выходами устройства. Од QD

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Тепляков И | |||

| М | |||

| Радаотелеметрия | |||

| М., Советское радио, 1966, с | |||

| Кулиса для фотографических трансформаторов и увеличительных аппаратов | 1921 |

|

SU213A1 |

| Парный рычажный домкрат | 1919 |

|

SU209A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Балашов Е | |||

| П | |||

| и Пузанков Д | |||

| В | |||

| Микропроцессоры и микропроцессорные системы | |||

| М., Радио и связь, 1981, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Раздвижной паровозный золотник со скользящими по его скалке поршнями и упорными для них шайбами | 1922 |

|

SU147A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1983-09-23—Публикация

1982-02-15—Подача