Изобретение относится к вычислительной технике и может быть использовано в электрически программируемом постоянном запоминающем устройстве с Х-образным размещением лавинно-инжекционных транзисторов с плавающими и управляющими затворами, нашедших широкое применение в вычислительных машинах, устройствах автоматики, микропроцессорах.

Цель изобретения - повышение надежности матричного накопителя.

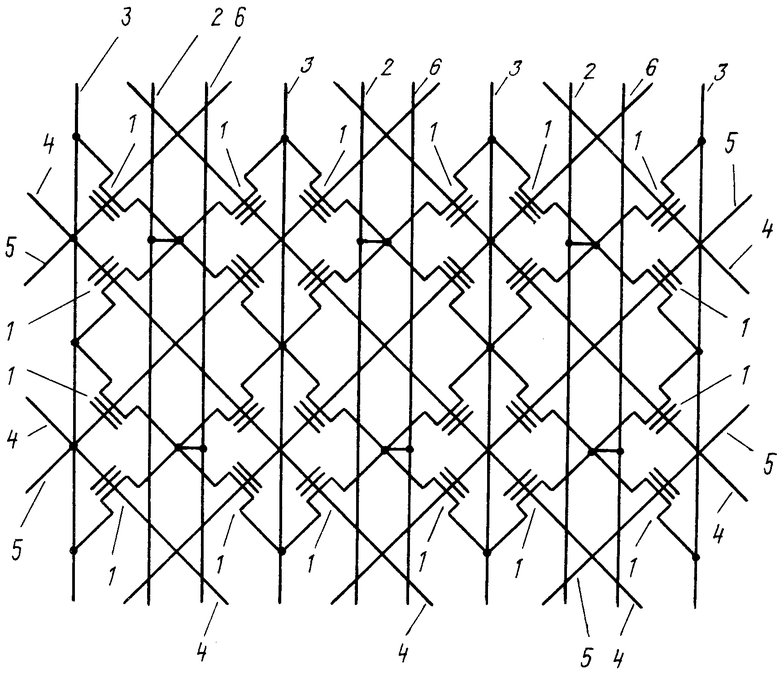

Накопитель содержит ячейки памяти на четырех запоминающих транзисторах 1 с плавающим затвором, первую группу разрядных шин 2, вторую группу разрядных шин 3, две группы адресных шин 4 и 5 и третью группу разрядных шин 6.

Сущность работы матричного накопителя заключается в следующем. В режиме считывания информации на выбранные разрядные шины 2 и 6, на адресную шину 4 или 5 подают низкое положительное напряжение. На разрядные шины 3, на невыбранные адресные шины 4 и 5 и невыбранные разрядные шины 2 и 6 подают нулевое напряжение.

Если пороговое напряжение выбранных запоминающих транзисторов 1 не превышает (превышает) напряжение на адресной шине 4, 5, то через него, выбранную разрядную шину 2, 6 и постоянно заземленную разрядную шину 3 протекает (не протекает) ток, что эквивалентно единичному (нулевому) состоянию.

Через остальные запоминающие транзисторы выбранных столбцов ток не протекает из-за нулевого напряжения на адресной шине 4 или 5, нулевой разности напряжений между разрядными шинами 2 и 6 и 3 соответственно.

Стирание информации во всех ячейках памяти осуществляют ультрафиолетовым облучением матричного накопителя в течение 30 мин, в результате чего происходит исчезновение заряда на плавающих затворах всех запоминающих транзисторов 1, пороговые напряжения становятся низкими, что эквивалентно единичному состоянию в режиме считывания информации.

Выборочное программирование нулевых состояний ячеек памяти проводится следующим образом. На выбранную адресную шину 4 или 5 подают высокое положительное импульсное напряжение (+12 В, 10 мс), на остальные адресные шины 4, 5 - нулевое напряжение. На выбранные разрядные шины 2 и 6 через нагрузки подают высокое положительное импульсное напряжение, на остальные невыбранные разрядные шины 2 и 6 и на разрядные шины 3 - нулевое напряжение.

Под действием высоких напряжений на управляющих затворах и стоках выбранных запоминающих транзисторов 1 при заземленных их истоках происходит инжекция горячих электронов из их каналов, захват электронов плавающими затворами, что приводит к увеличению пороговых напряжений выбранных запоминающих транзисторов 1.

Состояния остальных запоминающих транзисторов сохраняются неизменными из-за нулевых напряжений на адресных шинах 4 и 5 или нулевых напряжений на разрядных шинах 3.

Таким образом, при Х-образном размещении ячеек памяти обеспечивается повышение надежности из-за возможности поддержания постоянного нулевого напряжения на разрядных шинах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1405575A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1989 |

|

SU1642886A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

| НАКОПИТЕЛЬ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1995 |

|

RU2106022C1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

Изобретение относится к вычислительной технике и может быть использовано в электрически программируемом ПЗУ на основе транзисторов с плавающим затвором. Цель изобретения - повышение надежности накопителя. Цель достигается тем, что накопитель содержит третью группу разрядных шин 6 с соответствующими связями. Введение третьей группы разрядных шин 6 позволяет поддерживать постоянное нулевое напряжение на разрядных шинах 3 второй группы и, следовательно, на истоках запоминающих транзисторов 1. В результате при проведении программирования накопителя в невыбранных транзисторах 1 не происходит нежелательного изменения порогового напряжения. 1 ил.

| Electronies | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1994-12-30—Публикация

1986-07-16—Подача