ю

О5

ю

4;

(Х

Изобретение относится к вычислительной технике и может быть иснользовано для построения высоконадежных систем оперативной памяти микро-ЭВМ большой информационной емкости.

Целью изобретения является повышение достоверности функционирования.

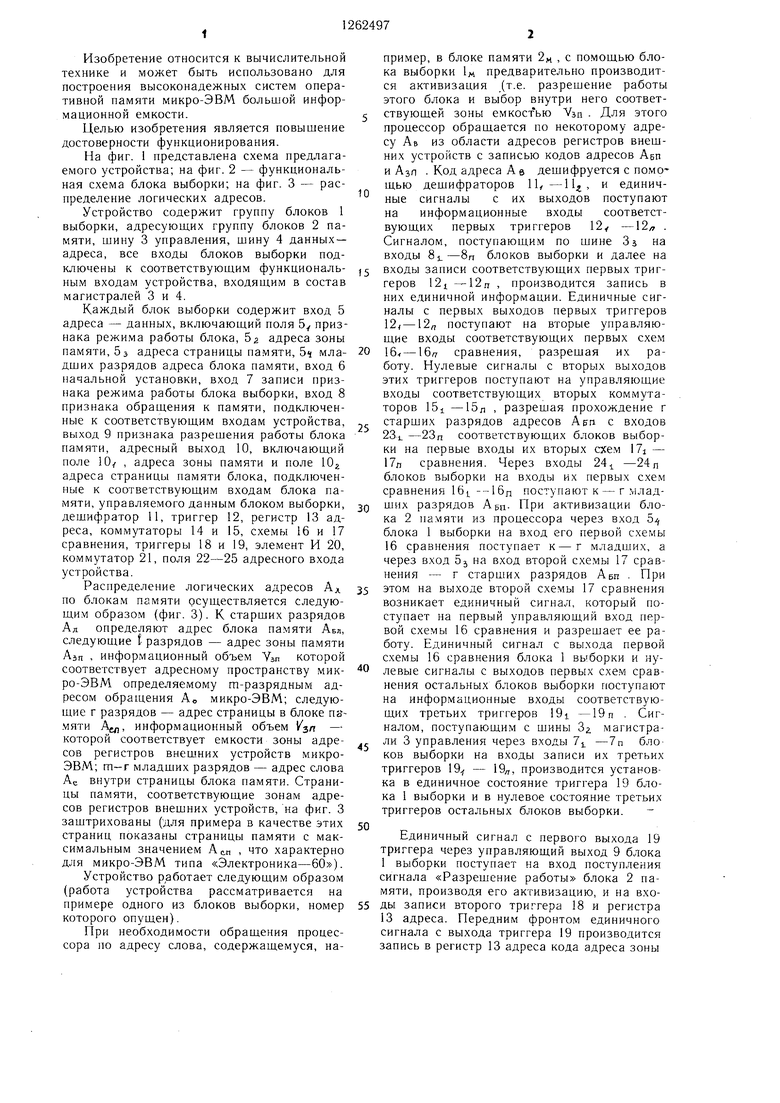

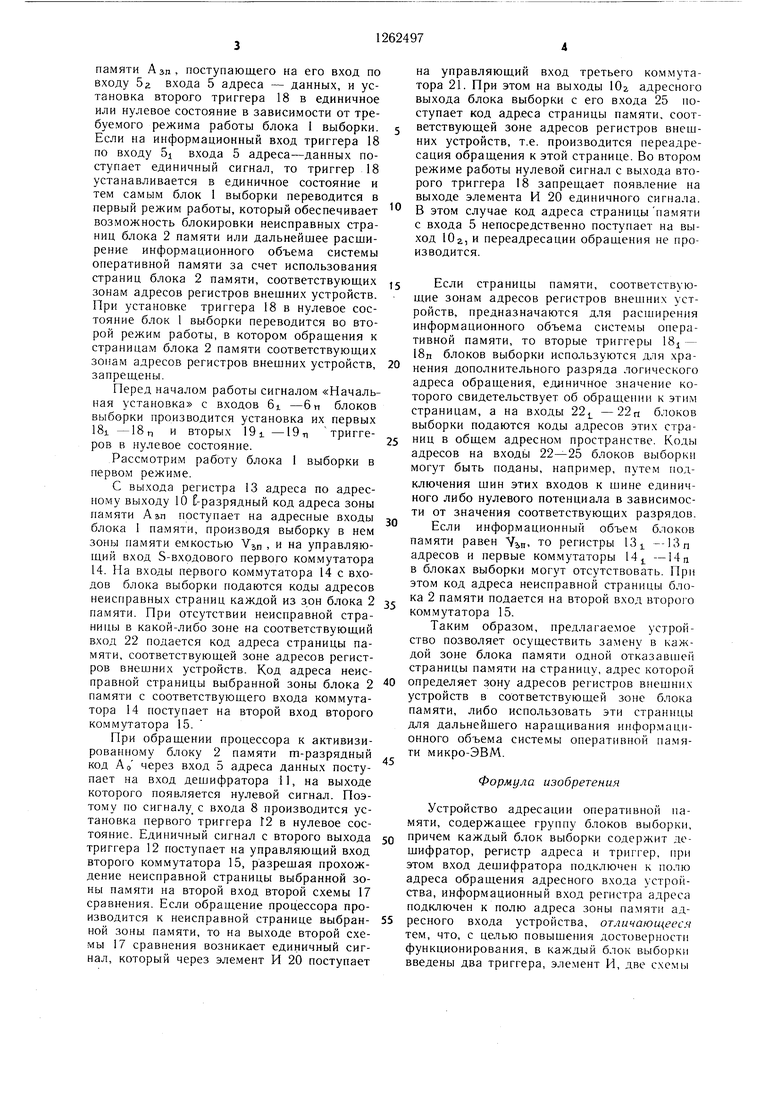

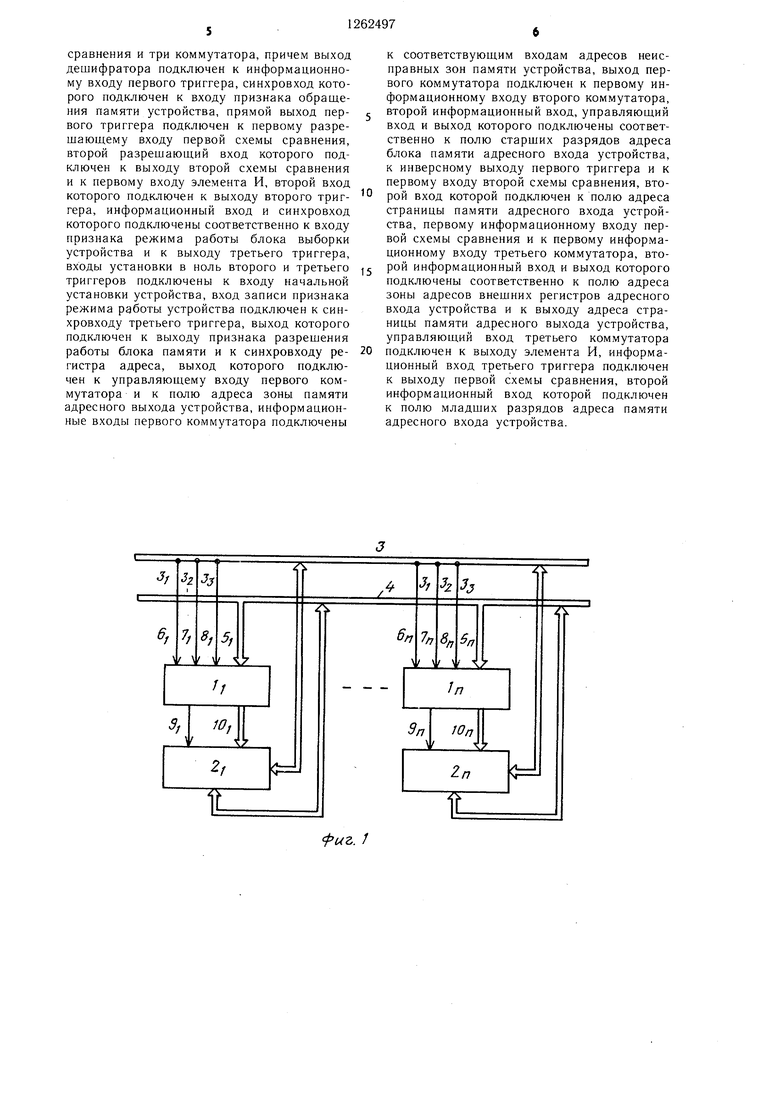

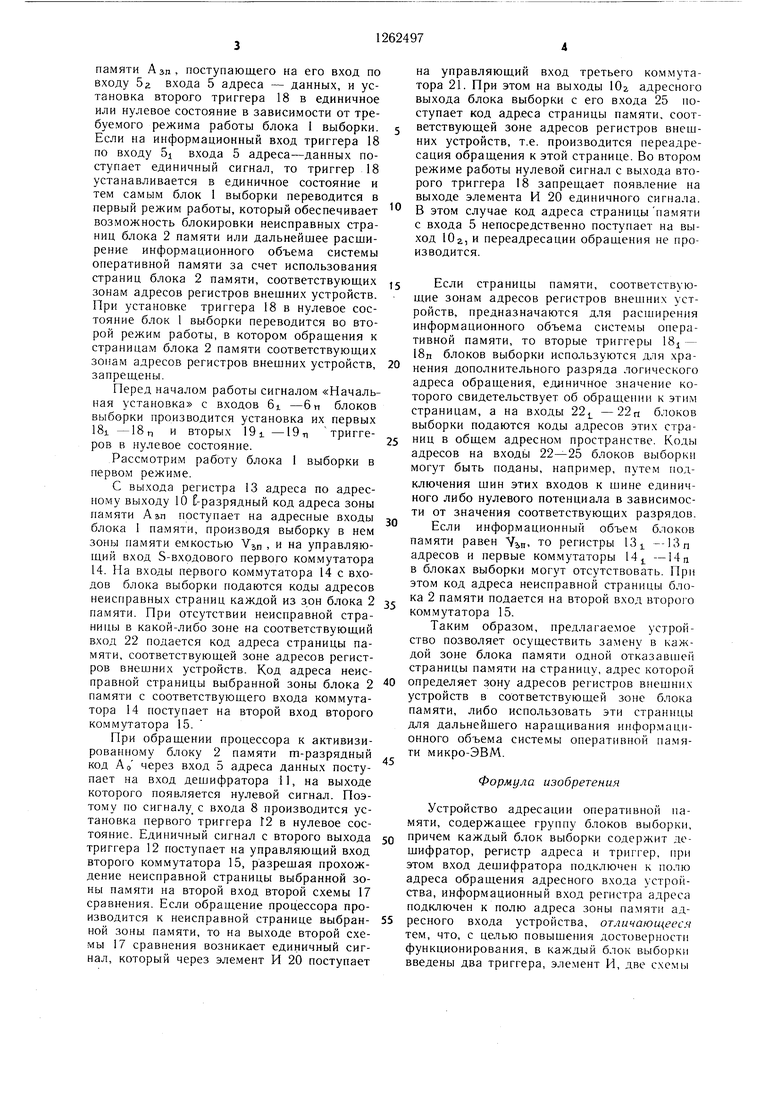

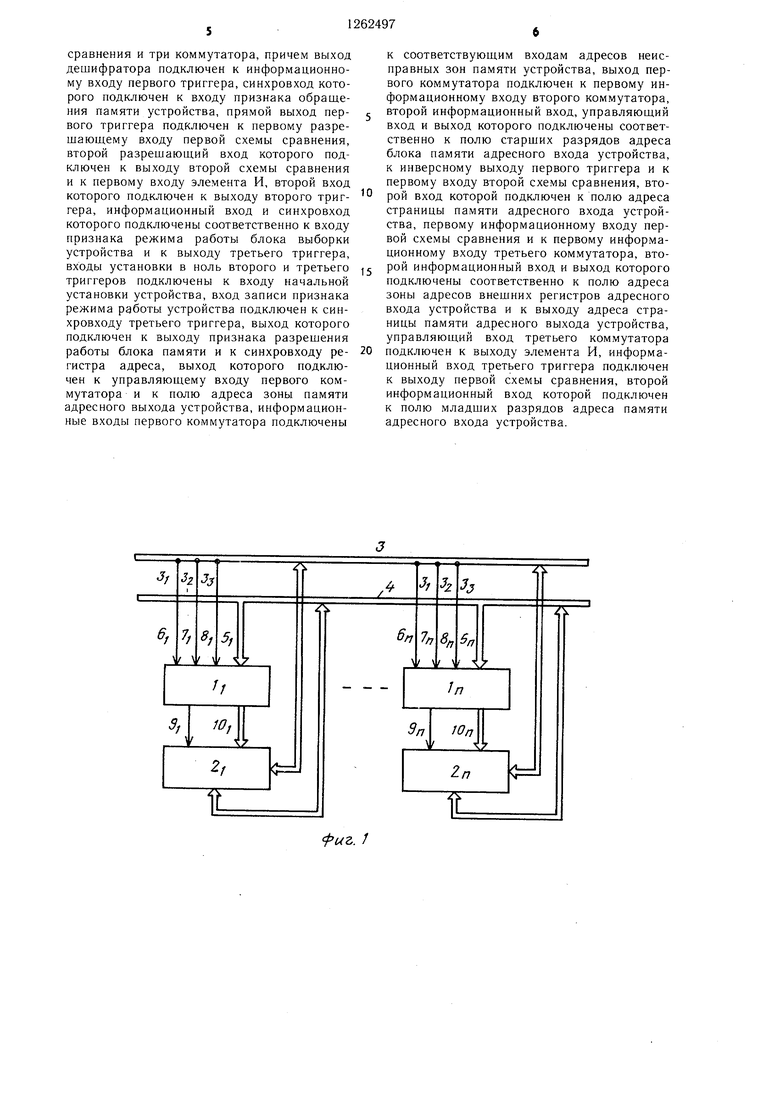

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 - функциональная схема блока выборки; на фиг. 3 - распределение логических адресов.

Устройство содержит группу блоков 1 выборки, адресующих группу блоков 2 памяти, шину 3 управления, шину 4 данных - адреса, все входы блоков выборки подключены к соответствующим функциональным входам устройства, входящим в состав магистралей 3 и 4.

Каждый блок выборки содержит вход 5 адреса - данных, включающий поля 5 признака режима работы блока, 5г адреса зоны памяти, 5э адреса страницы памяти, 5ч младших разрядов адреса блока памяти, вход 6 начальной установки, вход 7 записи признака режима работы блока выборки, вход 8 признака обращения к памяти, подключенные к соответствующим входам устройства, выход 9 признака разрешения работы блока памяти, адресный выход 10, включающий поле 10/ , адреса зоны памяти и поле 10 адреса страницы памяти блока, подключенные к соответствующим входам блока памяти, управляемого данным блоком выборки, дешифратор 11, триггер 12, регистр 13 адреса, коммутаторы 14 и 15, схемы 16 и 17 сравнения, триггеры 18 и 19, элемент И 20, коммутатор 21, поля 22-25 адресного входа устройства.

Распределение логических адресов АЛ по блокам памяти рсуществляется следующим образом (фиг. 3). К старших разрядов АЛ определяют адрес блока памяти АБЛ, следующие I разрядов - адрес зоны памяти АЗП , информационный объем Vjn которой соответствует адресному пространству микро-ЭВМ определяемому ш-разрядным адресом обращения АО микро-ЭВМ; следующие г разрядов - адрес страницы в блоке памяти Agfl, информационный объем з/ - которой соответствует емкости зоны адресов регистров внешних устройств микроЭВМ; т-г младших разрядов - адрес слова АС внутри страницы блока памяти. Страницы памяти, соответствующие зонам адресов регистров внешних устройств, на фиг. 3 заштрихованы (для примера в качестве этих страниц показаны страницы памяти с максимальным значением АС,П , что характерно для микро-ЭВМ типа «Электроника-60).

Устройство работает следующим образом (работа устройства рассматривается на примере одного из блоков выборки, номер которого опущен).

При необходимости обращения процессора по адресу слова, содержащемуся, например, в блоке памяти 2м , с помощью блока выборки IM предварительно производится активизация (т.е. разрешение работы этого блока и выбор внутри него соответствующей зоны емкостью Vjn . Для этого процессор обращается по некоторому адресу АВ из области адресов регистров внещних устройств с записью кодов адресов АБП и АЗЛ . Код адреса А в дещифруется с помо щью дешифраторов Ну -11, и единичные сигналы с их выходов поступают на информационные входы соответствующих первых триггеров 12/ -12/ . Сигналом, поступающим по шине Зз на входы блоков выборки и далее на

5 входы записи соответствующих первых триггеров 12t -12л , производится запись в них единичной информации. Единичные сигналы с первых выходов первых триггеров 12) - 12п поступают на вторые управляющие входы соответствующих первых схем

0 16ч -16 сравнения, разрешая их работу. Нулевые сигналы с вторых выходов этих триггеров поступают на управляющие входы соответствующих вторых коммутаторов 15i -15л , разрешая прохождение г старщих разрядов адресов с входов 23L -23п соответствующих блоков выборки на первые входы их вторых схем 17i - 17п сравнения. Через входы 24.; -24п блоков выборки на входы их первых схем сравнения 16) --16п поступают к - г младQ ших разрядов Agn- При активизации блока 2 памяти из процессора через вход 5. блока 1 выборки на вход его первой схемы 16 сравнения поступает к-г младших, а через вход 5j на вход второй схе.мы 17 сравнения - г старщих разрядов АБП . При

5 этом на выходе второй схемы 17 сравнения возникает единичный сигнал, который поступает на первый управляющий вход первой схемы 16 сравнения и разрешает ее работу. Единичный сигнал с выхода первой схемы 16 сравнения блока 1 выборки и ну0 левые сигналы с выходов первых схем сравнения остальных блоков выборки поступают на информационные входы соответствующих третьих триггеров 9i -19 п . Сигналом, поступающим с щины 3 магистра ли 3 управления через входы 7 -7п блоков выборки на входы записи их третьих триггеров 19. - 19л, производится установка в единичное состояние триггера 19 блока 1 выборки и в нулевое состояние третьих триггеров остальных блоков выборки. Единичный сигнал с первого выхода 19 триггера через управляющий выход 9 блока 1 выборки поступает на вход поступления сигнала «Разрешение работы блока 2 памяти, производя его активизацию, и на вхо5 ды записи второго триггера 18 и регистра 13 адреса. Передним фронтом единичного сигнала с выхода триггера 19 производится запись в регистр 13 адреса кода адреса зоны памяти АЗП, поступающего на его вход по входу 5 г входа 5 адреса - данных, и установка второго триггера 18 в единичное или нулевое состояние в зависимости от требуемого режима работы блока I выборки. Если на информационный вход триггера 18 по входу 5i входа 5 адреса-данных поступает единичный сигнал, то триггер 18 устанавливается в единичное состояние и тем самым блок I выборки переводится в о , первый режим работы, который обеспечивает возможность блокировки неисправных страниц блока 2 памяти или дальнейшее расширение информационного объема системы оперативной памяти за счет использования страниц блока 2 памяти, соответствуюш,их зонам адресов регистров внешних устройств. При установке триггера 18 в нулевое состояние блок 1 выборки переводится во второй режим работы, в котором обращения к страницам блока 2 памяти соответствующих зонам адресов регистров внешних устройств, запрещены. Перед началом работы сигналом «Начальная установка с входов 6i -6п блоков выборки производится установка их первых 18i -18п и вторых 19i -19я триггеров в нулевое состояние. Рассмотрим работу блока 1 выборки в первом режиме. С выхода регистра 13 адреса по адресному выходу 10 С-разрядный код адреса зоны памяти AM поступает на адресные входы блока 1 памяти, производя выборку в нем зоны памяти емкостью Vj,n , и на управляющий вход S-входового первого коммутатора 14. На входы первого коммутатора 14 с входов блока выборки подаются коды адресов неисправных страниц каждой из зон блока 2 памяти. При отсутствии неисправной страницы в какой-либо зоне на соответствующий вход 22 подается код адреса страницы памяти, соответствующей зоне адресов регистров внешних устройств. Код адреса неисправной страницы выбранной зоны блока 2 памяти с соответствующего входа коммутатора 14 поступает на второй вход второго коммутатора 15. При обращении процессора к активизированному блоку 2 памяти т-разрядный код АО через вход 5 адреса данных поступает на вход дешифратора 11, на выходе которого появляется нулевой сигнал. Поэтому по сигналу с входа 8 производится установка первого триггера 12 в нулевое состояние. Единичный сигнал с второго выхода триггера 12 поступает на управляющий вход второго коммутатора 15, разрешая прохождение неисправной страницы выбранной зоны памяти на второй вход второй схемы 17 сравнения. Если обращение процессора производится к неисправной странице выбранной зоны памяти, то на выходе второй схемы 17 сравнения возникает единичный сигнал, который через элемент И 20 поступает на управляющий вход третьего коммутатора 21. При этом на выходы Юг адресного выхода блока выборки с его входа 25 поступает код адреса страницы памяти, соответствующей зоне адресов регистров внешних устройств, т.е. производится переадресация обращения к этой странице. Во втором режиме работы нулевой сигнал с выхода второго триггера 18 запрещает появление на выходе элемента И 20 единичного сигнала. В этом случае код адреса страницы памяти с входа 5 непосредственно поступает на выход Юг, и переадресации обращения не производится. Если страницы памяти, соответствующие зонам адресов регистров внешних устройств, предназначаются для расширения информационного объема системы оперативной памяти, то вторые триггеры 18 - 18п блоков выборки используются для хранения дополнительного разряда логического адреса обращения, единичное значение которого свидетельствует об обращении к этим страницам, а на входы 22 -22п блоков выборки подаются коды адресов этих страниц в общем адресном пространстве. Коды адресов на входь 22-25 блоков выборки могут быть поданы, например, путем подключения щин этих входов к шине единичного либо нулевого потенциала в зависимости от значения соответствующих разрядов. Если информационный объем блоков памяти равен Уьп ID регистры 13, --13п адресов и первые ком.мутаторы 14 -14п в блоках выборки могут отсутствовать. При этом код адреса неисправной страницы блока 2 памяти подается на второй вход второго коммутатора 15. Таким образом, предлагаемое устройство позволяет осуществить замену в каждой зоне блока памяти одной отказавшей страницы памяти на страницу, адрес которой определяет зону адресов регистров внешних устройств в соответствующей зоне блока памяти, либо использовать эти страницы для дальнейшего наращивания информационного объема системы оперативной памяти микро-ЭВМ. Формула изобретения Устройство адресации оперативной памяти, содержащее группу блоков выборки, причем каждый блок выборки содержит дешифратор, регистр адреса и триггер, при этом вход дешифратора подключен к полю адреса обращения адресного входа устройства, информационный вход регистра адреса подключен к полю адреса зоны памяти адресного входа устройства, отличающееся тем, что, с целью повышения достоверности функционирования, в каждый блок выборки введены два триггера, элемент И, две схемы сравнения и три коммутатора, причем выход дешифратора нодключен к информационному входу первого триггера, синхровход которого подключен к входу признака обращения памяти устройства, прямой выход первого триггера подключен к первому разрешающему входу первой схемы сравнения, второй разрешающий вход которого подключен к выходу второй схемы сравнения и к первому входу элемента И, второй вход которого подключен к выходу второго триггера, информационный вход и синхровход которого подключены соответственно к входу признака режима работы блока выборки устройства и к выходу третьего триггера, входы установки в ноль второго и третьего триггеров подключены к входу начальной установки устройства, вход записи признака режима работы устройства подключен к синхровходу третьего триггера, выход которого подключен к выходу признака разрешения работы блока памяти и к синхровходу регистра адреса, выход которого подключен к управляющему входу первого коммутатора и к полю адреса зоны памяти адресного выхода устройства, информационные входы первого коммутатора подключены к соответствующим входам адресов неисправных зон памяти устройства, выход первого коммутатора подключен к первому информационному входу второго коммутатора, второй информационный вход, управляющий вход и выход которого подключены соответственно к полю старших разрядов адреса блока памяти адресного входа устройства, к инверсному выходу первого триггера и к первому входу второй схемы сравнения, второй вход которой подключен к полю адреса страницы памяти адресного входа устройства, первому информационному входу первой схемы сравнения и к первому информационному входу третьего коммутатора, второй информационный вход и выход которого подключены соответственно к полю адреса зоны адресов внешних регистров адресного входа устройства и к выходу адреса страницы памяти адресного выхода устройства, управляющий вход третьего коммутатора подключен к выходу элемента И, информационный вход третьего триггера подключен к выходу первой схемы сравнения, второй информационный вход которой подключен к полю младщих разрядов адреса памяти адресного входа устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство адресации оперативной памяти | 1987 |

|

SU1417003A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1305691A2 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении высоконадежных систем оперативной памяти микро-ЭВМ большой информационной емкости. Целью изобретения является повышение достоверности функционирования. Устройство содержит группу блоков выборки, каждый из которых содержит дешифратор, три триггера, три коммутатора, две схемы сравнения и элемент И. Поставленная цель достигается за счет автоматического замещения неисправных страниц памяти резервными страницами. 3 ил.

(риг. /

Логический адрес опрощения /1л

На лок Z лaмfff77cf

pui. 2

Aof/n)

бтк /7affff/7 U /7

| Устройство для формирования адреса данных | 1982 |

|

SU1068939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство адресации оперативной памяти | 1981 |

|

SU999054A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-15—Подача