4

VI

1

Изобретение относится к вычислительной технике и может быть использовано- для построения оперативной памяти микроэвм большой информационной емкости.

I Целью изобретения является расши- реИие функциональных возможностей устройства за счет возможности активизации произвольного набора физических страниц памяти адресного пространства блоков памяти и произволь- но:го распределения их в адресном иро- ст ранстве микроЭВМ.

Таким образом, соответствие между логическими адресами страниц памяти адресного пространства микроЭВМ и физическими адресами страниц памяти адресного пространства блоков памяти может быть произвольным и измениться при необходимости в процессе работы устройства.

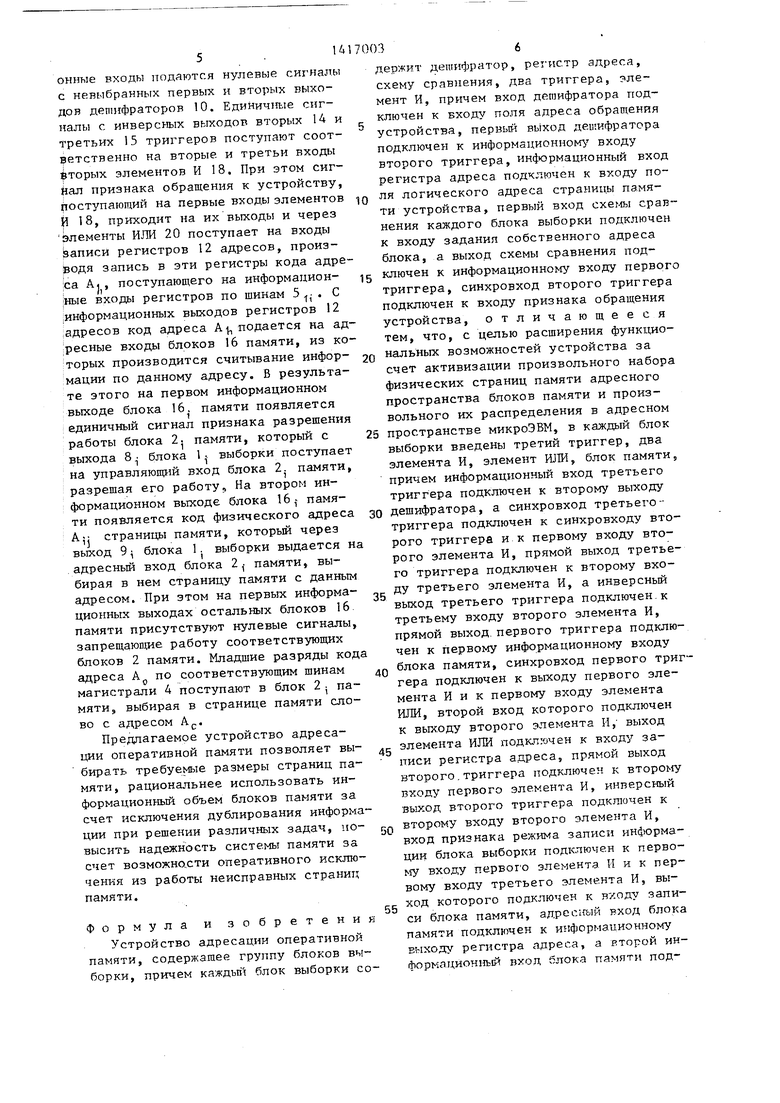

На фиг. 1 приведен пример распределения страниц памяти п блоков па1417003

блок

памяти, первый

ID- 11CI ш ;а I ri J

19; элементы Н, элемент 2

7, третий

ИЛИ 20. , вход

задания собственного адреса ад- ресуемого блока памяти, на котором задан код адреса А блока 2; памяти, например, путем подключения шин этого входа к шине единичного либо нулевого потенциала в зависимости от зна- 10 чения соответствующих разрядов.

Работу устройства последовательно рассмотрим в режиме активизации страниц памяти адресного поля блоков памяти и в режиме обращения процессора 15 микроэвм к активизированным страницам памяти.

При активизации j-й страницы памяти 1-го блока памяти, имеющей физи20

J

на месте страницы

имеющей логический адрес At

ческий адрес А памяти,

в адресном пространстве микроЭВМ, процессор производит два последовательных обращения с записью инфоргзтзм , мации. При первом обращении процессор мяти в адресном пространстве микроЭВМ з „ магистрали 4 где каждый блок памяти имеет 1 физимагистрали 4 адреса - данных через входы 5 адреса - данных во все блоки выборки передает следующую информацию: по шинам адреса устройства - не- которьш адрес Ag из области адресов регистров внешних устройств микроЭВМ, по шинам данных адрес выбранного- i-ro- блока памяти логический адрес страницы памяти А,, на.месте которой в адресном пространстве мик- 35 роЭВМ располагается выбранная страница i-ro блока памяти. При поступлении этой информации дешифраторы 10 всех блоков выборки производят

ческих страниц памяти, а адресное пространство микроэвм Ьключает г логических страниц памяти {стрелками уловно показано соответствие между этими страницами памяти); на фиг,2 - пример использования устройства для построения системы оперативной памяти; на фиг. 3 - функциональная схема блока выборки.

Система оперативной памяти (фиг.2 содержит группу блоков выборки 1,адресующих группу блоков памят магистраль. 3 управления.

-1 п магистраль

адреса - данных. Все входы блоков вы борки подключены к соответствующим функциональным входам устройства, входящим в состав магистралей 3 и 4 выходы - к соответствующим управляющему и адресному входам адресуемого (5лока памяти,

Каждый блок 1

выборки имеет вход включаюшда поля

.); адреса - данных, логического адреса страницы памяти .5. , адреса блока памяти 52, физического адреса страницы памяти 53i , вход 6; признака режима записи информации, вход 7- признака обращения к устройству, выход 8 признака разрешения работы адресуемого блока памя- ти, выход 9; физического адреса страницы памяти, дешифратор 10;, схему 11; сравнения, регистр 12- адреса, первый 13; - третий 15 i триггеры.

блок

памяти, первый

ID- 11CI ш ;а I ri J

19; элементы Н, элемент 2

7, третий

ИЛИ 20. , вход

задания собственного адреса ад- ресуемого блока памяти, на котором задан код адреса А блока 2; памяти, например, путем подключения шин этого входа к шине единичного либо нулевого потенциала в зависимости от зна- чения соответствующих разрядов.

Работу устройства последовательно рассмотрим в режиме активизации страниц памяти адресного поля блоков памяти и в режиме обращения процессора микроэвм к активизированным страницам памяти.

При активизации j-й страницы памяти 1-го блока памяти, имеющей физи

J

на месте страницы

имеющей логический адрес At

ческий адрес А памяти,

в адресном пространстве микроЭВМ, процессор производит два последовательных обращения с записью информации. При первом обращении процессор „ магистрали 4

магистрали 4 адреса - данных через входы 5 адреса - данных во все блоки выборки передает следующую информацию: по шинам адреса устройства - не- которьш адрес Ag из области адресов регистров внешних устройств микроЭВМ, по шинам данных адрес выбранного- i-ro- блока памяти логический адрес страницы памяти А,, на.месте которой в адресном пространстве мик- роЭВМ располагается выбранная страница i-ro блока памяти. При поступлении этой информации дешифраторы 10 всех блоков выборки производят

опознание адреса А

11

сравнения адреса

0 пает на их входы 5

блока

61 с входов

1,

знание адреса , который 5-7; входов адреса - данных

0

5

который посту- 5, а схема выборки - опо- по шинам подается

на вторые входы всех схем 11 сравнения. На первые входы всех схем 11 сравнения подаются коды адресов соответствующих блоков памяти. Единичные сигналы с первых выходов дешифраторов 10 поступают на информационные входы вторых триггеров 14, а единичный сигнал сравнения с выхода схе-. мы 11 сравнения и нулевые сигналы несравнения с выходов остальных схем 11 - на информационные входы соответствующих первых триггеров 13. По сигналу признака обращения к устройству, поступающему с соответствующей шины магистрали 3 управления через входы 7 блоков выборки на синхровходм вто3

рых lA и третьих 15 триггеров,-производится их установка соответственно в единичное и нулевое состояния (на информацион1а1е входы третьих триггеров 15 поступают нулевые сигналы с невыбранных вторых выходов дешифраторов 10). На входы 6 блоков выборки с соответствующей шины магистрали 3 управления поступает сигнал признака режима записи информации, по которому в устройстве производятся следующие действия. Проходя через первые элементы И 17 на синхровходы первых триггеров 13, сигнал производит установку в единичное состояние первый триггер 13 блока 1 выборки и в нулевое состояние первые триггеры 13 остальных блоков выборки. Единичный

170034

нака записи информя ши с входоп 6 поступает на первые входы третьих элементов И 19 и далее с их выходов на вхолы записи блоков 16 памяти. Этим сигналом во все блоки 16 памяти по адресу Л, , подаваемому на их адресные входы с информапионных выходов регистров 12 адресов, производится запись

кода адреса Л-- , поступающего на их вторые информационные входы по шинам 5j, а также запись признака разрешения работы блока памяти, поступающего на их первые информационные входы.

При этом в блоке 16j памяти блока 1- выборки разряд этого признака устанавливается в единичное состояние, а в остальных блоках 16 памяти - в нулевое состояние. Единичное состояние

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации оперативной памяти | 1985 |

|

SU1262497A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Запоминающее устройство | 1986 |

|

SU1361623A1 |

| Устройство для сопряжения процессора с памятью | 1988 |

|

SU1683020A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство управления памятью | 1987 |

|

SU1411761A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство для ввода информации | 1990 |

|

SU1748156A1 |

Изобретение относится к области вычислительной техники и может использовано для построения систем оперативной памяти микроЭВМ большой информационной емкости. Целью изобретения является расширение функциональных возможностей устройства за счет возможности активизации произвольного набора физических страниц памяти адресного пространства блоков памяти и произвольного распределения их в адресном пространстве микроэвм. Устройство адресаци оперативной памяти позволяет выбирать требуемые размеры страниц памяти, рациональнее использовать информационный объем блоков памяти за счет исключения дублирования информации при решении различных задач, повысить надежность системы памяти за счет возможного оперативного исключения из работы неисправных страниц памяти. 3 ил. сл

сигнал с прямого выхода первого триг-2о разряда признака по адресу А. блока гера 13. блока Ij выборки подается на первьй информационный вход блока 16

памяти. При этом на первые информационные входы остальных блоков 16 памяти подаются нулевые сигналы с прямых выходов соответствующих первых триггеров 13. Проходя с выходов первых элементов И 7 через элементы ИЛИ 20 на входы записи регистров 12 адресов, сигнал производит запись в них кода адреса А, поступающего на их информационные входы с шин 5, входов 5. С информационных выходов регистров 12 адреса код Af, подается на адресные входы блоков 16 памяти.

При втором обращении процессор по магистрали 4 через входы 5 во все блоки выборки передает следующую информацию: по шинам адреса - некото- рьм адрес Ag из области адресов регистров внешних устройств микроЭВМ; по шинам даиньгх - физический адрес AJ- активизируемой страницы памяти, поступающий по шинам 5 на вторые информационные входы блоков 16 памяти. Дешифраторы 10 всех блоков выборки производят опознание адреса А щ, и единичные сигналы с их вторых выходов подаются на информационные входы тре16, памяти означает, что на месте страницы памяти с адресом А f, в адре ном пространстве микроЭВМ размещается страница памяти блока 2,- памяти, 25 имеющая физический адрес А--.. Дпя

других блоков 2 памяти данная страни ца адресного пространства микроЭВМ является занятой, о чем и свидетельствует нулевое значение разряда при30

знака по адресу А в остальных блока 16 памяти. На этом активизация стран цы памяти блока 2 памяти, имеющей

физический адрес А

I)

в адресном про35

странстве блоков памяти и логический адрес Ajj в адресном пространстве мик

роэвм, заканчивается. Аналогично про изводится активизация и размещение в адресном пространстве микроЭВМ и дру гих страниц памяти блоков 2 памяти.

40 Работу устройства в режиме обраще ния поцессора к активизированным стр ницам памяти блоков 2 памяти рассмот рим на примере обращения к рассмотренной странице памяти с логическим

45 адресом А| в адресном пространстве микроэвм и физическим адресом AJ: в адресном пространстве блоков памяти. При обращении процессора к этой стра нице памяти во все блоки выборки потьих триггеров 15. По сигналу призна- 50 ступает логический адрес обращения ка обращения к устройству, поступаю- А, старшие разряды которого опреде- щему на входы 7 блоков выборки и с ляют адрес страницы памяти А:|, в ад- них на синхровходы вторых 1Д и тре ресном пространстве микроЭВМ, мпад- твих 15 триггеров, производится их шие - адрес слова А, внутри этой установка соответственно в нулевое и eд raичнoe состояния. При этом единичный сигнал с выходов третьих триггеров 15 проходит на вторые входа третьих элементов И 19. Сигнал приз

55 страницы. При поступлении из процессора сигнала признака обращения к устройству вторые 1Д и третьи 15 триггеры устанавливаются в нулевое состояние, так как на их информациразряда признака по адресу А. блока

16, памяти означает, что на месте страницы памяти с адресом А f, в адресном пространстве микроЭВМ размещается страница памяти блока 2,- памяти, имеющая физический адрес А--.. Дпя

других блоков 2 памяти данная страница адресного пространства микроЭВМ является занятой, о чем и свидетельствует нулевое значение разряда при30

знака по адресу А в остальных блоках 16 памяти. На этом активизация страницы памяти блока 2 памяти, имеющей

физический адрес А

I)

в адресном про5

странстве блоков памяти и логический адрес Ajj в адресном пространстве микроэвм, заканчивается. Аналогично производится активизация и размещение в адресном пространстве микроЭВМ и других страниц памяти блоков 2 памяти.

0 Работу устройства в режиме обращения поцессора к активизированным страницам памяти блоков 2 памяти рассмотрим на примере обращения к рассмотренной странице памяти с логическим

5 адресом А| в адресном пространстве микроэвм и физическим адресом AJ: в адресном пространстве блоков памяти. При обращении процессора к этой странице памяти во все блоки выборки поступает логический адрес обращения А, старшие разряды которого опреде- ляют адрес страницы памяти А:|, в ад- ресном пространстве микроЭВМ, мпад- шие - адрес слова А, внутри этой

страницы. При поступлении из процессора сигнала признака обращения к устройству вторые 1Д и третьи 15 триггеры устанавливаются в нулевое состояние, так как на их информационные входы подаются нулевые сигналы с невыбранных первых и вторых выходов дешифраторов 10. Единичные сигналы с инверсных выходов вторых 14 и третьих 15 триггеров поступают соответственно на вторые, и третьи входы фторых элементов И 18. При этом сиг- ал признака обращения к устройству, поступающий на первые входы элементов И 18, приходит на их выходы и через элементы ИЛИ 20 поступает на входы Ьаписи регистров 12 адресов, производя запись в эти регистры кода адре- :са А , поступающего на икформацион- |ные входы регистров по шинам 5 . С информационных выходов регистров 12 ;адресов код адреса А ц подается на ад- |ресные входы блоков 16 памяти, из ко

вторых производится считывание информации по данному адресу. В результате этого на первом информационном выходе блока 16, памяти появляется единичный сигнал признака разрешения работы блока 2. памяти, который с выхода 8 блока выборки поступает на управляющий вход блока 2. памяти, разрещая его работу. На втором информационном выходе блока 16| памяти появляется код физического адреса Aj; страницы памяти, которьй через выход 9 блока 1. выборки выдается н адресньш вход блока 2. памяти, выбирая в нем страницу памяти с данньм адресом. При этом на первых информационных выходах остальных блоков 16 памяти присутствуют нулевые сигналы, запрещающие работу соответствующих блоков 2 памяти. Младшие разряды код адреса А по соответствующим щинам магистрали 4 поступают в блок 2 памяти,, выбирая в странице памяти слово с адресом А,.

Предпагаемое устройство адресации оперативной памяти позволяет выбирать требуемые размеры страниц памяти, рациональнее использовать ин- формационньпЧ объем блоков памяти за счет исключения дублирования информации при решении различных задач, повысить надежность системы памяти за счет возможнасти оперативного исключения из работы неисправных страниц памяти.

Формула и зобретения

Устройство адресации оперативной памяти, содержащее группу блоков борки, причем каждъп1 блок выборки со5

0

держит дешифратор, рет истр адреса, схему сравнения, два триггера, элемент И, причем вход дешифратора подключен к входу поля адреса обращения устройства, первый выход деишфратора подключен к информационном входу второго триггера, инфюрмационный вход регистра адреса подключен к входу поля логического адреса страницы памяти устройства, первый вход схемы сравнения каждого блока выборки подключен к входу задания собственного адреса блока, а выход схемы сравнения подключен к информационному входу первого триггера, синхровход второго триггера подключен к входу признака обращения устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет активизации произвольного набора физических страниц памяти адресного пространства блоков памяти и произвольного их распределения в адресном

5 пространстве микроЭВМ, в каждый блок выборки введены третий триггер, два элемента И, элемент ШШ, блок памяти, причем информационный вход третьего триггера подключен к второму выходу

0 дешифратора, а синхровход третьего- триггера подключен к синхровходу второго триггера и к первому входу второго элемента И, прямой выход третьего триггера подключен к второму входу третьего элемента И, а инверсньй выход третьего триггера подключен.к третьему входу второго элемента И, прямой выход, первого триггера подключен к первому информационному входу блока памяти, синхровход первого триггера подключен к выходу первого элемента Ник первому входу элемента ИЛИ, второй вход которого подключен к вьпсоду второго элемента И, выход элемента ИЛИ подключен к входу записи регистра адреса, прямой выход второго, триггера подключен к второьгу входу первого элемента И, инверсный выход второго триггера подключен к второму входу второго элемента И, вход признака режима записи информации блока выборки подклюгтен к перво- iy входу первот о элемента И и к первому входу третьего элемента И, выход которого подключен к входу записи блока памяти, адрес1Шй вход блока памяти подключен к информаиионному выходу регистра адреса, а второй информационный вход блока памяти под5

0

5

0

5

ключей к входу поля физического адреса страницы памяти устройства, первый и второй информационные выходы блока памяти являются выходами признака

Адресное пространстдо микроэвм

Страница . памяти /

pOHt/i

Страница « : памяти 6

Страница , памяти п

Страница « памяти r-Z

Страница . памяти г 1

Страница памяти г

Фиг.1

разрешения работы адресуемого блока памяти и выходом физического адреса страницы памяти блока ныборки соот ветствснпо.

Адресное пространство блокоб памяти

траница .. памяти п

Страница .„ naMffmuiZ

9

Страница .. памяти it

Страница , памяти 1

Хтранища памяти22

Страница «. памяти

Страница . памрти и

Страница памяти LL

. . LJ

,5лок памяти I

Страница . памяти и

Страница . памяти П1

Страница

памятип2

блок памйти п

Страница , naMffmu п i

| Титов Ю.Н., Шахнов.В.А | |||

| Шпигель- ский В.Н | |||

| Модуль полупроводникового ОЗУ для микроэвм.-В кн.: Микроэлектроника и полупроводниковые приборы/Под ред | |||

| А.А.Васенкова и Я.А.Федотова, 1979, вып | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

| Шевкопляс Б.В | |||

| Микропроцессорные структуры | |||

| Инженерные решения | |||

| М,: Радио и связь, 1986, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство адресации оперативной памяти | 1985 |

|

SU1262497A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1987-01-12—Подача