Изобретение относится к вычиспнтепь ой технике и может быть использовано ри функциональном циагностировпнии ппаратуры.

Известно устройство цпя контропя5

поиска неисправностей комбинационных схем, содержащее источник питания, бпок фиксации неисправностей, коммутатор переменных погических функций, коммутатор переменных инверсных погическихО ункций. Эти коммутаторы выполнены матричными с двумя группами выхоцных шин. Шины одной группы явпяются общими цпя обоих коммутаторов и соединяются с соответствующими входными 15 шинами в одном из включенных попоже- . НИИ коммутирующих эпементов через электронные ключи. Управляющие входы электронных ключей через схемы ИЛИ подключены к входам шагового коммута- 20 тсра н к выходным шинам другой группы дшпюго коммутатора, соединяющихся с входными шинами в другом включенном опожении тех же коммутирующих эпе- ментов, которые соединены с управ- 25 пяющими входами диагностируемой . Нагрузкой диагностируемой схемы является блок фиксации неисправностей. Входы блока фиксации неисправностей через коммутируюите элементы коммута- зо тора конъюнкций подключены к одноименным входам шагового коммутатора В каждом положении шагового коммутатора источник питания подключен одновременно к одной из входных шин одного комму-,татора совместно со всеми входными шинами и входами всех схем ИЛИ другого коммутаюра Ш .

Недостатком указанного устройства является невозможность примене1тая его 4Q для контроля дискретного устройства в процессе выполнения рабочей программы.

Наиболее близким к предлагаемому является устройство контроля логических счем,содержащее блок управления,.блок вво- 5 да данных,подключенный к регистрам,управляющие входы которых подкпючены к выходу блока управления,блок выделения неисправностей,элемент ИЛИ и блок индикации l2j.

Однако в данном устройстве контроль 50 аппаратуры производится только во время ее остановки, т, е, в промежутки между выполнениями рабочей программы что не позволяет выявить неисправности, возни-. кающие в процессе выполнения рабочей 55 программы.

Цель 13обретения - повышение эффективности контроая, т. е. обнаружение

неисправностей в реальном масштабе времени, на основании вычисленных проверяющих тестов для комбинационных логических схем.

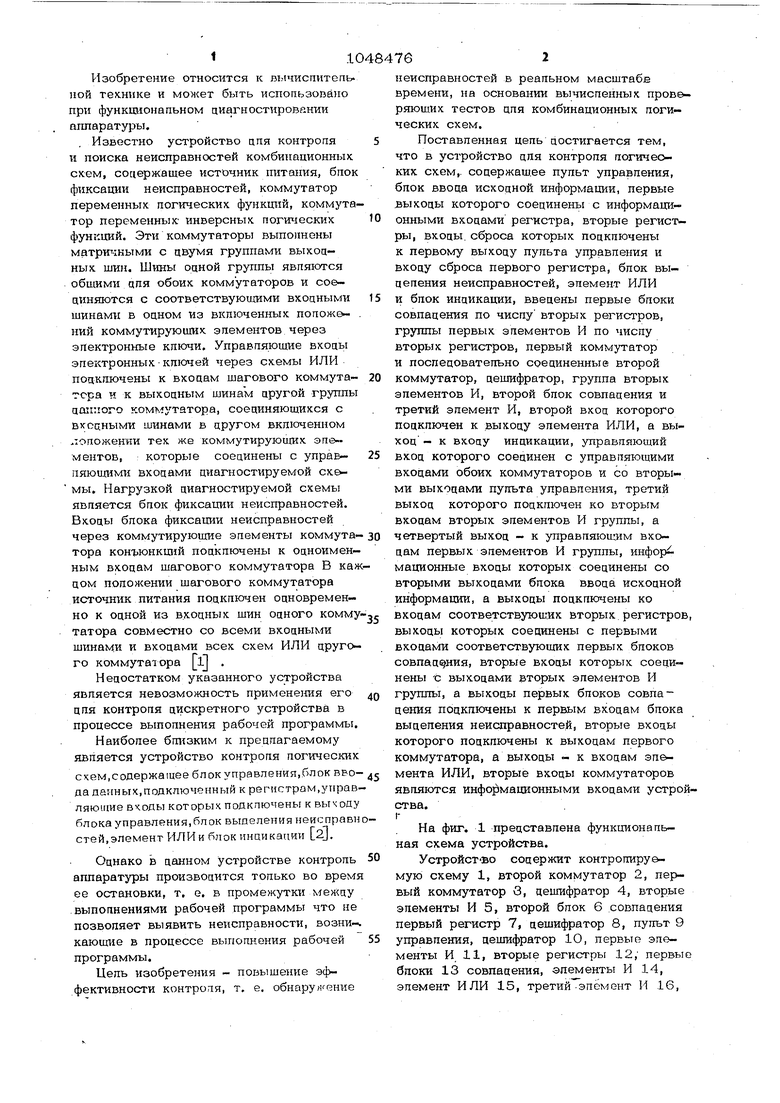

Поставленная цель достигается тем, что в устройство для контроля логических схем,, содержащее пульт управления, блок ввода исходной информации, первые выходы которого соединены с информационными входами регистра, вторые регистры, входы, сброса которых подключены к первому выходу пульта управления и входу сброса первого регистра, блок выделения неисправностей, элемент ИЛИ и блок индикации, введены первые блоки совпадения по числу вторых регистров, группы первых элементов И по числу вторых регистров, первый коммутатор и последовательно соединенные второй коммутатор, дешифратор, группа вторых эпементов И, второй блок совпадения и третий элемент И, второй вход которого подключен к выходу элемента ИЛИ, а выход - к входу индикации, управляющий вход которого соединен с управляющими входами обоих коммутаторов и со вторыми выходами пульта управления, третий выход которого подключен ко вторым входам вторых элементов И группы, а четвертый выход - к управляющим входам первых элементов И группы, инфор мационные входы которых соединены со вторыми выходами блока ввода исходной информации, а выходы подключены ко входам соответствующих вторых регистро выходы которых соединены с первыми входами соответствующих первых блоков совпадения, вторые входы которых соединены -с выходами вторых элементов И группы, а выходы первых блоков совпадения подключены к первым входам блока выделения неисправностей, вторые входы которого подключены к выходам первого коммутатора, а выходы - к входам элемента ИЛИ, вторые входы коммутаторов являются инфо; мационными входами устроства, |На фиг. 1 представлена функциональная схема устройства,

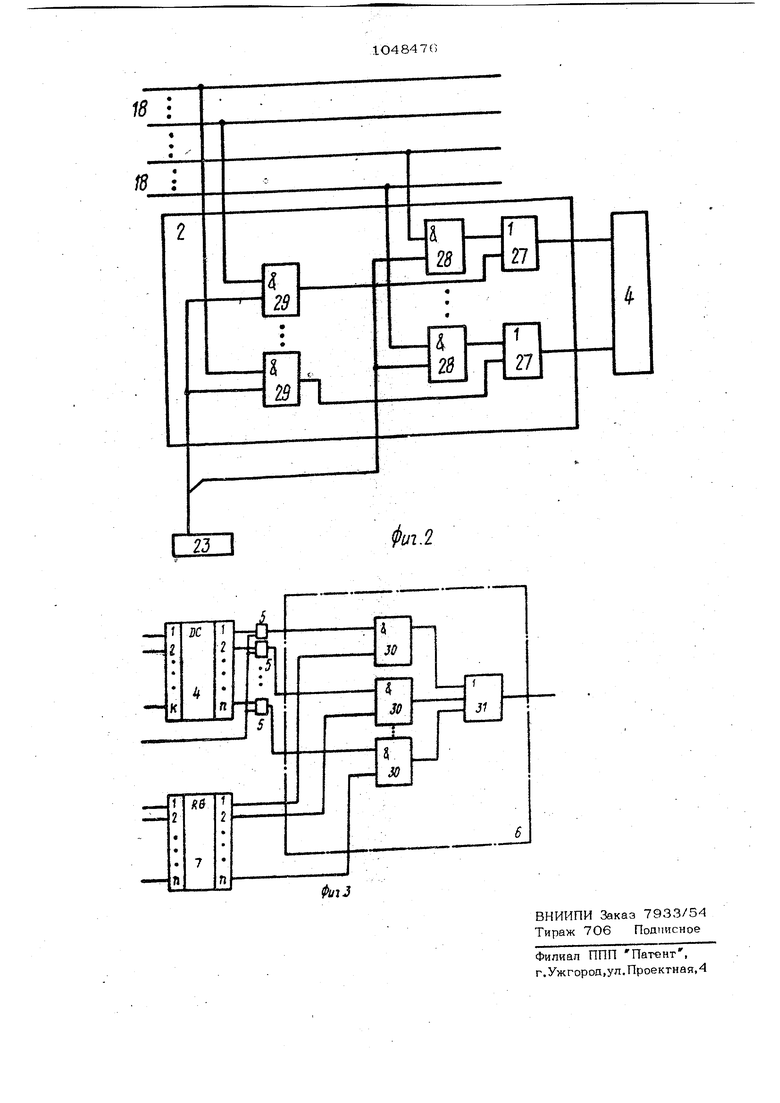

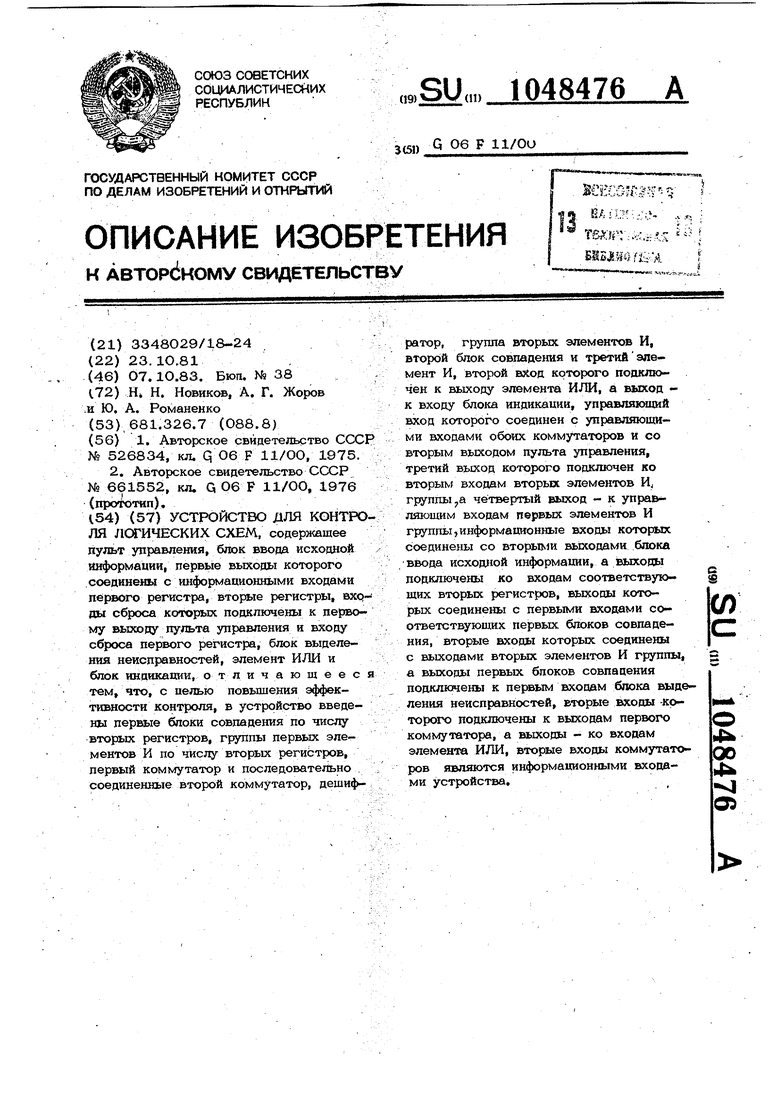

УстройсТБо содержит контролиру&мую схему 1, второй коммутатор 2, первый коммутатор в, дешифратор 4, вторые элементы И 5, второй блок 6 совпадения первый регистр 7, дешифратор 8, пульт 9 управления, дешифратор 10, первые элементы И 11, вторые регистры 12; первы блоки 13 совпадения, элементы И 14, элемент ИЛИ 15, третий элемент И 16, бпок 17 индикации, входные шнны 18, . выгсоцные шины 19, узеп 2О ввода исхоц ных данных, узеп 21 пуска, узеП 22 сбр са, узеп 23 выбора коитропируемой схемы, узеп 24 выбора контрогаируемой точки, бпок 25 ввода исходной информации, бпок 26 выдепения неисправностей, На фиг. 2 представпжна функционапьная схема комнутатора 2, который содержит эпементы ИЛИ 27, первую труппу, элементов И 28 и вторую группу элементов И 29. На фиг. 3 представпена функциональная схема бпоков совпадения, содержащих руппу элементов И 30 и элемент ИЛИ 31, Устройство работает спецующим обра ЗОМ... Для контроля комбинационной схемы прецварителъно- вычисляется одним из методов (табличным или аналит еским), проверяющий тест. С помощью узла ввода исходных данных 20 через дешифратор 8 в первый регистр 7 последовательно записываются единицы , которые. соответствуют весам состояний входных тестовых воздействий. Так, если проверяющий тест содержит входные наборы с весовым состоянием Ч 467, то в 4,6 и 7-е разряды первого регистра 7 последовательно за- писываются единицы, что содействует выбранному тесту. С помощью узла 23 выбора контролируемой схемы происходит через коммутатор 2 и 3 подключение проверяемой сх©мы 1 к устройству контроля. Выходные сигналы с первого регистра 7 поступают в блок 6, подготавливая его к работе. Бпок 6 предназначен для выцепения множества входных наборов, таких наборов, которые входят в выбранный проверяюш:ий тест. При этом блок 6 выдает сигнал, который поступает на элемент И 16, обеспечивающий выдачу сигнала неисправности в блок индика- , ции 17, только при наличии сигнала с. блока 6. С помощью узла 24 выбора контролируемой точки элементов И 11 выбирается один из вторых регистров 12, соответствующий определенной контротгь- ной выходной точке контролируемой сх&мы .1.В выбранный второй регистр 12 с по мощью узпа 20 ввода исходных данных, используя дешифратор 10, записываются единицы в те разряды выбранного регист ра 12, соответствукш.ше входным тестовы наборам, на которых выходная функция принимает единичное значение. Так, если при вводе Tfip 4-6-7 выходная функция при вводе тестовых наборов р весовым состоянием 4 и 7 принимает единичное значение, то в 4 и 7 разряды этого рогистра 12 записываются единицы, а в остальные разряды нули. Для остальных контролъ1Пз1х точек в регистры 12 вводится эталонное значение выходной функции на 4,6 и 7 наборах.. Для пуска устройства необходимо с помощью узпа 21 пуска подать команцу на группу элементов И 5, подготавливая их к открытию. При реализации рабочей программы, поступающей по входным шинам 18 выбранной схемы 1, с помощью узла 23 подаются рабочие воздействия, среди которых есть и входные наборы, которые входят в проверяющий тест. Рабочие воздействия одновременно поступают на вход контролируемой схомы 1 и на вход, дешифратора 2. Выходной сигнал с дешифратора 4 через rpjTiпу элементов И 5 поступает на.вход блока 6 и на блоки 13. В случае, если вес состоетшя входного набора входит в проверяющий тест, записанный в первом регистре 7, то с блока 6 поступает cvirnan на элемент И 16, В то же время выходной сигнал с деши уратора 4 через группу элементов И 5, поступает на блоки 13, где для каждой контролируемой точки записаны эталонные выходные значения выходной функции, :соответствующие входным наборам пров&ряющего теста..С выхода 13 снимается эталонное значение выходного сигнала контрольной точки блока 4, соответствующего входному набору. Выходные сигналы с блоков 13 поступают на элемен ты 14, где сравниваются с выходньага сигналами, поступающими с контроггару мой схемы 1 через коммутатор 3. Если значение выходного сигнала контрол фуомой схемы 1 отличается от эталонного значения, записанного в регистрах 12, то на выходе элемента 14 появляется сигнал, который через элемент ИЛИ 15 поступаетна элемент И 16. Элемент И 16 при наличии сигнала с блока 6 выдает сигнал на блок индикации 17, где также зафиксирован номер проверяемой схемы 1 по информации поступающей с узла 23. Для подключения и проверки другой контролируемой схемы необходимо подать управляющее воздействие с узла 23 вь бора контротфуемой схемы комхтутаторы 2 и 3. С помощью узпа сброса 22 необхоцимо сбросить информакию, aaimсанную в первом 7 и втором 12 регис рак и записать анапогично новую тестовую информаиию, соответствующую новой контропируемой схеме. Дапее процесс контроля аналогичен. Преимуществом разработанного уртро ства явпяется возможность опреаепения технического.состояния контролируемой аппаратуры в процессе выполнения ее ра ёочёй программы, т. е. произвоцить в рсйпьном масштабе времени. Это поа оляет исключить распространение неисп правности по системе, что позволит ло:1:апгкзовать место неисправности с точ-« носа-ью ар контролируемого блока, а это п.авт возможность сократить время отыск ния и устранения неиспр;авности, так как время отыскания и замены неиспра& ного блока опрецеляется Та t -tjfi, где -t-i время реализации диагностиг ческой программы} 2 - время (Дешифрации результатов тестового контроля; г время замены неисправного При иоюльзовакии разработанно1ч устройства Т в основном определяется tj неисправ ного яблока. Кроме TWO, устройство использования аля снфецеленвя электричеоки неразличнмык неисправностей на УОО&не контролируемых блоков сокращает время отыскания неразличимых неисправностей, так как нужно буцет производить блочную замену блоков с целью отыскания неисправного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1166119A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля узлов электронных вычислительных машин | 1976 |

|

SU667969A1 |

| Устройство для тестового контроля цифровых узлов электронно-вычислительных машин | 1981 |

|

SU993266A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛСГИЧЕСКИХ СХЕМ, содержащее пульт управления, блок ввода исходной , информации, первые выходы которого соединешд с информационными входами первого регистра, вторьте регистры, вхрды сброса которых подключены к первому выходу пульта управления и входу сброса первого регистра, блок выделения неисправностей, элемент ИЛИ и блок индикации, о т л и ч а ю щ е е с я тем, что, с целью повышения эффективности контроля, в устройство введены первые блоки совпадения по числу вторых регистров, группы первых элементов И по числу вторых регистров, первый коммутатор и последовательно . соединенные второй коммутатор, дешифратор, группа вторых элементов И, второй блок совпадения и третийэлемент И, второй вход которого подключен к выходу элемента ИЛИ, а выход к входу блока индикаини, управляющий вход которого соединен с управляющими входами обоих коммутаторов и со вторым выходом пульта управления, третий выход которого подключен ко вторым входам вторьвс элементов И., группы ,,а четвертый выход - к управ ляюшим входам первых элементов И группы,информационные входы которых соединены со вторьши выходами блока ввода исход} ой информации, а выходы подключены ко входам соответствующих вторых регистров, выходы кото(Л рых соединены с первыми входами соответствующих первых блоков совпадес: ния, вторые входы которых соединены с выходами вторых элементов И группы, а выходы первых блоков совпадения подключены к переым вхоодм блока выделения неисправностей, вторые входы -коо торого подключены к выходам первого 4 коммутатора, а выходы - ко входам элемента ИЛИ, вторые входы коммутатоОО ров являются информационными входа ми устройства. Од

18

18

19

13

-LJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для поиска неисправностей бесповоротных комбинационных схем | 1974 |

|

SU526834A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

Авторы

Даты

1983-10-15—Публикация

1981-10-23—Подача