(54) УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

1

Изобретение относится к электронной вычислительной технике и может быть ис пользовано в аготаратуре автоматического контроля и диагностики цифровых узлов.

По основному авт. св. № 694863 известно устройство для тестового конт- роля цифровых узлов ЭВМ, содержащее последовательно соединенные запоминающий блок для хранени51 тестов, блок записи информации, регистр теста, комму- ,о татор, блок управления, блок сравнения,, регистр сдвига и проверяемый блок СЦ.

Недостатком этого устройства является то, что .нагрузка на выходные элемённ ты проверяемого изделия для всех кана- vs лов и для всех изделий одинакова и определяется величиной выходного сощ)оти& ления элемента И-НЕ. Между тем, для более полной проверки изделия необходимо при его контроле иметь возможность. 2о имитировать наиболее тяжелые режимы работы изделия, когда его выходные эл&. менты имеют максимальную нагрузку, при этом, так как выходные могут быть

нагружены на один или несколько элемент тов внутри проверяемого изделия (обратные связи), то понятно, что величина тока нагрузки, имитируилая при проверке, должна иметь возможность изменяться от минимального до максимального зна- че1гия с дискретностью, равной току, создаваемому одт1М элементом.

Цель изобретения - повышение надеж ности работы устройства за счет контроюля выходных элементов испытуемого изделия имитацией наиболее тяжелых работы.

Поставленная цепь достигается тем, что в устройство для тестового контроля цифровых узлов электронных вычиспитольных машрн введены группа регистров ксм дов нагрузки и группа формирователей параметров сигналов нагрузки, причем групйа выходов регистра теста подключ на соответственно к входам каждого р&гистра кодов нагрузки грушш, группа выходов казкдого из которых пошипочвЕк к группе входов соответствующего формв «

роватепя параметров сигналов нагрузки группы, выход каждого из которых подключен и: первому входу соотвегствунлцего элемента И коммутатора, третья группа &ЫХОДОВ блока управпешш подключена к управляющим входам регистров кодов нагрузки грухшы.

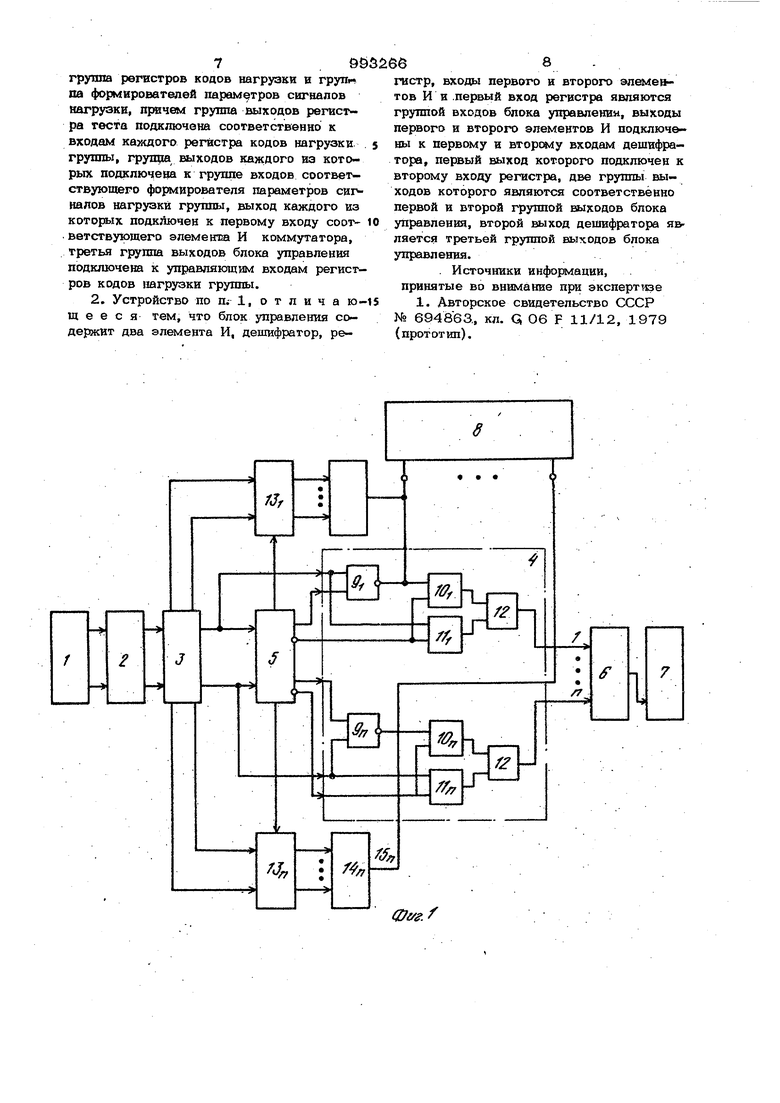

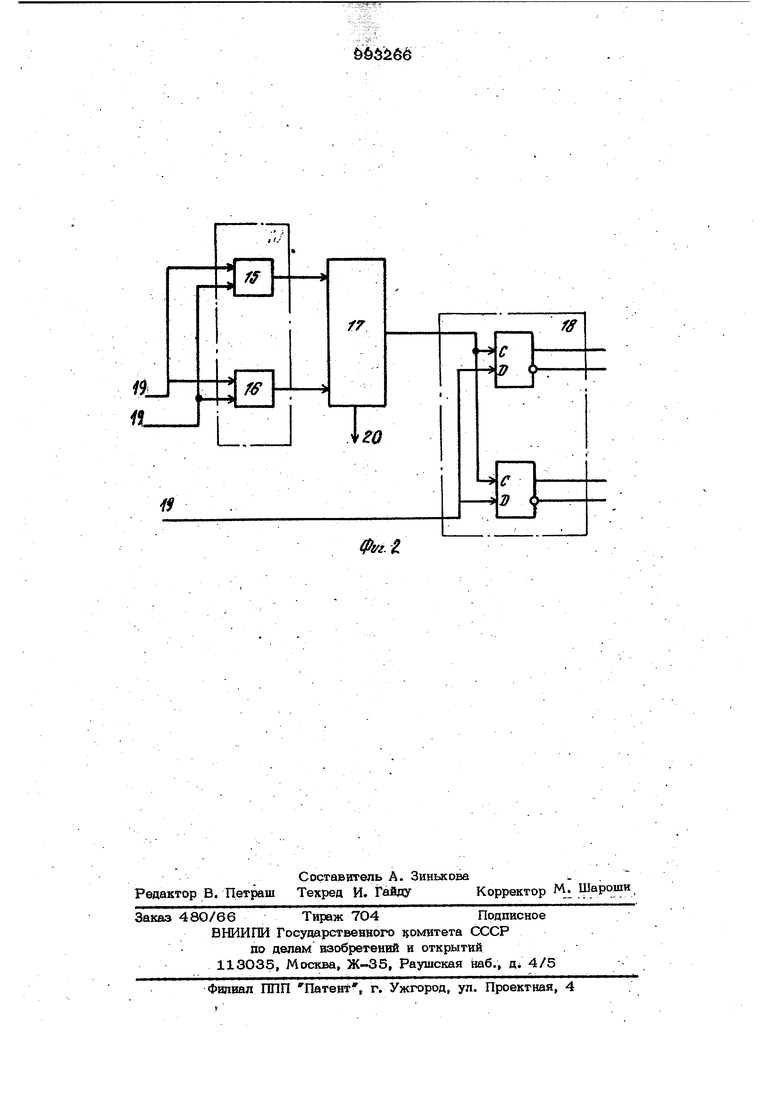

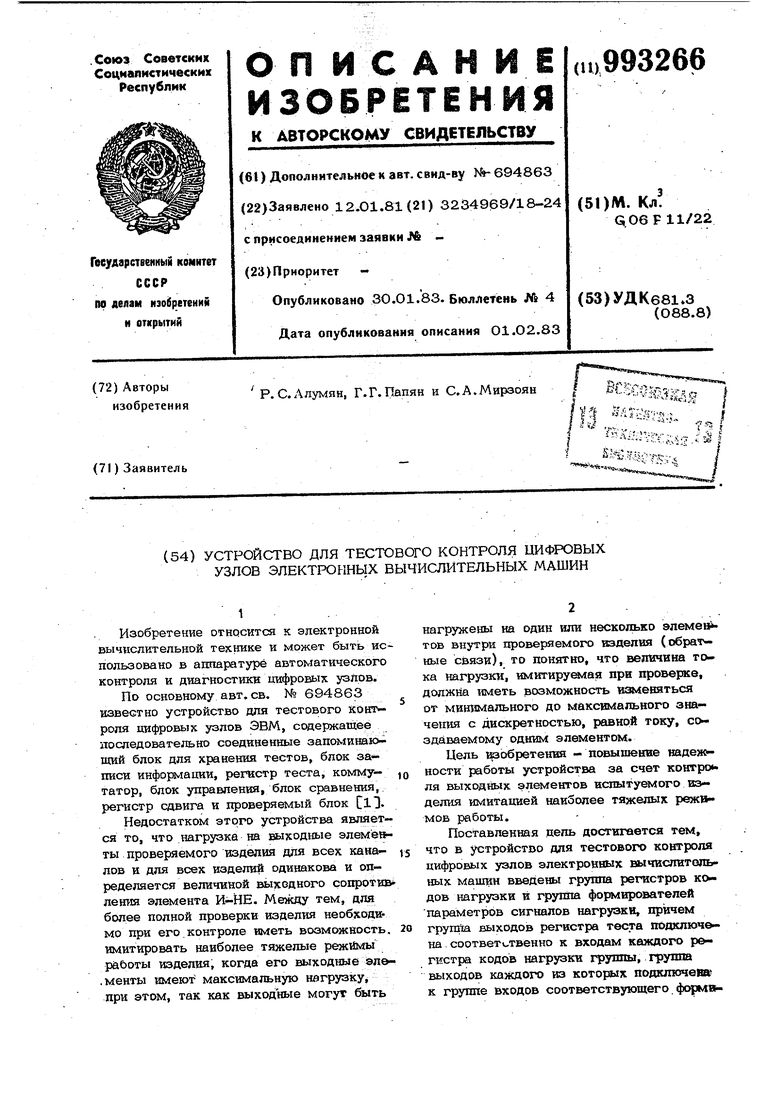

Кроме того, блсж управления содержит два элемента И, дешифратор, регистр, входы первого и второго элементов И и первый вход регистра являются группой входов блока управления, выходы первого и второго элементов И подключены -к первому и второму входам дешифратора. первый выход которого подключен к Bjopo му входу регистра, две группы выходов которого являются .соответственно первой и второй группой выходов блока управления, второй выход дешифратора является третьей группой выходов блока управлений. На фиг. 1 предстаьлена структурная схема предлагаемогпэ устройства; на фиг. 2 - схема бпока управления. Устройство содержит запоминающий блок 1 для хранения тестов, блок 2 заЩ1СИ информащш, регистр 3 теста, коммутатор 4, блок 5 управления, блок 6 сравнения, регистр 7 сдвига, проверяемый блок 8, группа элементов И-НЕ р,, две группы элементов И 10/)-1Ор и , группа элементов ИЛИ 12, группа регистров кодов нагрузки, rpyitпа формирователей параметров сигналов нагрузки, два элемента И 15 и 16, дешифратор 17, регистр 18 коммутатора. Устройство работает следуюпщм образом. Проверяемый блок 8 имеет п контактов, каждый из которых может быть входн ным или выходным. В начале каждого теста в запоминающий блок 1 записана информация, которая задает распределение входных и выходных контактов проверяемого изделия и величину нагрузки, которую нужно обеспечить отдельно для каж дого выходного контакта, чтобы проверить работу выходного элемента в наихудшем режиме. Информация из запоминающего блока 1 через блок 2 записи записывается в регистр 3 теста. В начале работы информация о распреДелении входных и. выходных контактов проверяемого изделия из регистра 3 теота поступает в блок 5 управления коммутатором для выработки в парофазном коде сигналов упраштения коммутатором, а информаяэд, определяющая максимальное количество элементов, на которые могут быть нагружены выходш 1е элементы про веряеМого изделия в двоичном коде, поступает из регистра 3 теста в регистры .

Двоичный код нагрузки с выходов регистров поступает иа входы формировать лей , на выходах которых формируются токи, значения которых зависят от двоичного кода записанных в соответ. ствующих регистрах (отметим, что если контакт проверяе «ого изделия является входным, то в соответствующих регистрах записывается нулевая информация и а выходах формирователей токи не форируются). Указанные токи по существу являются аксимально допустимыми выходными тоами для соответствующего выходного элемента проверяемого изделия. В исходном состоянии на единичных выходах блока 5 поддерживаются сигналы О, т.е. элементы И-НЕ р закрыты, а элементы И 1О,,-1О, и 11-1-11, . В начале работы устройства на регистр 3 теста постуйают команды у1ьравления коммутатором и информация о величине нах-рузочной способности выходного элемента проверяемого изделия. Блок 5 управления принимает команды управления, деши(ЙРИрует, вырабатывает разрешающие сигналы для принятия и формащда о нагрузочной способности из регистра 3 теста в регистры, устанавливает сигнал IHa единичных выходах блока 5, которые соответствуют входным контактам проверяемого блока 8, и си1 налы О, соответствующие выходным контактам проверяемого блока 8. Блок 5 управления поддерживает выработанные сигналы до конца прохождения теста и запрещает принятие последующих сигналов с регистра 3 теста в блок 5 управления И регистры 13-j-13n. Рассмотрим работу устройства, считая, например, что первый контакт npt веряемого изделия является входным. При этом блок 5 управления после прихода ксшанды управления и дешифрирования ее обеспечивает открытие элемента 9 и закрытие элементов 1О и 11/|, тем самым обеспечивая прохождение информации из регистра 3 теста на первый контакт проверя0,4ого блока 8 и блокируя прохождение информации на блок 6 сравнения (в регистре 13 записаны нули и через формирователь 14 ток не проходит).

Если первый контакт проверяемого блока является выходным, то блок 5 уи-равленвя обеспечивает крытие элеме та It-HE Q н открытие элементов И lOyj и И 11. В этом случае формирователь 14, ТО1Ш формирует toK, величина которого определяется кодой записанным в регистре 13, кото{йлй протекает через Еаыходной элемент при максимально допустимой нагрузке. Информация с выходного контакта проверяемого блока 8 через элементы И 10, ИЛИ 12,j поступает на блок 6 сравнения, туда же для сравнения поступает эталонное значение выхода проверяемого блока с регистра теста через элементы И 11 и ИЛИ 12,. Для обеспечения .нормального функоионирования , элемент И-НЕ 9 имеет Rgj., вза фытом состоянии. Шок 6 сравнения формирует сигналы О или 1 на каждом наборе тестаВ завистшюсти от равенства выходных сигналов проверяет ого блока и эталонных значений сигналов, поступающих с регистра теста. В случае равенства йырабатывается сигнал О, в неравенства хотя бы на.одном из контактов- .

Сигналь из блока 6 сравнения поступают на регистр 7 одвига, где формиру ется синдром неисправности. Синхроназация всего устройства обеспечивается синхроимпульсами, поступающими с регистра теста. В начале проверяющей тест программы каждого изделия написана информация о распреде}1&нив входных и йлходных контактов провертемого издешв. В проверяющей тест-программе написана, также информация, определяюгцая максемальиое количество элементов, на которые могут быть нагружены выходные элементы пpoвepяe foгo изделия в двоичном коде. В структуре слова кроме этих инфору1аций указывается также номер абонента, который должен принять эту информацию. В структуре слова один разряд выделяется для сигнала сопровождения.

Информационная часть слова вз блока 1 памяти через блок 2 записи и блок 3 теста лерез щнну 19 поступает на И.1ФЭР мационные входы регистра 18 коммутатора и регистров Зр нагрузки, а адресная часть слова, указывающая номер абонента, через шину 19 поступает на .первые входы элементов И 15 и 16.

При наличии сигнала сопровождения на входе 19 а;цресная часть слова через . элементы И поступает на .входы дешифратора 16. По номеру абонента, записанному в адресной части программы, нвформа ПИЯ принимается регистром 18 кок{мутатора или регистрами , нагрузки при помощи выбранного выхода из выходов 2О дешифратора.

При отсутствии .сигнала сопровождения информационная .и адресная части иин формации првш1маК}тся только регистром 3 теста как тестовая информация.

Контроль испытуемого шделия проквэводится двумя режимами. Сначала пронэ|водится тестовая проверка изделий, при Которой в начале работы регистр 18 уста навл ается в соответствующее входу выходу состояние {для входных контактов единичное, для выходных - нулевое). Трш геры всех регистров устанавливаются в нулевое состояние, поэтому на выходной щине формирователей 14.-14 ток не формируется. Работа предлагаемого устройства при тестовой проверке Ни чем не отличается от работы устройства-прототипа.

Если испытуемое юделие прошло тестовую проверку, начинается проверка вы ходных элементов изделия на нагрузочную способность. Наиболее тяжелый режим par боты элемента бывает тогда, когда да его выходе установлен низкий уровеоь. Поэтому тест-программа проверки изделия на нагрузоч гю сяюсобвость составлявется так, чтобы на всех выходных элемешах устававливался низкий уровень. Предположим, что на выходе выходного элемента первэого контакта усташ)влен шкзквй уровешэ. В penEicrpe 13) записыве ется двоичный код максимальной вагрузкв Открываются соответствуклове разрадвые ключи формирователя 14 и сформвхювавш 1й на общей шине Шход1ю й тшс втекает через выходной тракзистор выходного элемента. На .выходе исправной (с точки зрения нагрузочной способности); микросхемы нулевой уровень не меняется На выходе 1шис1фавной микросхемы появятся сбои, которые через элементы 1О а 12поступают на блок 6 сравнения, оттуда на регистр 7 сдвига. Даже при одном сбое на,выходе регистра 7 сдвига может формироваться синдром неирправности.

Формула изобретения

. 1. Устройство для тестового контроля цифровых узлов электронных вычислительных машин по авт. ев, № 694863, отличающееся тем, что, с целью повышения надежности, в него введены

грутша регистров кодов нагрузки и групг. па формирователей параметров сигналов нагрузки, причем группа выходов регистра теста подключена соответственно к входам каждого регистра кодов нагрузки группы, групца выходов каждого иэ которых подключе1ш к группе входов соответствующего формирователя параметров сигналов нагрузки группы, выход каждого из которь х подключен к первому входу соответствузющего элемента И коммутатора, третья группа выходов блока управления подключена к управляющим входам регистров кодов нагрузки группы.

2. Устройство по п; 1, о т л и ч а юЩ е е с я тем, что блок управления содержит два элемента И, дешифратор, регистр, входы первого и второго элементов И и .первый вход регистра являются группой входов блока управлении, выходы первого и второго элементов И подключи ны к первому и второму входам дешифратора, первый выход которого подключен к второму входу регистра, две группы выходов которого являются соответственно первой и второй группой выходов блока управления, второй выход дешифратора является третьей группой выходов блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 694863,, кл. Q 06 F 11/12, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для контроля цифровых узлов | 1985 |

|

SU1262508A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

фуг.

фуг. I

Авторы

Даты

1983-01-30—Публикация

1981-01-12—Подача