(54) МИКРОПРОГРАШНОЕ УСТРОЙСТВО УПРАВЖНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммный процессор | 1980 |

|

SU980098A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2013803C1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

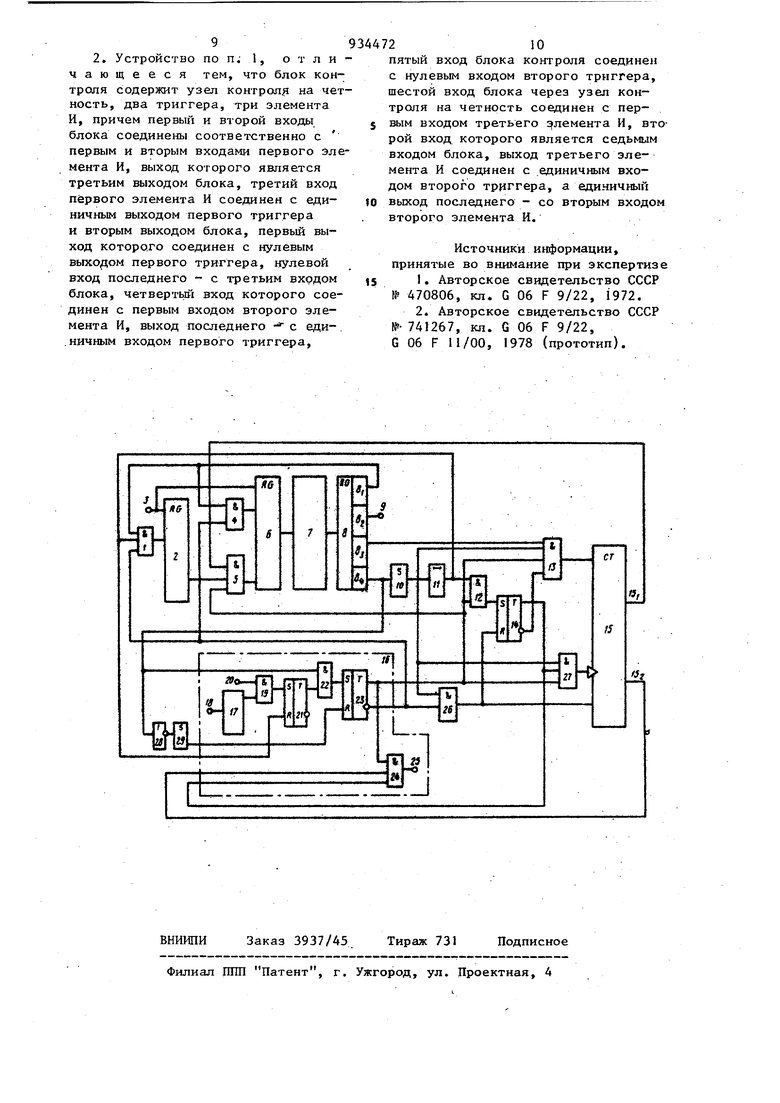

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении микропрограммных устройств и систем с самовосстановлением. Известен микропрограммньи процессор с восстановлением при сбоях, содержащий запоминающий блок, адреса, регистр микрокоманд, регистр адреса повтора, блок контроля, счетчик, элементы И (П. Недостатком указанного устройства является низкая функциональная .надежность, которая также обусловле на возможностью ложной идентификации сбоя как устойчивого отказа. Из известных устройств наиболее близким к предлагаемому является ми ропрограммное устройство управления, содержащее последовательно сое диненные регистр адреса, запоминающий блок, регистр микрокоманд, первый выход которого является выходом микроопераций устройства, а второй соединен с первыми входами первого и второго блоков элементов И, вторые входы которых соединены с первым выходом блока контроля, а ш 1ходы соединены соответственно с первыми входами буферного регистра и регистра адреса, вторые входы которых яв ляются входом начального адреса устройства и вторым входом буферного регистра, выход которого соединен с первым входом третьего блока элементов И, выход которого соединен с третьим входом регистра адреса, второй вход - соединен со вторым выходом блока контроля, третий вход - соединен с первым входом счетчика, информационшлй вход которого соедчинен с выходом четвертого блока элементов И, второй выход счетчика соединен с первым входом блока контроля, второй последнего - с единичным выходом триггера, единичный и нулевой входы которогосоединены с выходами первого и второго элементо И соответственно t2. Недостатком известного устройства является низкая экономичность, обусловленная большой избыточностью средств контроля и исправления ошибок, а также низкая экономичность у ройства, которая обусловлена большой разрядностью счетчика, в которы записывается суммарное допустимое время выполнения участка. Цель изобретения -.повышение эко номичности средств контроля и восстановления. Поставленная цель достигается тем,что микропрограммное устройство дополнительно содержит элемент НЕ, два формирователя импульсой, элемен задержки и третий элемент И, выход которого соединен со счетным входом счетчика, установочный вход которог соединен с выходом второго элемента И, первый выход блока контроля соединен с первым входом второго элемента И, третий вход блока контроля соединен с выходом первого форгадрователя импульсов, вход которого через элемент НЕ соединен с четвертым входом блока контроля, выходом метки регистра микрокоманд и входом второго формирователя импульсов, выход которого соединен со вторым входом второго элемента И, первым входом третьего элемента И, первым входом четвертого блока элементов И, а через элемент задержки - с пятым входом блока контроля, с третьи входом первого блока элементов И и первым входом первого элемента И, второй вход которого соединен со вт рыми входами третьего элемента И, третьего и четвертого блоков элементов И и вторым выходом блока кон троля, третий вход которого соедине с выходом логических условий регис ра микрокоманд, четвертый вход четвертого блока элементов И соединен с нулешз1М выходом триггера, единичный выход которого соединен с третьим входом третьего элемента И, шестой, седьмой входы и третий выхо блока контроля являются соответственно первым и вторым информационными входами и выходом отказа устройства. Кроме того, блок контроля содер- жит узея контроля а четность, два триггера, три элемента И, причем пе вый и второй входы блока контроля соединены соответственно с первым и; вторым входами первого элемента И, выход которого является третьим выходом блока контроля,третий вход первого элемента И соединен с единичным выходом первого триггера и вторым выходом блока контроля, первый выход которого соединен с нулевым выходом первого триггера, нулевой вход последнего - с третьим входом блока контроля, четвертый вход которого соединен с первым входом второго элемента И, выход последнего с единичным.:входом первого, триггера, пятый вход блока контроля соединен с нулевым входом второго триггера, шестой вход блока контроля через узел контроля на четность соединен с первым входом третьего элемента И, второй вход которого является седьмым входом блока контроля, выход - соединен с единичным входом второго триггера, а единичный выход последнего со вторым входом второго элемента И, Повышение экономичности устройства обеспечивается путем снижения избыточности средств контроля и восстановления за счет использования свободных полей микрокоманд для задания полезной информации и исключения ассоциативной памяти. Устройство работает следующим образом. Реализуемые микропрограммы разбиваются на отдельные участки - микроподпрограммы. Восстановление информации осуществляется путем повторения микропрограмм при обнаружении ошибок в хЪде их выполнения. В свободном поле логических условий последней: микрокоманды каждой микропрограммы задается допустимое число повторений данной микроподпрограм мы. Это число выбирается для каждЪго участка, исходя из общего запаса времени работы предлагаемого устройства и управляемого им объекта. Если после указанного числа повторений микроподпрограммы ошибка не самоустраняется, то фиксируется отказ устройства:, На чертеже приведена функциональная схема предлагаемого микропрограммного устройства управления. Устройство содержит первый блок .1 элементов И, буферный регистр 2 со входом 3 начального адреса, второй 4 и третий 5 блоки элементов И, регистр 6 адреса, запоминаю1 щй блок 7, регистр 8 микрокоманд с полями: адресным 8, микроопераций 8«логи ческих условий (числа повторений) 8j, метки 84. и выходом 9 микроопераций, второй формирователь 10 импульсов, первый элемент 11 задержки, первый элемент И J2, четвертый блок 13 элементов И, триггер 14, счетчик 15 с первым 15 и вторым 15ц выходами, блок 16 контроля, в состав которого входят узел 17 конт рсхпя на четность с шестым входом 18 блока, третий элемент И 19 с входом 20 блока, второй триггер 21, второй элемент И 22, первый триггер 23 и первый элемент И 24 с третьим выходом 25 блока. Кроме того, устройство содержит так же второй 26 и третий27 элементыИ, элемент ИЕ 28 и первый формирова- тель 29 импульсов, В запоминающем блоке 7 хранятся микропрограммы, выполняемые пред лагаемым устройством. Каждая микрокоманда имеет четыре поля: адресное 8, микроопераций 8, логических условий 8 и поле метки 8д. В поле метки 8 записывается единица для микрокоманд, которые являются последними в участках. При этом в попе 8 j указывается код возможного числа повторений соответствующего участка. Во всех других микрокомандах в поле 8д записывается нуль, и в поле 8 - либр код проверяемых логических условий, либо нулевой код. Счетчик 15 служит для подсчета числа повторений участков в случае их искажений. Устройство работает в двух режимах: режиме нормального функциониро вания и режиме восстановления информации. В исходном состоянии все элементы памяти находятся в нулевом состоянии, а регистры 2 и б записыванг начальный адрес, поступающий на вход 3. В первом режиме по адресу, хранимому. в регистре 6, из блока 7 счи тываются микрокоманды. Сигналы микроопераций с поля 8 регистра 8 поступают на выход 9, а очередной адрес с поля 8, передается в регистр 6 через блок 4 элементов И, Затем из блока 7 считывается очередная микрокоманда и работа устройства продолжается аналогично описанному выше. Одновременно осуществляется контроль его функционирования, В каждом NBiKpOTaKTe по сигналам на входе 20 опрашивается состояние выхода узла 17, на вход 18 которого поступают считывае1« 1е микрокоманды. Если искажения отсутствуют, то триггер 21 сохраняет нулевое состояние, При этом после считыва п я последней микрокоманды участка и появления сигнала на выходе поля 8 триггер 23 остается в нулевом сос тоянии, запрещая запись информации в счетчик 15 через блок 13 элементов И и триггер |4 через элемент И 12, Одновременно разрешается запись .начального адреса следующего участка в регистр 2 через блок 1 элементов И. В режиме восстановления информации устройство работает следукяцим образом. Если в процессе выполнения очередного участка на выходе узла 17 появляется сигнал сбоя, то этим сигналом через элемент И 19 триггер 21 устанавливается в единичное состоя ьше. После считывания из блока 7 последней микрокоманды участка сиг.налом с выхода 84 через элемент Н 22 триггер 23 устанавливается в единичное состояние. Формирователь 10 формирует импульс, которым из поля 8j- регистра 8 через блок 13 элементов И в счетчик 15 записывается код числа возможных повторений данного участка. Одновременно нулевым сигналом с выхода триггера 23 запр ещается передача начального адреса следующего участка в регистры 2 и 6 и разрешается передача начального адреса данного участка в регистр 6 из регистра 2 (на третьем входе блока элементов И 3 также единичный сигнал с выхода 15 счетчика 15). Через время, определяемое элементом задержки 11 триггер 21 обнуляется, триггер 14 устанавливается в единичное состояние, а начальный адрес данного участка передается в регистр 6 через блок 5 элементов И. После этого начинается повторное выполнение данного участка. По очередной (первой) считанной микрокоманде происходит обнуление триггера 23, поскольку на выходе элемента НЕ 28 появляется высокий потенциал {в поле .считывается нуль) .и формирователь 29 формирует сигнал обнуления, В результате триггер 23 разрешает передачу из поля 8 через блок элементов Ид в регистр 6, По мере считывания микрокоманд осуществляется их контроль узлом 17 и триггером 21. Если сбой вновь обнаружен, то после считываНИН последней микрокоманды участка происходит вычитание единицы из содержимого счетчика 15 через открытый элемент И 27 и участок вновь повторяется. Если после очередного повторения сбой не появляется, то триггеры 21 и 23 остаются в нулевом состоянии и по единичному сигналу в поле 8 формирователь 10 осуществит обнуление счетчика 15 и триггера 14, и устройство перейдет в первый режим работы. Если после очередного пбвторения ошибка не устраняется и счетчик 15 устанавливается в нулевое состоя ние (появляется единичный сигнал на выходе 15п), то в этом случае формируется сигнал отказа. Этот сигнал появляется на выходе 25 элеMeiiTa И 24, поскольку триггеры 23 и 14 находятся в единичном состоянии и появляется единичный сигнал на выходе 15 (счетчика 15. После этого осуществляется локсШизация отказавшего элемента, поскольку автоматическое восстановление невозможно. Следовательно, предлагаемое устройство превосходит по экономичности средств контроля, обладая теми же функциями восстановления. Использование изобретения позволяет строить более простые и надежные самовосстановливаемые микропрограммные устройства управления. Формула изобретения 1. Микропрограммное устройство управления, содержащее последова- . тельно соединенные регистр адреса, запоминающий блок, регистр микрокоманд, выход микроопераций которого является выходом микроопераций устройства, адресный выход соединен с первыми входами первого и второго блоков элементов И, вторые входы которых соединены с первым вы ходом блока контроля, а выходы первого и-Второго блоков элементов И соединены соответственно с первыйи входами буферного регистра и регист ра адреса, вторые входы которых являются входом начального адреса устройства, буферного регистра соединен с первым входом третьего блока элементов И, выход которого соединен с третьим входом регистра адреса, второй вход третьего блока элементов И соединен со вторым выходом блока контроля, а третий вход - с первым выходом счетчика, информационный вход которого соединен с выходом четвертого блока элементов И, второй выход счетчика соединен с первым входом блока контроля, второй вход последнего - с единичным выходом триггера, единичный и нулевой входы которого соединены с выходами первого и второго элементов И соответственно, отличающееся тем, что, с целью повьшения экономичности средств контроля и восстановления, оно дополнительно содержит элемент НЕ, два формирователя импульсов, элемент задержки и третий элемент И, выход которого соединен со счетным входом счетчика, установочный вход которого соединен с выходом второго элемента И, первый выход блока контроля соединен с первым входом второго элемента И, третий вход блока контроля соединен с выходом первого формирователя импульсов, вход которого через элемент НЕ соединен с четвертым входом блока контроля, выходом метки регистра микрокоманд и входом второго формирователя импульсов, выход которого соединен со вторым входом второго элемента И, первым входом третьего элемента И, первым входом четвертого блока элементов И, а через элемент задержки с пятым входом блока контроля, с третьим входом первого блока элементов И и с первым входом первого элемента И, второй вход которого соединен со вторыми входами третьего элемента И, третьего и четвертого блоков элементов И и вторым выходом блока контроля, третий вход которого соединен с выходом логических условий регистра.микрокоманд,. а четвертый вход четвертого блока элементов И соединен с нулевым выходом триггера, единичный выход которого соединен с третьим входом третьего элемента И, шестой и седьмой входы и третий выход блока контроля являются соответственно первым и вторым информационными входами и выходом отказа устройства.

3447210

пятый вход блока контроля соединен с нулевым входом второго триггера, шестой вход блока через узел контроля на четность соединен с первым входом третьего з(лемента И, второй вход, которого является седьмым входом блока, выход третьего элемента И соединен с .единичным входом второго триггера, а единичнь й to выход последнего - со вторым входом второго элемента И.

Источники информации, принятые во внимание при экспертизе 15 1. Авторское свидетельство СССР № 470806, кл. G 06 F 9/22, 1972.

Авторы

Даты

1982-06-07—Публикация

1980-10-28—Подача