первого триггера, выход пятото элемента И соединен с вторым входо второго элемента 1ШИ и с третьим входом

первого элемента ИЛИ, выход которого является первым выходомблока сЬиксации сбоев.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1024920A1 |

| Микропрограммный процессор с контролем | 1980 |

|

SU862144A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

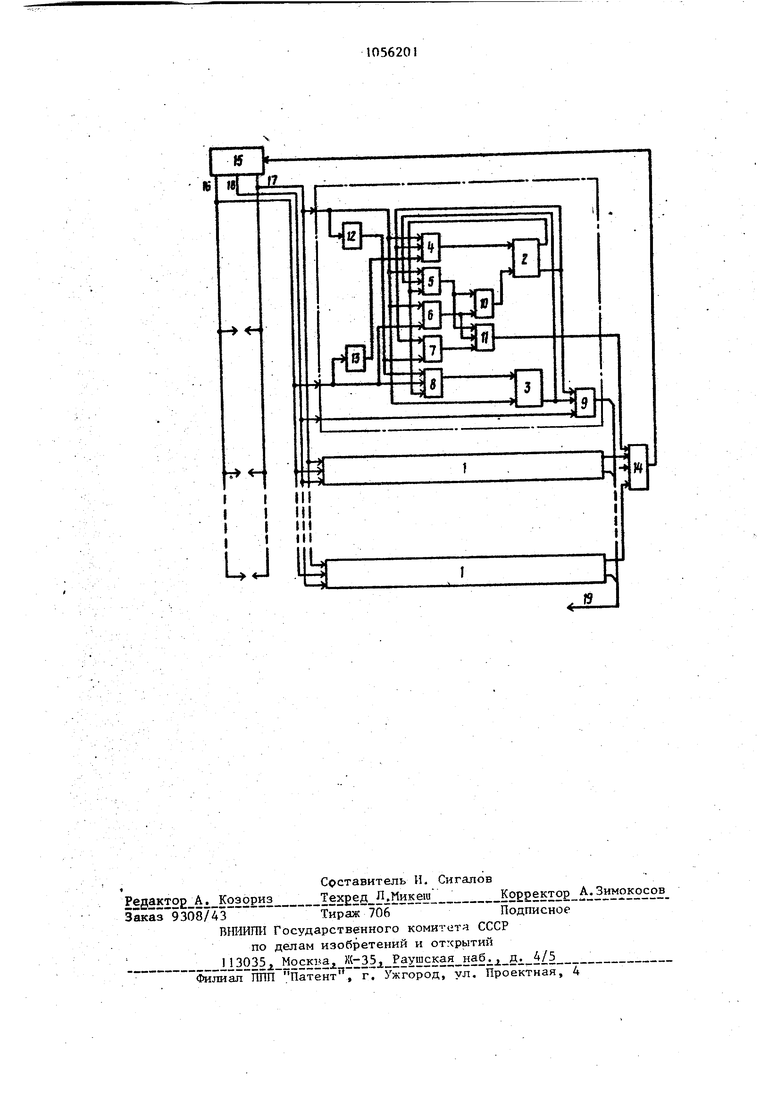

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении аппаратурных средств контроля микропрограммных устройств управления микропроцессоров и обычных ЭВМ. Известно устройство для контроля выполнения последовательности микрокоманд, содержащее элементы И, ИЛИ, связанные с управляющими шинами, и триггер ошибки П . Недостатками известного устройства являются ограничения Лунктдиональных возможностей, связанные с необходимостью выработки только одного управляющего сигнала и только на одной рмне, и необходимостью жесткого чередования сигналов чтения и записи, что при известных ограничениях для микропроцессоров по быстродействию создает дополнительные трудности, а также необходимость увеличения размерности управляю1цей тины и усложнения устройства управления, св занные с введением контрольных кодов и управлением иьш., 1 Наиболее близким по технической сурщости к изобретению является уст, ройство дпя контроля выполнения последовательности микрокоманд, содер ;а1цее п блоков фиксации сбоя (по числу регистров процессора) и два элемента ИЛИ. Работа устройства основана на том, что выполнение любой микропрограммы в машине осу1цествляется путем передач данных между регистрами через арифметико-логический блок под управлением сигналов чтения и записи, nocTynaronpix из блока управления на входы каждого из N регистров. Причем, если на -ьй регистр подается сигнал записи, то независи го от такта микропрограммы с него должна быть считана инсюрмация подачей соответствующего сигнала чтения Г21 . Однако известное устройство , требует строгого чередования управляюпц х сигналов записи и чтения для каждого регистра, что может быть приемлемо лишь дпя ряда регистров, выполненных на ферритопых сердечниках при условии, что олера1щя регенерации будет интерпретирована как процесс выполнения очередной команды записи. Для операционных же блоков, реализованных по интегральной технологии, такое устройство не допускает использование микропрограмм с многократным считыванием одной и той же информации с одного регистра (как, например, требуется при выполнении микропрограмм умножения с регистра множимого). Кроме того, одновременное поступление на вход i-го регистра сигналов чтения и записи делает реакцию блока фиксации сбоя неоднозначной. Цель изобретения - расширение области применения устройства путем обеспечения контроля микропрограмм с произвольным числом операций считывания одной и той же информации с одного и того же регистра. I Поставленная цель достигается тем, что в устройство дпя контроля последовательности микрокоманд, содержащее элемент ИЛИ и п блоков фиксации сбоев, первые выходы блоков фиксации сбоев соединены с соответствующими входами элемента ИЛИ, выход которого является выходом устройства, вторые выходы блоков фиксации сбоев являются группой выходов устройства, управляющий вход записи устройства соединен с первыми входами всех бло- , ков фиксации сбоев, управляюршй вход чтения устройства соединен с вторыми входами всех блоков фиксации сбоев. управляющий вход считывания состояния устройства соединен с третьими входами всех блоков фиксации сбоев, причем блок Фиксации сбоев содержит первый триггер, первый, второй и третий элементы И, первый вход блок фиксации сбоев соединен с первым вх дом первого элемента И, второй вход блока фиксации сбоев соединен с первым входом второго элемента И, нуле- вой выход первого триггера соединен с вторым входом первого элемента И и с первым входом третьего элемент И, выход которого является вторым выходом блока, третий вход блока фиксации сбоев соединен с вторым вхо дом третьего элемента И, единичный выход первого триггера соединен с вторым входом второго элемента И, в состав блока Ликсации сбоев введены первцй и второй элементы НЕ, первый и второй элементы ИЛИ, четвертый пятый и щестой элементы И и второй триггер, причем первый вход блока фиксации сбоев соединен с первыми входами четвертого и пятого элементов И, с первым входом второго три гера и через первый элемент НЕ - с первым входом шестого элемента И и третьим входом второго элемента И .вы.ходы которых соединены соответственно с первым входом первого элемента ЛИИ и с вторым входом второго триггера, нулевой выход которого сое динен с третьим входом третьего элемента И и с вторым входом четвертого элемента И, второй вход блока фик .сации сбоев соединен с вторым входом пятого элемента И и через второй эле мент НК с третьим входом первого эле мента И, выход которого соединен с первым-входом первого триггера, единичный выход которого соединен с третьими входами четвертого элемента И, нулевой выход первого триггера соединен с вторым входом шестого эле мента И, выход четвертого элемента И соединен с вторым входом первого эле мента ИЛИ и с первым входом второго элементаЦЛИ, выход которого соедине с вторым входом первого триггера, выход пятого элемента И соединен с вторым входом второго элемента ILTOI и с. треть йм входом первого элемента ИЛИ, выход которого является первым выходом блока фикслции сбоев. Па чертеже показана схема предлагаемого ycTpoi tcTi a. Устройство содержит п блоков 1 фиксации сбоя, каждый из которых включает первый 2 и второй 3 триггеры, первый 4, четвертый 5. пятый 6, шестой 7, второй 8 и третий 9 элементы И, второй 10 и первый 11 элементы ИЛИ, первый 12 и второй 13 элементы НЕ, а также, элемент ИЛИ 14. Выполнение микропрограммы как процесс передачи данных между регистрами или через арифметико-логический блок организуется контролируемым блоком 15 микропрограммного управления с выходом 16 управляющим чтением, с выходом 17 управляющим записью, управляюп1им выходом 18 считывания. Выполнение микропрограммы считается правильным, если на i-ый регистр сначала придет сигнал записи, затем независимо от такта микропрограммы один или несколько сигналов чтения. При этом блок 1 фиксации сбоя не выдает сигнал ошибки с первого выхода и работает следующим образом. Перед выполнением микропрограммы первый и второй триггеры устанавливаются предварительно в нулевое состояние (эти цепи не показаны), Далее изменения состояний триггеров и фop шpoвaниe выходных сигналов происходит в такой последовательности:а)при поступлении на 1-ый регистр первого сигнала записи через первый вход блока 1 фиксации сбоя этого регистра первый триггер 2 перебрасывается в единичное состбяние сигналом, поступаю1 1им на единичньй вход через элемент 4 И, второй триггер 3 остается в нулевом состоянии. Сигнал ошибки на первом выходе блока фиксации сбоя при этом отсутствует; б)при последующем поступлении на второй вход сигнала чтения второй триггер 3 перебрасывается в единичное состояние сигналом, поступаю1т1им на его единичный вход через элемент И 8, первый триггер 2 остается в .единичном состоянии, сигнал ошибки не выдается; в)если очередной сигнал, подаваемый на этот же регистр, тоже чтение, то состояния триггеров блока фиксации сбоя при этом не изменяются и сигнал ошибки не выдается. Сиг- на.4 чтения может поступать произвольное число раз; г)при последуюием поступлении на i-ый регистр сигнала записи второн триггер 3 переходит в нулевое состояние, так как с первого входа блока 1 фиксатдии сбоя осуществляется . непосредственное воздействие на. нулевой вход, первый триггер 2 остается в единичном состоянии, сигнал ошибки с первого выхода блока не выдается; д)если очередной сигнал является чтением, то с второго входа блока i второй триггер 3 переводится в единичное состояние через элемент И 7, первый триггер 2 остается в единичном состоянии, сигнал ошибки не вьщяется; , ej при поступлении последуюпрх сигналов на -ый регистр работа блока «фиксации сбоя осуществляется в соответствии либо с п.q , либо п.Ъ в зависимости от поступающих сигналоя При выполнении последовательности микрокоманд возможны:ошибки, состоящие для 1-го регистра в возникновении ложного или пропадании дейст.вительного управляющего сигнала. Про .является и обнаруживается это следую |ЩИм образом. Если нарушается чередование сигналов чтения и записи .и первым на t-ый perTiCTp приходит сигнал чтения то первый 2li второй 3триггеры.блока фиксации сбоя 1-го регистра остаются в нулевом состоянии, а через элемент И 6 и второй элемент ИЛИ 1 на первый выход блока 1 проходит сиг.нал .ошибки, который передается через элемент ИЛИ 14 на первый вход блока 15 управления. При появлении второго сигнала записи подряд первый триггер 2 сигналом через элемент И и элемент ИЛИ 10 переводится в нулевое состояние, второй триггер 3 остается в нулевом состоянии как и пос ле первой записи. При этом выдается на первый выход блока 1 сигнал ошибк через элемент И 5 и элемент ИЛИ 1. Если появление ложного сигнала совпадает по времени с приходом действительного, т.е. сигналы чтения и записи поступают на соответствующие Ьходы i-ro регистра одновременно, то фоисходит следующее. . Если сигналы чтения и записи приходят в исходном положении триггеров, т.е. в начале микропрограммы, то их состояние не изменяется, сигнап опгабки выдается через элемент И 6 и элемент ИЛИ 11. . Если сигналы чтения и записи прихоj дят после очередного сигнала записи ьикропрограммы и первый триггер находится единичном состоянии, а второй 3 в нулевом (п.а), то второй 3 триггер остается в нулевом, а nejjвый 2 переводится сигналом через элемент И 6 и элемент ИЛИ 10 в кулевое состо|яние,а через элемент И6 и элемент ИЛИ 1 формируется сигнал ошибки. Если сигнал чтения и записи ириходит после очередного сигнала чте;ния микропрограмг в 1 и оба триггетра ;;находятся В единичном состоянии, то в нулевое состояние первый триггер 2 переводится сигналом, снимаемым с выхода элемента И 6 через элемент ИЛИ 10, а второй триггер 3 - непосредст- венным воздействием с первого входа блока 1. Сигнал ошибки формируется как и в предыдущем случае. Во всех из предложенных вариантов появления ложного или пропадания действительного сигнала формируется сигнал ошибки, а триггеры 1-го блока ймксации сбоя устанавливаютс.я в нулевое состояние, что создает возможность при выдаче сблока 15 управления через управляюпщй выход 18 общего считывакщего сигнала, через третий вход блока Аиксадан сбоя вызвать срабатываиие элемента И 9 и передать таким образом инфор- мацик со всех блоков на информацион ньй вход 19 арифметико-логического блока для использования при локализации места появления ложного или пропадания действительного управ- , ляющего сигнсша.. Таким образом, расширяется область применения предлагаемого устройства контроля для блоков управления, ис- . пользукнчих микропрограмма с много1фатным считыванием одиой и той жё информации с одного регистра, что , при сохранении той же глубины контроля позволяет реализовать более совершенные алгорит1«11 с меньшими затратами времени благодаря уменьшению числа обращений к памяти. Помимо этого контролируется одновременное появление сигналов записи и считывания на входах 1-го регистра, при котором блок (Ъиксагщи сбоя вьщает сигнал ошибки, устраняя тем самым существовавшего неопределенность в работе известного устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Папернов А.А | |||

| Логические OGаовьг ЦВТ | |||

| М., Советское радио, 1972, с | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1983-11-23—Публикация

1982-07-30—Подача