2.Устройство по п. 1, отличающееся тем, что формирователь сигналов корректируемой ошибки содержит дополнительные cy Ф aтopы

по модулю два, выхода которых сое динены с одними из входов первого элемента И, выход которого является выходом формирователя, входами которого являются другой вход первого элемента И и входы дополнительных сумматоров по. модулю два.

3.Устройство по п. 1, отличающееся тем, что формирователь сигналов некорректируемой ошибки содержит элемент ИЛИ, выход которого подключен к одному из входов второго элемента И, выход которого является выходом формирователя, входамп которого являются другие входы вч рого элемента Н и входы элемента ИЛИ.

4. Устройство по п. 1, отличаюсцееся тем, что корректор информации содержит дешифраторы, матрицу элементов И и группы элементов И, первьле входы которых подключены к выходам соответствующих дешифраторов, вторые входы объединены и являются одним из входов корректора информации, другими входами которого являются входы дешифраторов и третьи входы одного из элементов И групп, причем первые входы элементов И каждого столбца матрицы объединены и подключены к выходам элементов И первой группы, вторые входы элементов И каждой строки матрицы объединены и подключены к выходам элементов И второй группы, выходы элементов И групп являются выходами корректора информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1322379A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU752502A1 |

| Устройство для исправления ошибок в системах хранения и передачи информации в кодовой комбинации | 1984 |

|

SU1231503A1 |

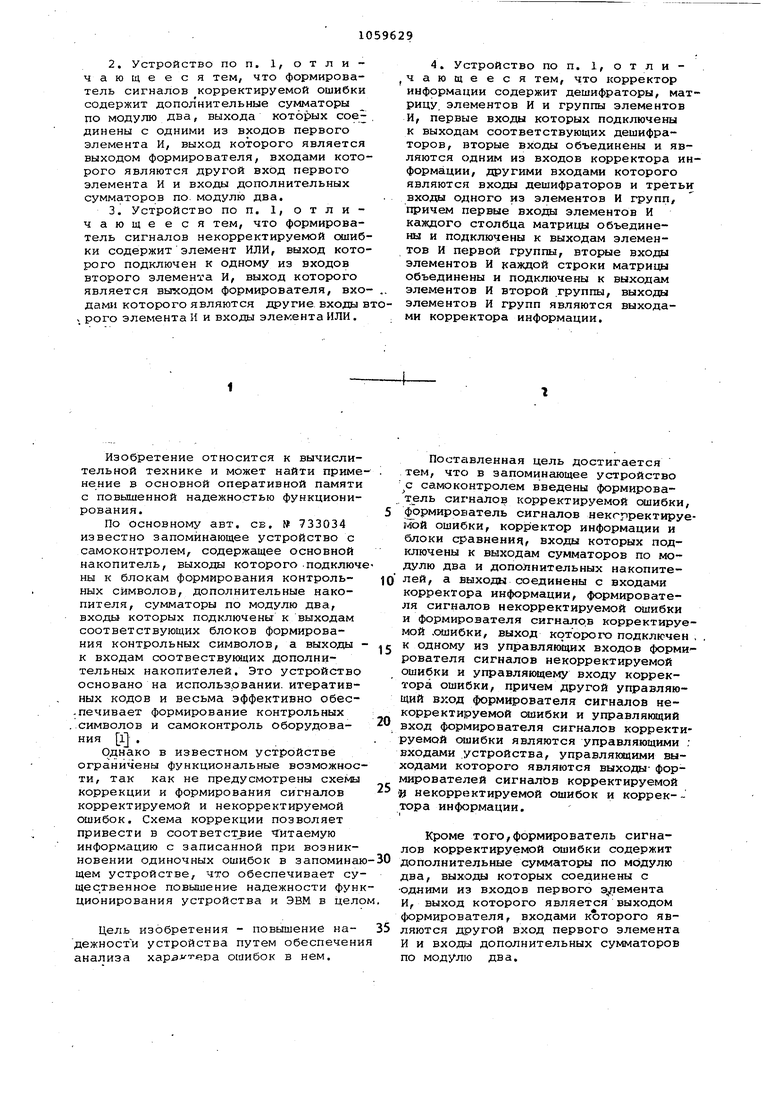

1. ЗАПОМИНАКМЦЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ по авт. св. 733034, отличающееся тем, что, с целью повышения его надежности путем обеспечения анализа характера ошибок, в него введены формирователь сигналов корректируемой ошибки, формирователь сигналов некорректируемой ошибки, корректор информации и блоки сравнения, входы которых / подключены к выходам сумматоров по модулю два и дополнительных накопителей, а выходы соединены с входами корректора информации, формирователя сигнсшов некорректируемой ошибки и формирователя сигналов корректируемой ошибки, выход которого подключен к одному из управляющих входов формирователя сигналов некорректируемой ошибки и управляющему входу корректора ошибки, причем другой управляющий вход.формирователя сигналов некорректируемой ошибки и управляющий вход формирователя сигналов- корректируемой ошибки являются управляющими входами устройства, управляющими выходами которого явля- Jg 1ются выходы формирователей сигналов (Л корректируемой и некорректируемой ошибок и корректора информации. т

Изобретение относится к вычислительной технике и может найти приме нение в основной оперативной памяти с повышенной надежностью функционирования. По основному авт. св. № 733034 известно запоминающее устройство с самоконтролем, содержащее основной накопитель, выходы которого -подключ ны к блокам формирования контрольных символов, дополнительные накопителя, сумматоры по модулю два, входы которых подключены к выходам соответствующих блоков формирования контрольных символов, а выходы к входам соотвествующих дополнительных накопителей. Это устройство основано на использовании, итеративных кодов и весьма эффективно обес..печивает формирование контрольных .символов и самоконтроль оборудования l . Однако в известном устройстве ограничены функциональные возможнос ти, так как не предусмотрены схеки коррекции и формирования сигналов корректируемой и некорректируемой ошибок. Схема коррекции позволяет привести в соответствие читаемую информацию с записанной при возникновении одиночных ошибок в запомина щем устройстве, что обеспечивает су щес,твенное повышение надежности фун ционирования устройства и ЭВМ в цел Цель изобретения - повышение надежности устройства путем обеспечени анализа хара.ь-т«ра ошибок в нем. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем введены формироват ль сигналов корректируемой сяиибки, формирователь сигналов некгрректируемой ошибки, корректор информации и блоки сравнение, входы которых подключены к выходам сумматоров по модулю два и дополнительных накопителей, а выходы соединены с входами корректора информации, формирователя сигналов некорректируемой сяаибки и формирователя сигнало.в корректируемой .ошибки, выход которого подключен , к одному из управлякяцих входов формирователя сигналов некорректируемой ошибки и управляющему входу корректора ошибки, причем другой управляющий вход формирователя сигналов некорректируемой слаибки и управлягаций вход формирователя сигналов корректируемой ошибки являются управляющими ; входами устройства, управлякядими выходами которого являются выходы- формирователей сигналов корректируемой И некорректируемой ошибок и коррек-тора информации. Кроме того,формирователь сигналов корректируемой ошибки содержит дополнительные сумматоры по модулю два, выходил которых соединены с одними из входов первого э гемента И, выход которого является выходом формирователя, входами которого являются другой вход первого элемента И и вход1а дополнительных сумматоров по модулю дв а.

При этом формирователь сигналов некорректируемой ошибки содержит . элемент ИЛИ, выход которого подключен к одному из входов второго элемента И, выход которого является выходом формирователя, входами которого являются другие входы второго элемента И и входы элемента ИЛИ,

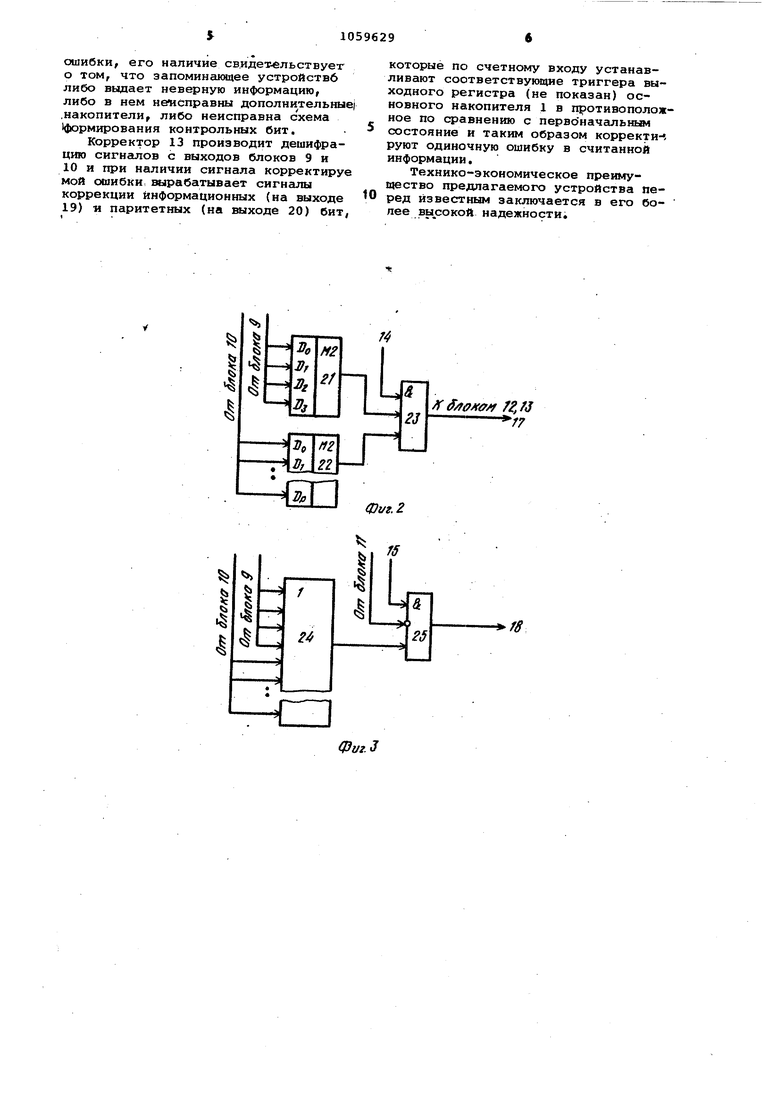

Причем корректор информации содержит дешифраторы, матрицу элементов И и группы элементов И, первые входы которых подключены к выходам соответствующих дешифраторов, вторые входы объединены и являются одним из входов корректора информации, другими входами которого являются входы дешифраторов и третьи входы одного иэ элементов И групп, причем первые входы элементов И каждого столбца матрицы объединены и под-. ключены к выходам элементов И первой группы, вторые входы .элементов И каждой строки матрицы объединены и подключены к выходам элементов И второй группы, выходы элементов И групп являются выходами корректора информации.

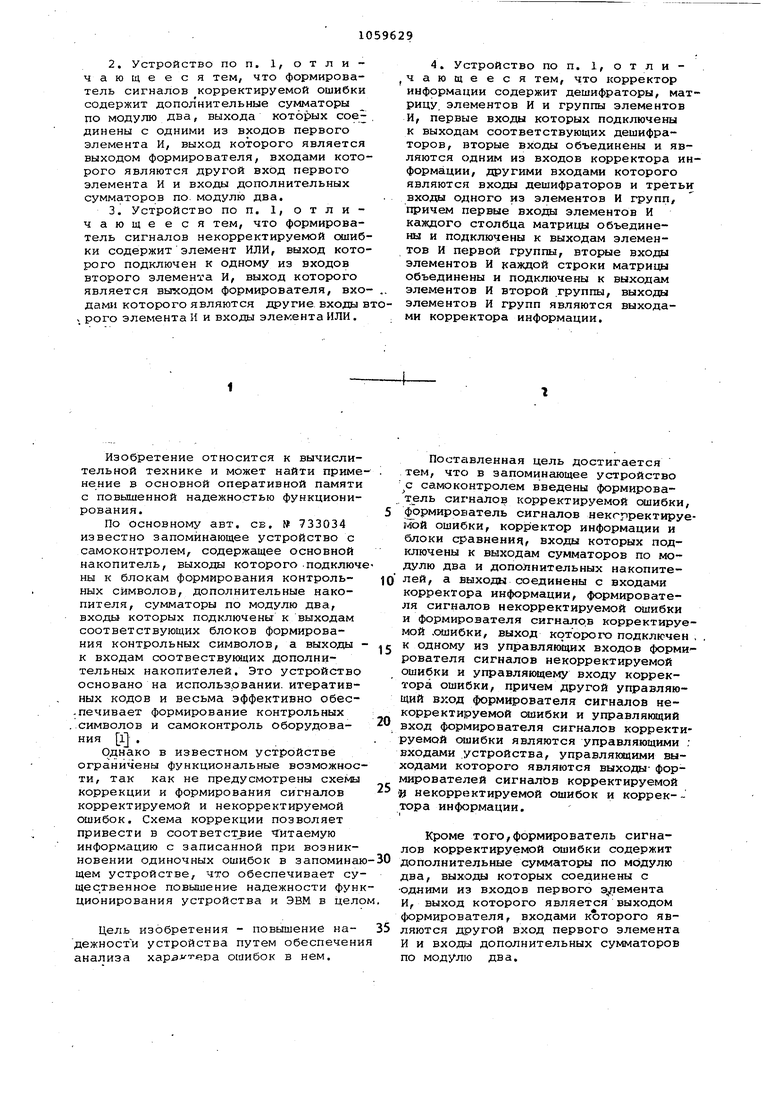

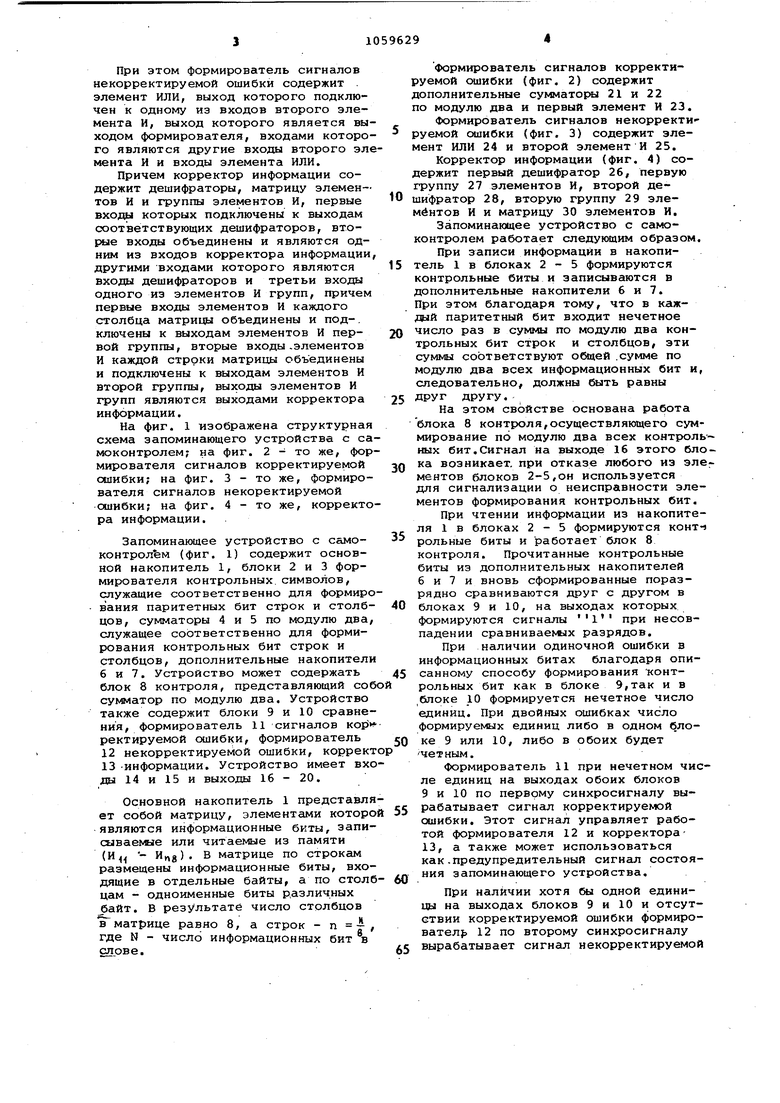

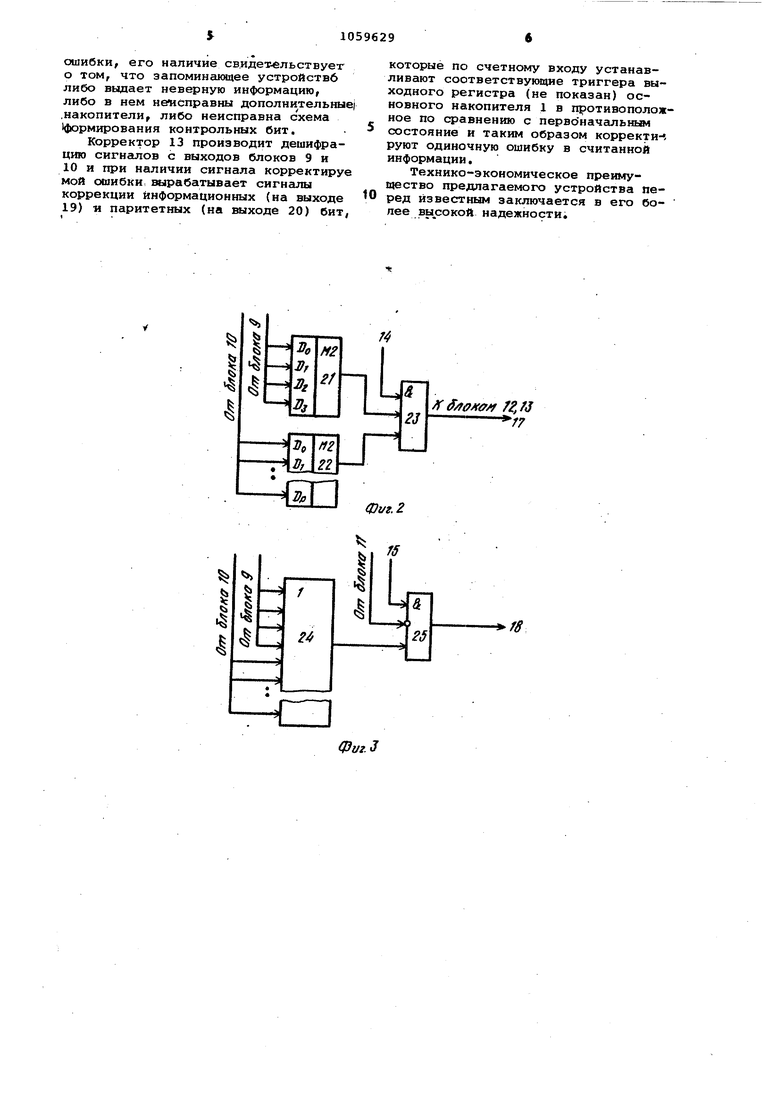

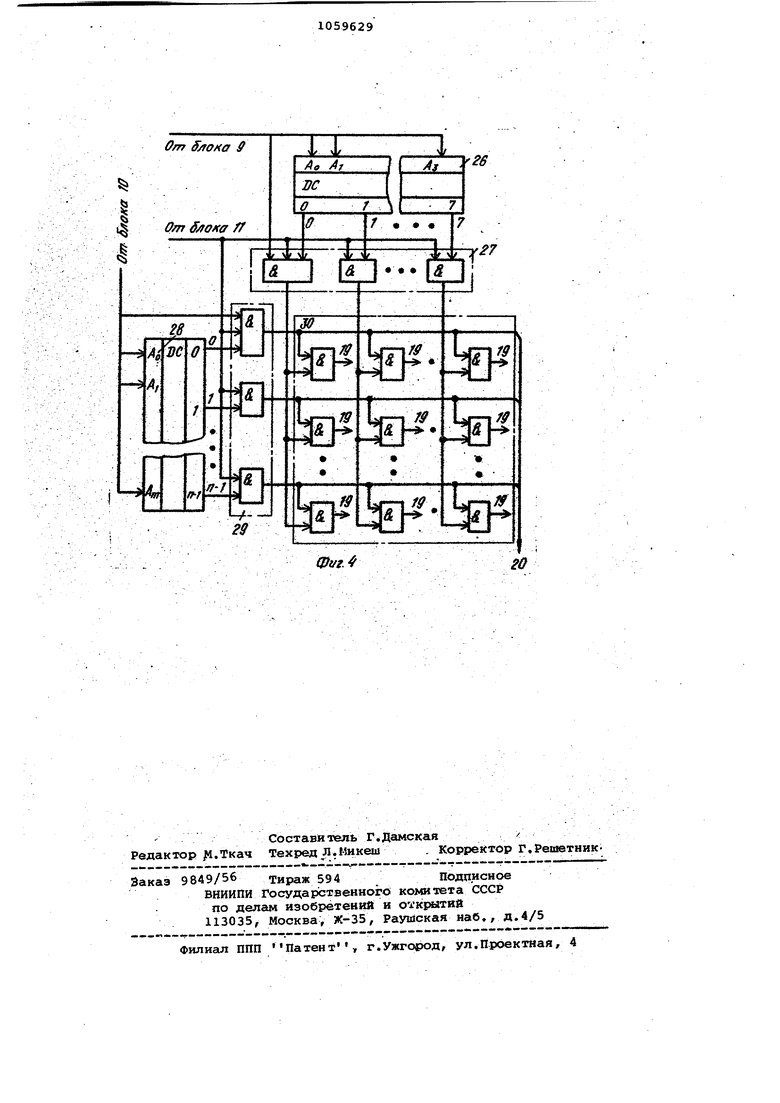

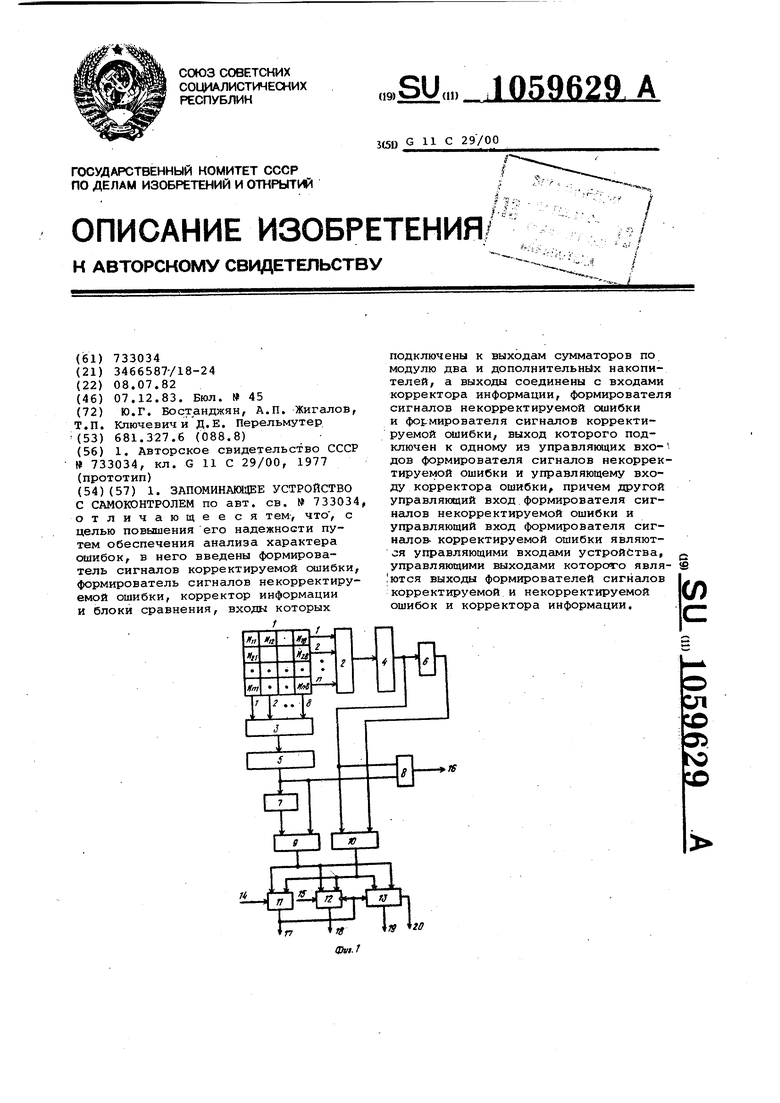

На фиг. 1 изображена структурная схема запоминающего устройства с самоконтролем; на фиг. 2 - то же, формирователя сигналов корректируемой ошибки; на фиг. 3 - то же, формирователя сигналов некоректируемой ошибки; на фиг. 4 - то же, корректора информации.

Запоминающее устройство с самоконтролем (фиг. 1) содержит основной накопитель 1, блоки 2 и 3 формирователя контрольных.символов, служащие соответственно для формирования паритетных бит строк и столбцов, сумматоры 4 и 5 по модулю два, служащее соответственно для формирования контрольных бит строк и столбцов, дополнительные накопители 6 и 7. Устройство может содержать блок 8 контроля, представляющий соб сумматор по модулю два. Устройство также содержит блоки 9 и 10 сравнения, формирователь 11 сигналов кор ректируемой ошибки, формирователь

12некорректируемой ошибки, коррект

13-информации. Устройство имеет входы 14 и 15 и выходы 16-20.

Основной накопитель 1 представляет собой матрицу, элементами которо являются информационные биты, записываемые или читаемые иэ памяти (И - Hug) . В матрице по строкам размещены информационные биты, входящие в отдельные байты, а по столб цам - одноименные биты различных байт. В результате число столбцов

в матрице равно 8, а строк - п - , где N - число информационных бит ®в слове.

формирователь сигналов корректируемой ошибки (фиг. 2) содержит дополнительные сумматорял 21 и 22 по модулю два и первый элемент И 23.

Формирователь сигналов некорректируемой ошибки (фиг. 3) содержит элемент ИЛИ 24 и второй элемент И 25.

Корректор информации (фиг. 4) содержит первый дешифратор 26, первую группу 27 элементов И, второй дешифратор 28, вторую группу 29 элементов И и матрицу 30 элементов И.

Запоминающее устройство с самоконтролем работает следующим образом

При записи информации в накопитель 1 в блоках 2-5 формируются контрольные биты и записываются в дополнительные накопители 6 и 7. При этом благодаря тому, что в каждый паритетный бит входит нечетное число раз в суммы по модулю два контрольных бит строк и столбцов, эти суммы соответствуют общей .сумме по модулю два всех информационных бит и следовательно, должны быть равны друг другу.

На этом свойстве основана работа блока 8 контроля,осуществляющего суммирование по модулю два всех контролных бит.Сигнал На выходе 16 этого блка возникает, при отказе любого из элментов блоков 2-5,он используется для сигнализации о неисправности элементов формирования контрольных бит.

При чтении информации из накопителя 1 в блоках 2-5 формируются конт рольные биты и работает блок 8 контроля. Прочитанные контрольные биты из дополнительных накопителей 6 и 7 и вновь сформированные поразрядно сравниваются друг с другом в блоках 9 и 10, на выходах которых формируются сигналы 1 при несовпадении сравниваемых разрядов.

При наличии одиночной ошибки в информационных битах благодаря описанному способу формирования контрольных бит как в блоке 9,так и в ,блоке 10 формируется нечетное число единиц. При двойных ошибках число формируемых единиц либо в одном блоке 9 или 10, либо в обоих будет Четным.

Формирователь 11 при нечетном числе единиц на выходах обоих блоков 9 и 10 по первому синхросигналу вырабатывает сигнал корректируемой ошибки. Этот сигнал управляет работой формирователя 12 и корректора13, а также может использоваться как.предупредительный сигнал состояния запоминающего устройства.

При наличии хотя бы одной единицы на выходах блоков 9 и 10 и отсутствии корректируемой ошибки формировател г 12 по второму синхросигналу вырабатывает сигнал некорректируемой

ошибки/ его наличие свидетельствует о том, что запоминающее устройствб либо выдает неверную информацию, либо в нем неисправны дополни тельные .накопители, либо неисправна схема 1формирования контрольных бит.

Корректор 13 производит дешифрацию сигнгшов с выходов блоков 9 и 10 и при наличии сигнала корректируе мой ошибки вырабатывает сигналы коррекции информационных (на выходе 19) я паритетных (на выходе 20) бит,

которые по счетному входу устанавливают соответствующие триггера выходного регистра (не показан) основного накопителя 1 в противоположное по сравнению с первоначальным состояние и таким образом корректи- руют одиночную ошибку в считанной информации.

Технико-экономическое преимуBjecTBO предлагаемого устройства перед известным заключается в его бопее вьлсокой надежности.

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU733034A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-12-07—Публикация

1982-07-08—Подача