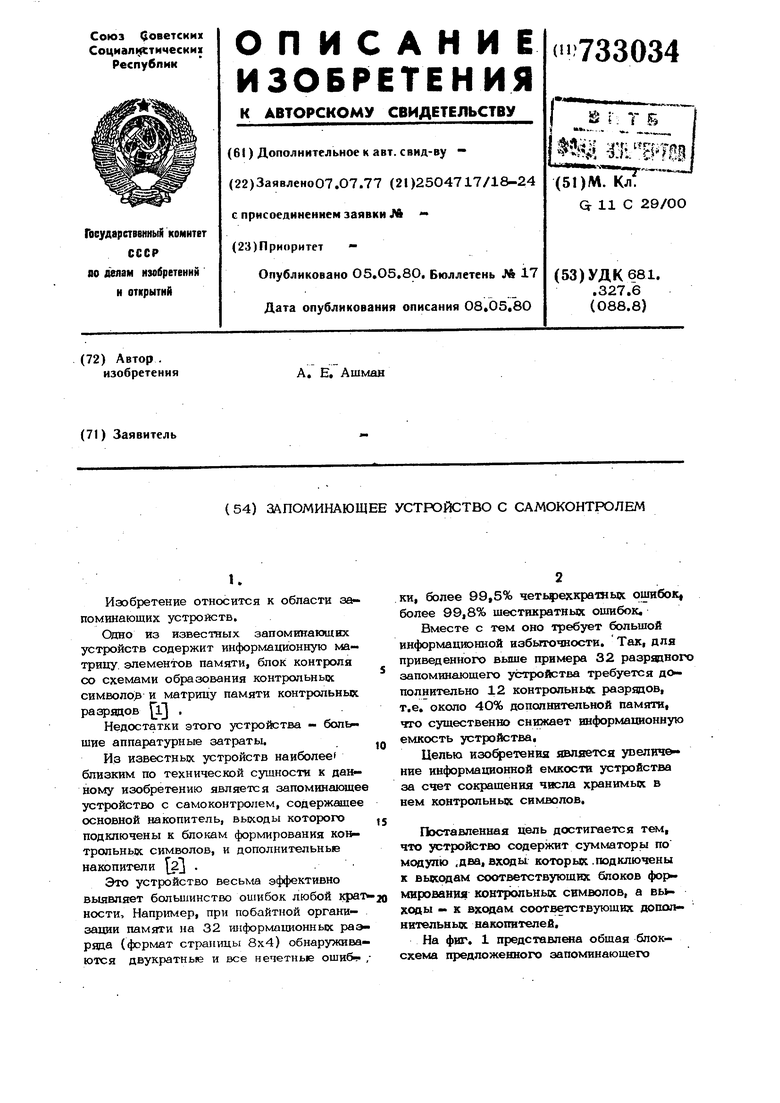

Изобретение относится к области запоминающих устройств. Одно из HaBecTObix запоминающих устройств содержит информационную матрицу, элементов памяти, блок контроля со схемами образования контрольных символов и матрицу памяти контрольных разрядов 1 . Недостатки этого устройства - большие аппаратурные затраты. Из известных устройств наиболее близким по технической сущности к да№ному изобретению является запоминающее устройство с самоконтролем, содержащее основной накопитель, выходы которого подключены к блокам формирования контрольньк символов, и дополнительные накопители 2 .. Это устройство весьма эффективно выявляет большинство ошибок любой крат кости. Например, при побайтной организации памяти на 32 информационных разряда (формат страницы 8x4) обнаруживаются двукратнью и все нечетные оший КИ| более 99,5% четырехкратных ошибок, более 99,8% щестикратных ошибок. Вместе с тем оно требует большой информационной избыточности. Так, для приведенного вьпие примера 32 разрядного запоминающего устройства требуется дсь. полнительно 12 контрольных разрядов, т.е. около 40% дополнительной памяти, что существенно снюкает информационную емкость устройства. Целью изофетения является упелич&« ние информационной емкости устройства за счет сокращения числа хранимых в нем контрольных символов. Поставленная цель достигается тем, что устройство содержит сумматоры по моцупю ,два, входы которьк .подключены к вьксщам соответствующих блоков формирования контрольных символов, а выходы - к входам соответствующих дополнительных накопителей. На фиг. 1 представлена общая блоксхема предложенного запоминающего

устройства; на фиг. 2 - пример его конкретного исполнения

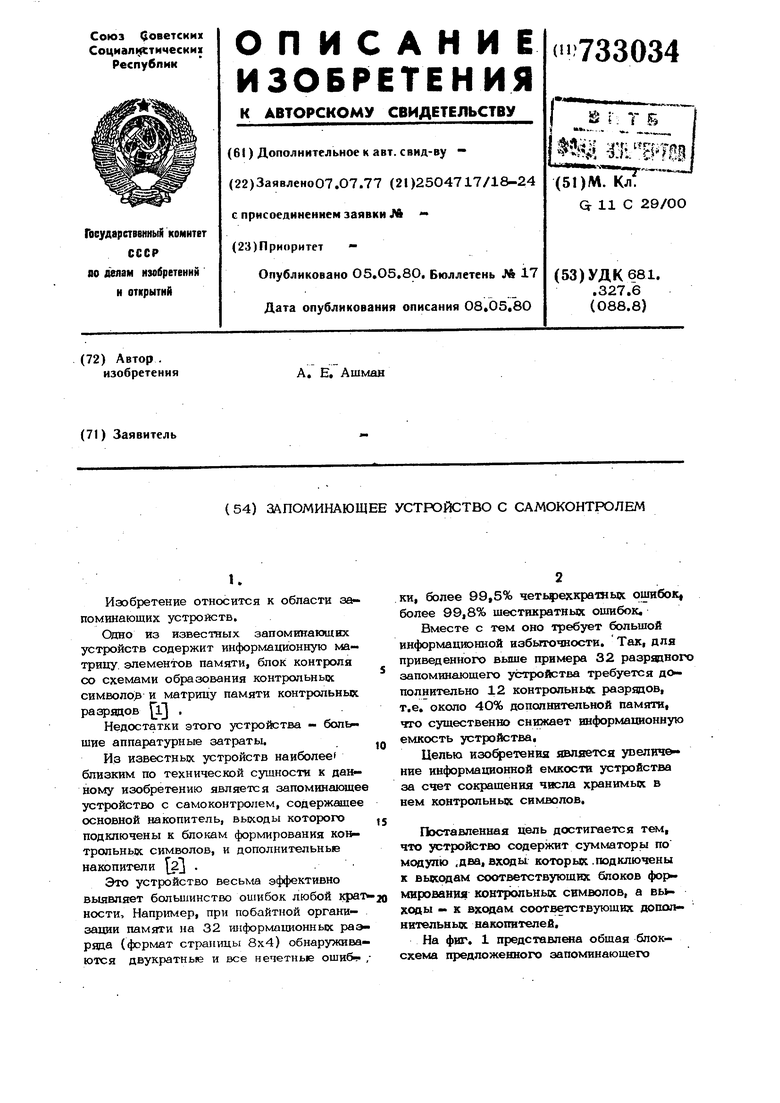

Устройство (см. фиг, 1) содержит накопитель 1, каждое слово которого представляет собой страницу (таблицу) из П строк и п столбцов запоминающих элементов, хранящих-IT информационных символов.

w4

. Выходы накопителя 1, соответствующие выходам У| и ( таблицы по строкам и столбцам, подключены к входам блоков 2 и 3 формирователя контрольных символов, например (ct.}н W .

Выходы блоков 2, в свою очередь, подключены ко входам сумматоров 4 по модулю два, а выходы этих сумматоров подключены ко входам дополнительного накопителя 5, хранящего контрольные разряды А )строко

Аналогичным образом в устройство могут быть введены сумматоры 6 по модулю два, включаемые между блоками 3 и дополнительным накопителем 7, слу жащим для хранения контрольных дов I столбцов.

Число сумматоров 4 определяется выражением г j ogg сумматоров 6 - выражедием

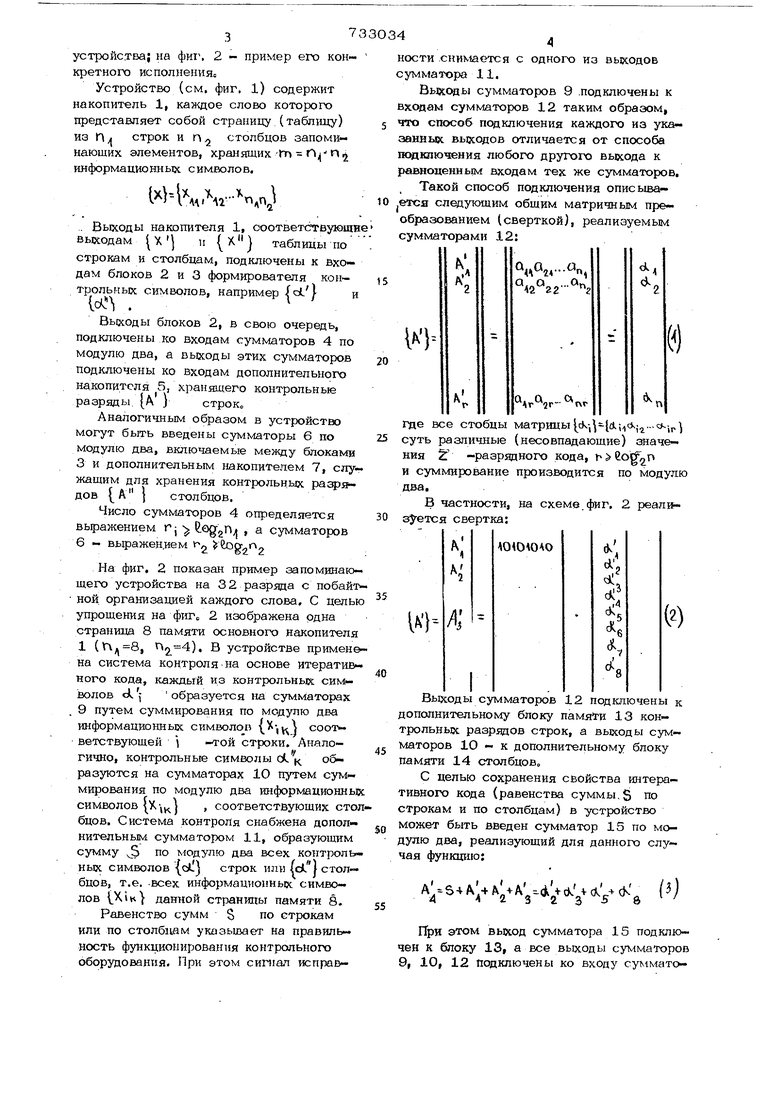

На фиг. 2 показан пример запоминающего устройства на 3 2 разряда с побайт ной организацией каждого слова, С целью упрощения на фиг 2 изображена одна страница 8 памяти основного накопителя 1 (, ). В устройстве применена система контроля на основе итеративного кода, каждый из контрольных сим образуется на сумматорах

ВОЛОВ

9 путем суммирования по модулю два информационных символов соот ветствующей -той строки. Аналогично, контрольные символы dL | образуются на сумматорах 10 путем суммирования по модулю два информационных символов У.1к соответствующих столбцов. Система контроля снабжена дополнительным сумматором 11, образующим сумму S по модулю два всех контрольных символов {oil строк или (ci. столбцов, т.е. -всех информационных символов (Xin} данной страницы памяти 8.

Равенство сумм S по строкам или по столбцам указывает на правильность функционирования контрольного оборудования. При этом сишат исправности снимается с одного из вькодов сумматора 11.

Вьвсоды сумматоров 9 .подключены к входам сумматоров 12 таким образом, что стюсоб подключения каждого из указанных, выходов отличается от способа подключения любого другого выхода к равноценнь1М входам тех же сумматоров.

Такой способ подключения описыва ется следующим общим матричным преобразованием (сверткой), реализуемым сумматорами 12:

кИ

IA

л

Где все стобцы матрицы ,- diiickj...cs-,p суть различные (несовпадающие) значения 2f -разрядного кода, и суммирование производится по модулю два,

В частности, на схеме.фиг. 2 реал зуется свертка:

ЮШЮАО

1

;

N

13

г4

()

Л

s.

Выходы сумматоров 12 подключены к дополнительному блоку памяги 13 контрольных разрядов строк, а выходы сумматоров 10 - к дополнительному блоку памяти 14 столбцов,

С целью сохранения свойства интеративного кода (равенства суммы, S по строкам и по столбцам) в устройство может быть введен сумматор 15 по модулю два, реализующий для данного случая функцию:

А;.54л;4лЧА;- ч.(к; (з)

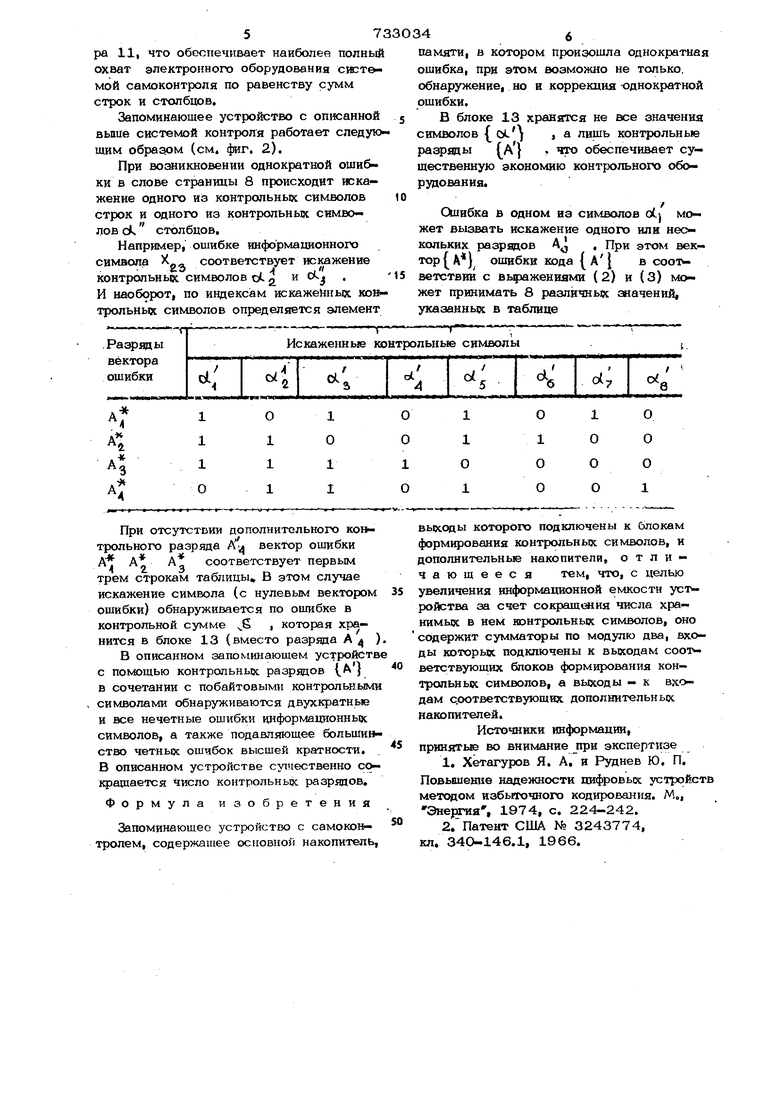

При этом выход сумматора 15 подключен к блоку 13, а все выходы сумматоров 9, 10, 12 подключены ко входу сумматоpa 11, что обеспечивает наиболее полный охват электронного оборудования системой самоконтроля по равенству сумм строк и столбцов. Запоминающее устройство с описанной Bbuue системой контроля работает следующим образом (см. фиг. 2). При возникновении однократной оши&ки в слове страницы 8 происходит искажение одного из контрольных символов строк и одного из контрольных символов ck столбцов. Например, ошибке информационного символа X соответствует искажение контрольных символов Ы 2 и c-j . И наоборот, по индексам искаженных контрольных символов определяется элемент памяти, в котором произошла однократная ощибка, при этом возможно не только, обнаружение, но и коррекция юднократной рщибки. В блоке 13 хранятся не все значения символов {OL , а лишь контрольные разряды А} . что обеспечивает существенную экономию контрольного оборудования. Оиибка в одном из символов oCj может вызвать искажение одного или нескольких разрядов А , При этом вектор ( А) оивдбки кода ( А | в cooiw ветствии с вьфажениями (2) и (3) может принимать 8 различных значений, указанньк в таблице

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059629A2 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Постоянное запоминающее устройство с самоконтролем | 1988 |

|

SU1532979A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1322379A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1005193A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

При отсутствии дополнительного контрольного разряда A.I вектор ошибки А А А соответствует первым трем строкам таблицы В этом случае искажение символа (с нулевым вектором ошибки) обнаруживается по ошибке в контрольной сумме 6 , которая хранится в блоке 13 (вместо разряда А j В описанном запоминающем устройств с помощью контрольных разрядов } в сочетании с побайтовыми контрольными символами обнаруживаются двухкратные и все нечетные ошибки информационных символов, а также подавляющее большин ство четных ошибок высшей кратности, В описанном устройстве существенно с кращается число контрольных разрадов. Формула изобретения Запоминающее устройство с самоконтролем, содержащее сю 1ов}юй накопитель, выходы которого подключены к блокам формирования контрольных символов, и дополнительные накопители, отличающееся тем, что, с целью увеличения информационной емкости устройства за счет сокращения числа хранимых в нем {вонтрольных символов, оно сумматоры по модулю два, входы моторьк подключены к выходам соответствующих блоков формирования контрольньк символов, а выходы - к соответствующих дополнительных накопителей. Источники информации, принятые во внимание при экспертизе 1.Хетагуров Я, А, н Руднев Ю, П, noBbEuemie надежности цифровых устройств методом избыточного кодирования, М„ Эне ягна, 1974, с, 224-242, 2.Патент США № 3243774, кл. 340-146,1, 1966,

Авторы

Даты

1980-05-05—Публикация

1977-07-07—Подача