Изобретение относится к вычислительной технике и может быть использовано для цифровой обработки сигналов в радиосвязи и автоматике.

Известен цифровой фильтр, реализующий систему разностных уровней вида:

Fi=Xi+aiFi-1+ a2Fi-2

yi=b0Fi+b1Fi-1+b2Fi-2 (1)

где Xi, yi входной и выходной сигналы устройства в i-м такте,

Fi промежуточная переменная в i-м такте,

а1, а2, b0, b1, b2 постоянные коэффициенты [1]

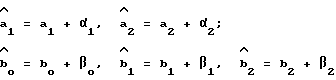

Недостатком известного устройства является наличие вычислительной погрешности, указанная погрешность включает в себя две составляющие. Первая из них обусловлена округлением постоянных коэффициентов. Коэффициенты, как правило, являются дробными числами. При их представлении в двоичном коде получаются бесконечные двоичные дроби. Для размещения в регистрах дроби требуют округления, при котором происходит искажение значений коэффициента. В результате вместо точных значений а1, а2, b0, b1, b2 в вычислениях используются приближенные значения коэффициентов  отличающиеся от точных на величины ошибок округления α1, α2, βo, β1, β2,

отличающиеся от точных на величины ошибок округления α1, α2, βo, β1, β2,

Вторая составляющая обусловлена округлением произведений промежуточных переменных на постоянные коэффициенты, что приводит к появлению погрешностей А1i, A2i, B0i, B1i, B2i.

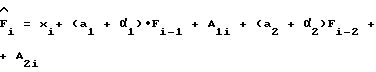

В результате в каждом такте работы цифрового фильтра формируется промежуточная переменная:

с ошибкой

ΔFi = α1Fi-1 + α2Fi-2 + A1i + A2i,

что приводит к появлению погрешности выходного сигнала yi.

Наиболее близким аналогом является цифровой фильтр, содержащий последовательно соединенные тактовый генератор, первый и второй регистры сдвига, второй умножитель, первый сумматор. выход которого подключен к второму входу первого регистра сдвига, третий умножитель и второй сумматор, к второму входу которого и второму входу первого сумматора подключен соответственно через четвертый умножитель и первый умножитель выход первого регистра сдвига, а выход второго регистра сдвига, к тактовому входу которого подключен выход тактового генератора, подключен через пятый умножитель к третьему входу второго сумматора, N блоков коррекции, к тактовому входу каждого из которых подключен выход тактового генератора, а к первому и второму входам первого блока коррекции подключены выходы первого и второго умножителей, выход первого блока коррекции подключен к четвертому входу входного сумматора, а выход каждого (i+1)-го блока коррекции подключен к третьему входу i-го блока коррекции, при этом каждый из N блоков коррекции содержит последовательно соединенные входной суматор, выход которого подключен к входу блока округления, первый регистр сдвига, выход которого через второй умножитель подключен к третьему входу входного сумматора, второй регистр сдвига и первый умножитель, выход которого подключен к четвертому входу входного сумматора, первый второй и пятый входы входного сумматора первого блока коррекции являются первым, вторым и третьим входами блока коррекции, выходом которого является выход блока округления, а тактовым входом блоков коррекции являются вторые входы первого и второго регистров сдвига каждого блока коррекции, выходом (i+1)-го блока коррекции является выход блока округления (i+1)-го блока коррекции, первый и второй входы (i+1)-го блока коррекции соединены соответственно с выходами первого и второго умножителей i-го блока коррекции [2]

Известное устройство позволяет с помощью блоков коррекции сформировать корректирующий сигнал для компенсации ошибок округления произведений промежуточных переменных на постоянные коэффициенты а1 и а2 и устранения их накопления. Однако при этом не учитывается составляющая результирующей погрешности, обусловленная определением постоянных коэффициентов. Ошибки α1Fi-1 и α2Fi-2 циркулируют в петле обратной связи и не компенсируются. Они могут накапливаться, существенно снижая точностные характеристики цифрового фильтра. Поэтому целесообразно в корректирующий сигнал ввести составляющую, компенсирующую погрешности округления постоянных коэффициентов.

Технический результат повышение точности цифровой фильтрации за счет исключения накопления погрешностей, обусловленных округлением постоянных коэффициентов.

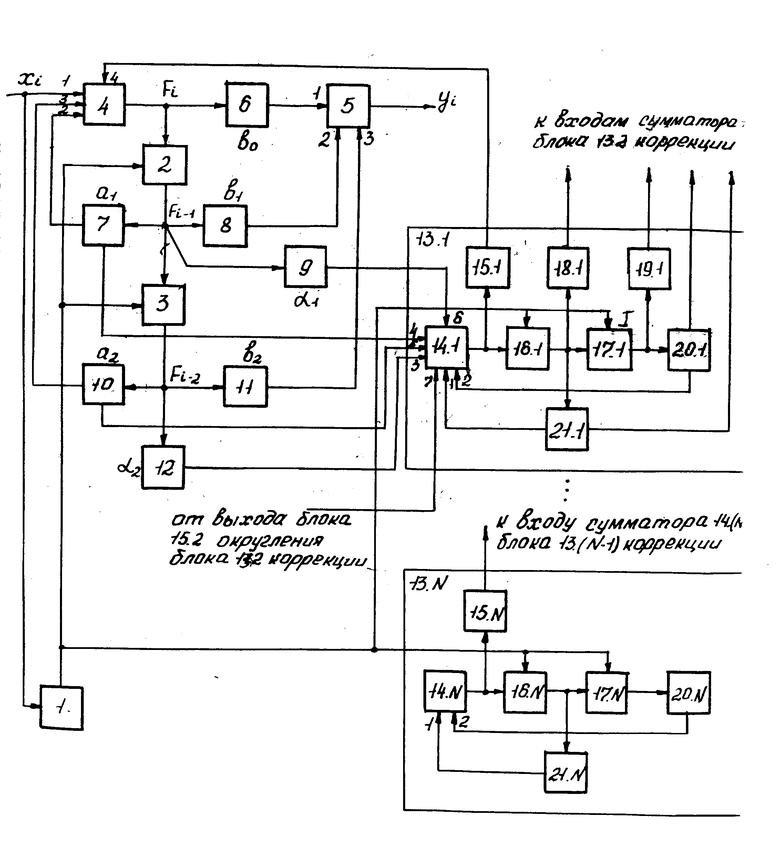

На чертеже представлена структурная электрическая схема цифрового фильтра.

Цифровой фильтр содержит тактовый генератор 1, первый и второй регистры сдвига 2, 3, первый и второй сумматоры 4, 5, первый, второй, третий, четвертый, пятый, шестой и седьмой умножители 6-12 и N блоков коррекции 13.1-13. N, каждый из N-1 блоков коррекции содержит входной сумматор 14, блок 15 округления, первый и второй регистры сдвига 16, 17, первый, второй, третий и четвертый умножители 18-21, блок коррекции содержит входной сумматор, 14, блок 15 округления, первый и второй регистры сдвига 16, 17 третий и четвертый умножители 20, 21.

Цифровой фильтр работает следующим образом.

Входной сигнал Xi в виде последовательности отсчетов, представленных в цифровой форме и следующих с периодом дискредитации То, поступает на вход звена второго порядка (первый вход сумматора 4), а также на вход тактового генератора 1 для формирования управляющего импульса. В цифровом фильтре, построенном на блоках 1-8, 10-11, производится формирование выходного сигнала в соответствии с системой уравнений (1).

Для компенсации вычислительной погрешности фильтра, обусловленной округлении коэффициентов и промежуточных результатов вычисления, в блоках 13.1-13N производится формирование корректирующего сигнала. Во входной сумматор 14.1 в каждом i-м тактовом интервале вводятся сигналы A1i, A2i ошибки округления произведений, формируемые на дополнительных выходах умножителей 7 и 10, а также сигналы α1Fi-1 и α2Fi-2 формируемые на выходах умножителей 9 и 12. Таким образом, на вход цифрового звена 13.1 поступает сигнал ΔFi, равный погрешности формирования и промежуточной переменной Fi.

Поскольку цифровое звено (блоки 14.1, 16.1, 17.1, 20.1 и 21.1) в составе первого блока 13.1 коррекции функции низшей в соответствии с первым уравнением системы (1), при отсутствии округления в умножителях 20.1 и 21.1 и точном представлении коэффициентов а1 и а2 сигнал на выходе входного сумматора 14.1 в каждом такте в точности повторяет сигнал ошибки, накопленной к данному такту в основном звене второго порядка. Если этот сигнал в каждом такте вводить в сумматор 4, то можно добиться полной компенсации ошибок, обусловленных округлением коэффициентов а1 и а2 и произведений в умножителях 7 и 10. Однако, чтобы избежать наращивания разрядности отсчетов, циркулирующих по петле обратной связи через умножители 7 и 10, выходной сигнал сумматора 14.1 необходимо предварительно округлить с точностью до младшего разряда отсчетов Fi, что и производится в блоке 15.1 округления.

Блок 13.1 коррекции содержит точно такие цепи обратной связи (через умножители 20.1 и 21.1), какие входят с состав основного звена, а умножение производится на коэффициенты а1 и а2. Поэтому для сохранения постоянной разрядности отсчетов в процессе работы в умножителях 20.1 и 21.1 необходимо производить округления результатов умножений, а в качестве постоянных коэффициентов использовать округленные значения  При этом также может иметь место накопление ошибок округления, которые имеют уже гораздо меньшее значения.

При этом также может иметь место накопление ошибок округления, которые имеют уже гораздо меньшее значения.

Для повышения точности вычислений за счет компенсации ошибок округления, возникающих уже в блоке 13.1, в состав цифрового фильтра может быть введен точно такой же блок 13.2, на вход которого в каждом такте необходимо подавать сигналы ошибок округления от умножителей 20.1 и 21.1 и ошибок, обусловленных округлением коэффициентов, от умножителей 18.1 и 19.1. В блоке формируется корректирующий сигнал, который вводится в сумматор 14.1, т. е. блок 13.2 по отношению к блоку 13.1 коррекции выполняют те же функции, что и блок 13.1 по отношению к основному звену второго порядка.

Компенсация ошибок округления, возникающих в блоке 13.2 коррекции, может быть аналогично осуществлена следующим блоком 13.3 коррекции и т. д. В общем случае в устройстве может быть N блоков коррекции, число которых определяется требованиями точности вычислений и зависит от того, насколько велика может оказаться ошибка округления, накопленная в основном звене при данных постоянных коэффициентов а1 и а2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1988 |

|

SU1566471A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1989 |

|

SU1619299A1 |

| Устройство для умножения на постоянную величину | 1989 |

|

SU1594528A1 |

| Цифровой фильтр | 1975 |

|

SU590749A1 |

| Устройство для исправления ошибок в избыточном коде | 1988 |

|

SU1582356A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1241258A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1721610A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1654835A1 |

Способ относится к вычислительной технике и может быть использован для цифровой обработки сигналов в радиосвязи и автоматике. Технический результат - повышение точности цифровой фильтрации за счет исключения накопления погрешностей, обусловленных округлением постоянных коэффициентов. Сущность способа заключается в том, что в корректирующий сигнал дополнительно вводится составляющая, обусловленная округлением постоянных коэффициентов путем умножения промежуточной переменной на величину ошибки округления каждого коэффициента. Цифровой фильтр содержит штанговый генератор 1, регистры сдвига 2, 3 сумматоры 4, 5 умножители 6-12, N блоков коррекции 13.1-13N,входной сумматор 14, блок 15 округления, умножители 18-21. 1 ил.

Цифровой фильтр, содержащий первый и второй регистры сдвига, первый и второй сумматоры, первый, второй, третий, четвертый и пятый умножители, N блоков коррекции, где N 1, 2, 3, и тактовый генератор, вход которого подключен к входу первого сумматора, выход тактового генератора подключен к тактовым входам N блоков коррекции и тактовым входам первого и второго регистров сдвига, при этом выход первого регистра сдвига подключен к входу второго регистра сдвига через первый умножитель к второму входу первого сумматора, к третьему входу которого через второй умножитель подключен выход второго регистра сдвига, причем выходы первого и второго регистров сдвига подключены соответственно через четвертый и пятый умножители к второму и третьему входам второго сумматора, вторые выходы первого и второго умножителей подключены соответственно к первому и второму входам первого блока коррекции, выход которого подключен к четвертому входу первого сумматора, а выход каждого (i + 1)-го, где i 1, 2, N-1, блока коррекции подключен к третьему входу i-го блока коррекции, при этом каждый из N блоков коррекции содержит последовательно соединенные входной сумматор, первый регистр сдвига, второй регистр сдвига и первый умножитель, а также второй умножитель и блок округления, к входу которого подключен выход входного сумматора, первый, второй и пятый входы которого являются соответственно первым, вторым и третьим входами первого блока коррекции, выходом которого является выход блока округления, а к третьему и четвертому входам входного сумматора подключены первые выходы соответственно второго и первого умножителей, причем тактовым входом каждого блока коррекции являются вторые входы первого и второго регистров сдвига каждого блока коррекции, выходом (i + 1)-го блока коррекции является выход блока округления (i + 1)-го блока коррекции, к первому и второму входам которого подключены вторые выходы первого и второго умножителей i-го блока коррекции, отличающийся тем, что введены шестой и седьмой умножители, при этом выходы первого и второго регистров сдвига соответственно через шестой и седьмой умножители подключены к четвертому и пятому входам первого блока коррекции, а в каждый i-й блок коррекции введены третий и четвертый умножители, к входам которых подключены выходы соответственно первого и второго регистров сдвига, а выходы третьего и четвертого умножителей i-го блока коррекции подключены соответственно к шестому и седьмому входам входного сумматора (i + 1)-го блока коррекции.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Введение в цифровую фильтрацию /Под ред | |||

| Боднера Р | |||

| и Констрантинидиниса А | |||

| - М.: Мир, 1876, с | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, авторское свидетельство, 1566471, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1997-11-20—Публикация

1993-05-26—Подача