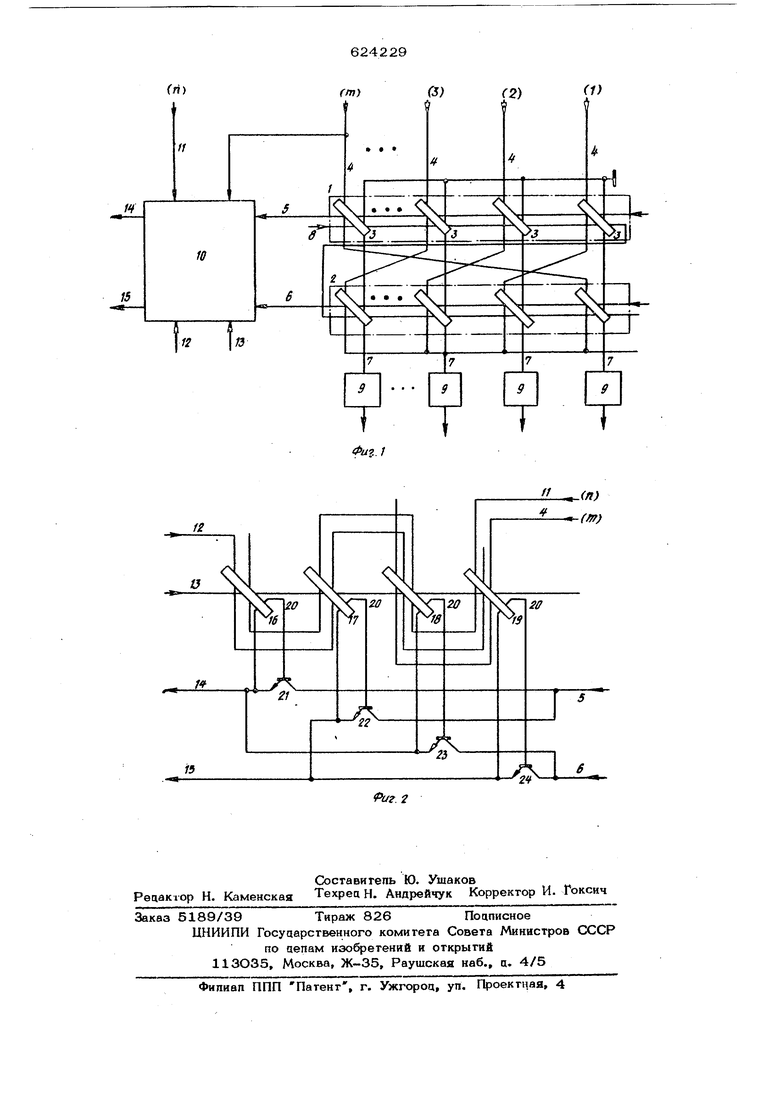

3 .6242 принципиапьная схема уапа коммутации. Бпок содержит цва Ш - разрядных регистра 1 и 2, соцержащих магнитные серцеч- НИКИ 3, гце П - основание системы счис пения, входные шины 4, шины переноса 5 и 6, Быхоцные шины 7 и шину сброса 8. Выходные шины 7 соецииены со входами выходных усипигепей 9. Кроме того, блок содержит узеп коммутации 1О, выходы которого подключены к шине поразрядного переноса 11, к одной из входных шин 4 - к шине старшей цифры Ш, к шине установки 12 и считывания 13, а также к шинам переноса 5 и 6 регистров 1 и 2. Выходы узпа коммутации соединены с выходными шинами 14 и 15 переноса в спе цуюший разряд. Уаеп коммутации содержит четыре маг гитных сердечника 16.17, 18, 19, прошитых кроме перечисленных шин, обмотка ми управпения; 2О, которые подключены к эмиттерам и базам соответствуюшик транзисторов 21, 22, 23 и 24. Работает устройство следующим образом. В первом такте на входные шины 4 с одного из разрядов матричного сумматора поступает код поразрядной суммы в коде (1) из (t1). При этом;, в pei-истры 1 и 2 записывается вход поразрядной суммы и суммы, увеличенной на единицу, соответственно. В этомже гакте осуществляется подача сигналов П() и W (старшая цифра) fia узеп коммутации Ю, гае происхоцит вычисление функций И, П, ПУШ и nVrti, определяющих условие распространения переноса. Во втором такте происходит распространение переноса и считывание окончательной суммы с одного из регистров 1 или 2 током по шинам 5 или 6. Номер считываемого регистра в следующем разряде определяется условиями переноса в данном разряде, т.е. насыщением одного из аранзнсторов 21, 22, 23 или 24. Таким образом, происходит быстрое распространение ,переноса вовсех разрядах. В третьем такте цепь пере носа Бозврашается в исходное состояние токами в шинах 8 и 12. Работа цепи переноса согласуется с работой трехтактной матрицы сумматора, имеющей циклы: прие первого операнда, прием второгх операнда - выдача поразрядной суммы, возврат. Таким образом, за счет введения в бпок двух регистров и узпа коммутации удается повысить :его быстродействие. Формула изобретения 1. Блок переноса для матричного сум,матора, содержащий элементы памяти на магнитных сердечниках, прошитых входными и выходными шинами, шиной сброса и поразрядного переноса, выходные усилители, подключенные к выходным шинам, отличающийся тем, что с целью повышения быстродействия блока, он содержит два rrt-разрядных регистра на магнитнрлх сердечниках, прошитых шинами переноса, и узел коммутации, первый вхоц которого соединен с шиной поразрядного переноса, второй вход - с соответствующей входной шиной, третий вход - с шиной переноса первого регистра, четвертый вход - с шиной переноса второго регистра, причем магнитный сердечник первого ред истра и ( i + 1) -и магнитный сердеч-. ник второго регистра прошиты i -и входной шиной, а m-и магнитный сердечник первого регистра и первый магнитный сердечник второго регистра прошиты Kff-и входной шиЕюй, где - номер разряда регистра. 2. Бпок переноса для матричного сумматора по п. 1, отличающийся тем, что узеп коммутации содержит четыре транзистора к четыре магнитных сердечника, прошитых шинами установки, считывания поразрядного переноса записи и обмотками управления, копПекторы первого и второго транзисторов соединены с четвертым входом узпа коммутации, коппекторы третьего и четвертого транзисгоров - с третьим входом, база и эмиггеры транзисторов соединены с соответствующими обмотками управления, соответствук щие концы которых подключены к выхоцам узла коммутации. Источники информации, принятые во внимание при экспертизе: 1.Авторское свицетепьство СССР № 432495, кп. Q,O6 Р 7/5О, 1972. 2.Авторское свиаетепьство СССР № 434412, кп, Q Об Р 7/5О, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок переноса для матричного сумматора | 1982 |

|

SU1061135A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Логическое запоминающее устройство | 1977 |

|

SU710041A1 |

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

Авторы

Даты

1978-09-15—Публикация

1976-01-16—Подача