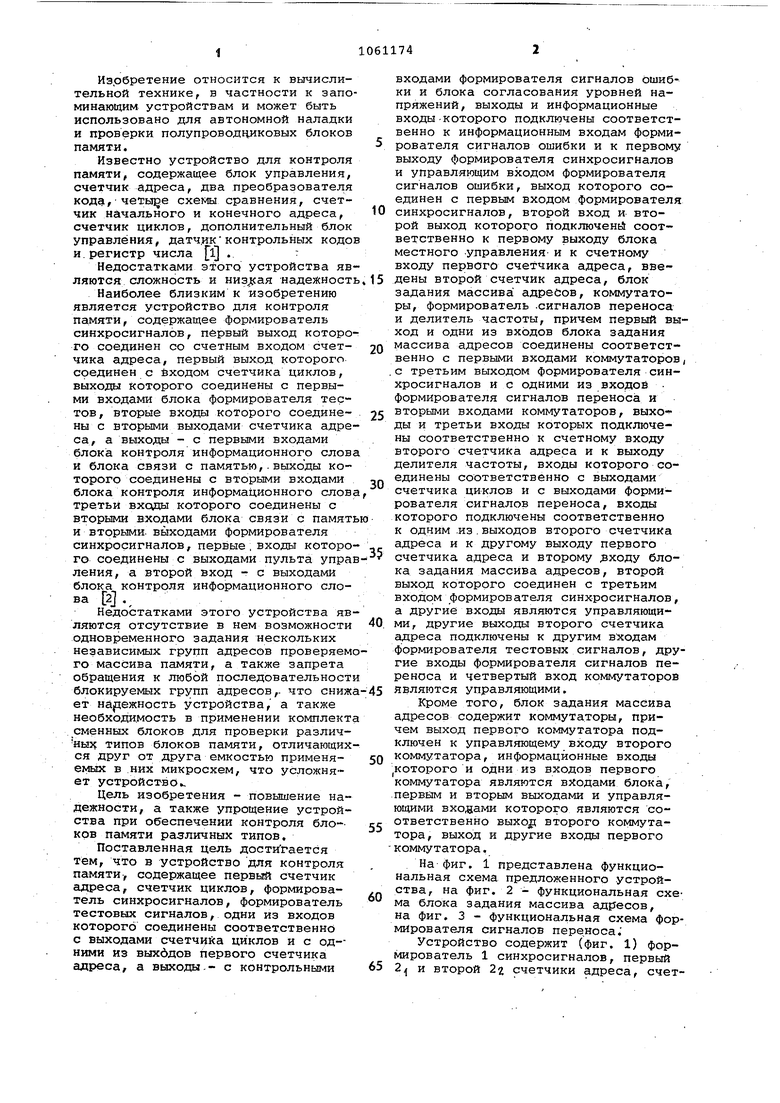

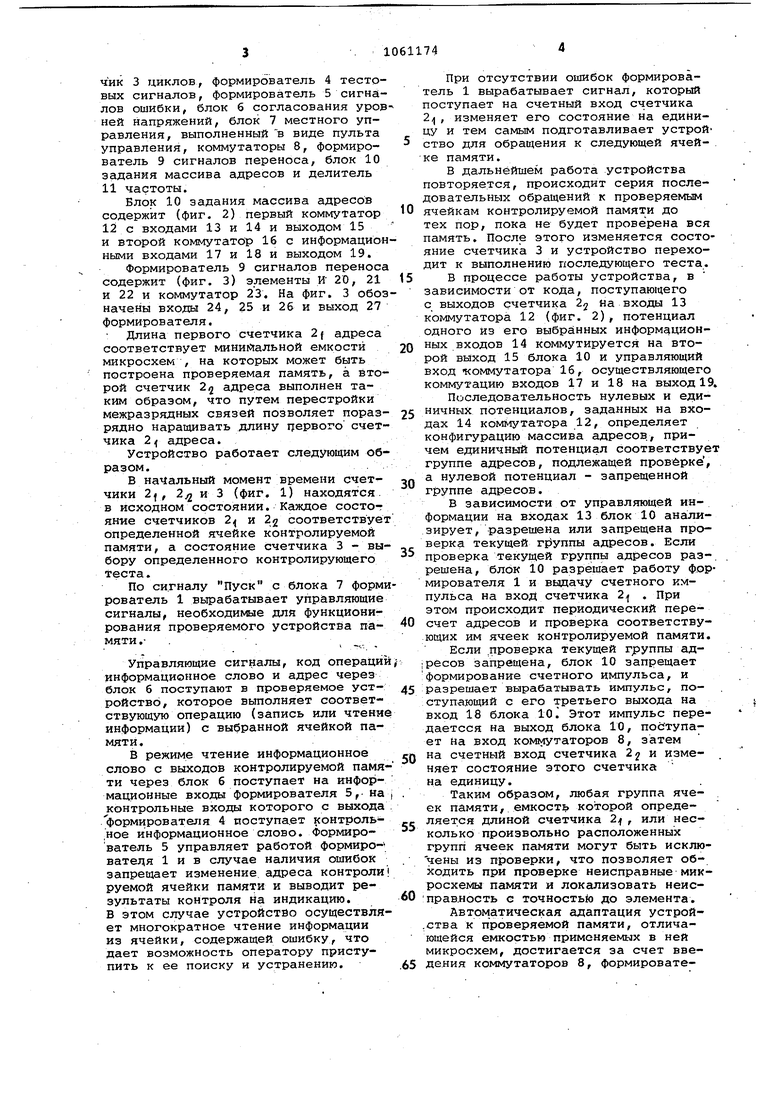

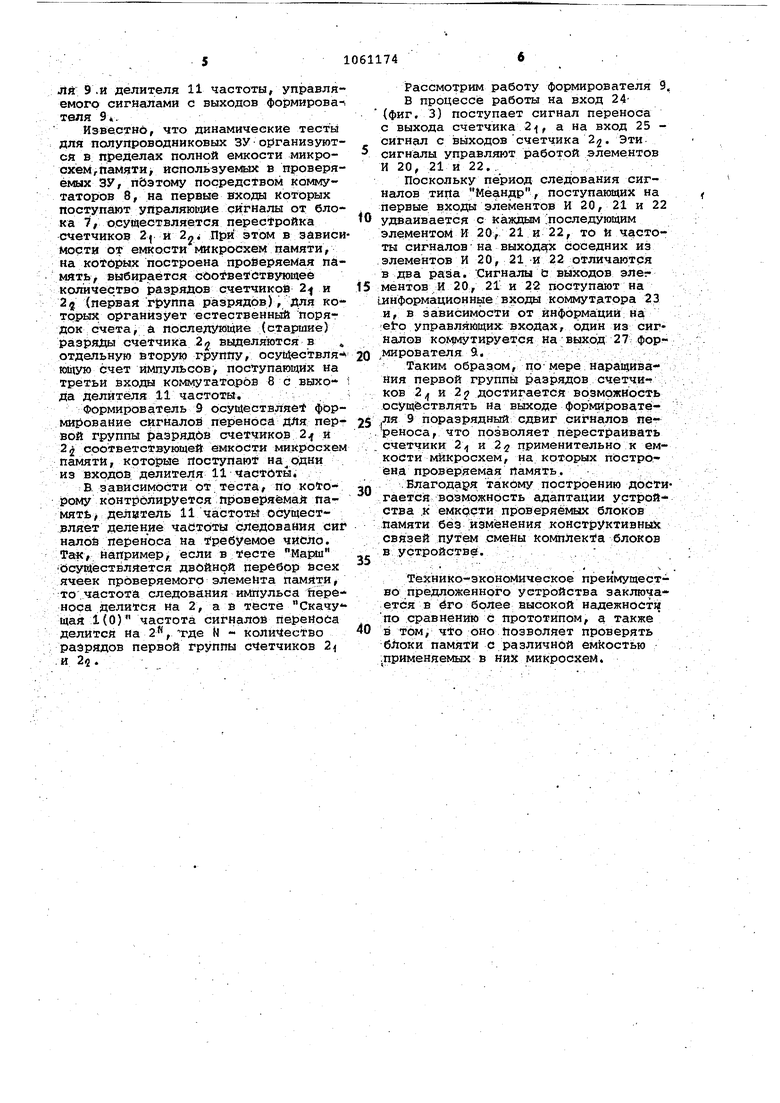

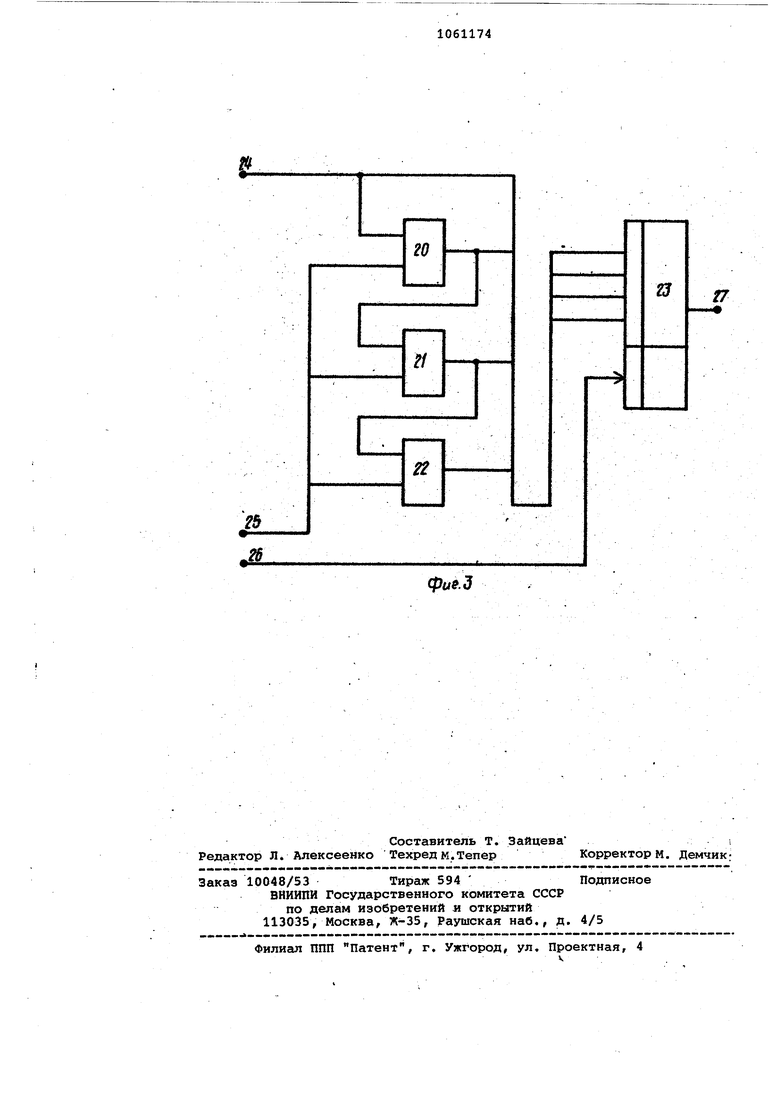

Изобретение относится к вычислительной технике, в частности к запо минающим устройствам и может быть использовано для автономной наладки и проверки полупроводниковых блоков памяти. Известно устройство для контроля памяти, содержащее блок управления, счетчик адреса, два преобразователя кода,-четыре схемы сравнения, счетчик начального и конечного адреса, счетчик циклов, дополнительный блок управления, датчикконтрольных кодо и. регистр числа l . Недостатками этого устройства яв ляются сложность и надежност Наиболее близким к изобретению является устройство для контроля памяти, содержащее формирователь синхросигналов, первый выход которо го соединен со счетным входом счетчика адреса, первый выход которого соединен с йходом счетчика циклов, выходы которого соединены с первыми входами блока формирователя тестов, вторые входы которого соединены с вторыми выходами счетчика адре са, а выходы - с первыми входами блока контроля информационного слов и блока связи с памятью,.выходы которого соединены с вторыми входами блока контроля информационного слов Тре:тьй входы которого соединены с вторыми входами блока связи с памят и вторыми, выходами формирователя синхросигналов, первые,входы которо го соединены с выходами пульта упра Ленин, а второй вход - с выходами блока контроля информационного спова 2J . Недостатками этого устройства яв ляются отсутствие в нем возможности одновременного задания нескольких независимых групп адресов проверяем го массива памяти, а также запрета обращения к любой последовательност блокируемых групп адресов,- что сниж ет надежность устройства, а также необходимость в применении комплект сменных блоков для проверки различных типов блоков памяти, отличающих ся друг от друга емкостью применяемык в них микросхем, что усложняет устройство. Цель изобретения - повышение надежности, а также упрощение устройства при обеспечении контроля бло-ков памяти различных типов. Поставленная цель достигается тем, что в устройство для контроля памяти-, содержащее первьгй счетчик адреса, счетчик циклов, формирователь синхросигналов, формирователь тестовых сигналов, одни из входов которого соединены соответственно с выходами счетчийа циклов и с од-ними из выхддов первого счетчика адреса, а выходы.- с контрольными входами формирователя сигналов ошибки и блока согласования уровней напряжений, выходы и информационные входы-которого подключены соответственно к информационным входам формирователя сигналов ошибки и к первому выходу формирователя синхросигналов и управляющим входом формирователя сигналов ошибки, выход которого соединен с первым входом формирователя синхросигналов, второй вход и второй выход которого подключен соответственно к первому выходу блока местного -управления- и к счетному входу первого счетчика адреса, введены второй счетчик адреса, блок задания массива адресов, коммутаторы, формирователь .сигналов переноса и делитель частоты, причем первый выход и одни из входов блока задания массива адресов соединены соответственно с первыми входами коммутаторов, с третьим выходом формирователя синхросигналов и с одними из входов формирователя сигналов переноса и вторыми входами коммутаторов, выходы и третьи входы которых подключены соответственно к счетному входу второго счетчика адреса и к выходу делителя частоты, входы которого соединены соответственно с выходами счетчика циклов и с выходами формирователя сигналов переноса, входы которого подключены соответственно к одним .из.выходов второго счетчика адреса и к другому выходу первого счетчика адреса и второму эходу блока задания массива адресов, второй выход которого соединен с третьим входом формирователя синхросигналов, а другие входы являются управляющими, другие выходы второго счетчика адреса подключены к другим входам формирователя тестовых сигналов, другие входы формирователя сигналов переноса и четвертый вход коммутаторов являются управляющими. Кроме того, блок задания массива адресов содержит коммутаторы, причем выход первого коммутатора подключен к управляющему входу второго коммутатора, информационные входы которого и одни из входов первого коммутатора являются входами блока, .первым и вторым выходами и управляющими входами которого являются соответственно выхоц второго коммутатора, выход и другие входы первого коммутатора. На фиг. 1 представлена функциональная схема предложенного устройства, на фиг. 2 - функциональная схема блока задания массива адресов, на фиг, 3 - функциональная схема формирователя сигналов , Устройство содержит (фиг, 1) формирователь 1 синхросигналов, первый 2 и второй 2г счетчики адреса, счетчик 3 циклов, формирователь 4 тестовых сигналов, формирователь 5 сигналов ошибки, блок 6 согласования урор ней напряжений, блок 7 местного управления, выполненный в виде пульта управления, коммутаторы 8, формирователь 9 сигналов переноса, блок 10 задания массива адресов и делитель 11частоты. Блок 10 задания массива адресов содержит (фиг. 2) первый коммутатор 12с входами 13 и 14 и выходом 15 и второй коммутатор 16 с информацион ными входами 17 и 18 и выходом 19. Формирователь 9 сигналов переноса содержит (фиг. 3) элементы И 20, 21 и 22 и коммутатор 23. На фиг. 3 обоз начены входы 24, 25 и 26 и выход 27 формирователя. Длина первого счетчика 2( адреса соответствует минимальной емкости микросхем , на которых может быть построена проверяемая память, а второй счетчик 22 адреса выполнен таким образом, что путем перестройки межразрядных связей позволяет поразрядно наращивать длину цервого счетчика 2 адреса. Устройство работает следующим образом. В начальный момент времени счетчики 2, 2 и 3 (фиг. 1) находятся, в исходном состоянии. Каждое состот ян-ие счетчиков 2 и 2 соответствует определенной ячейке контролируемой памяти, а состояние счетчика 3 - выбору определенного контролирующего теста. По сигналу Пуск с блока 7 форми рователь 1 вырабатывает управляющие сигналы, необходимые для функционирования проверяемого устройстёа памяти.- . . Управляющие сигналы, код операций информационное слово и адрес через блок 6 поступают в проверяемое устройство, которое вьтолняет соответствующую операцию (запись или чтение информации) с выбранной ячейкой памяти. В режиме чтение информационное слово с выходов контролируемой памяти через блок б поступает на информационные входы формирователя 5,. на контрольные входы которого с выхода формирователя 4 поступает контроль,ное информационное слово. Формирователь 5 управляет работой формирователя 1 и Б случае наличия ошибок запрещает изменение, адреса контроли руемой ячейки памяти и выводит результаты контроля на индикацию. В этом случав устройство осуществляет многократное чтение информации из ячейки, содержащей ошибку, что дает возможность оператору приступить к ее поиску и устранению. При отсутствии ошибок формирователь 1 вырабатывает сигнал, который поступает на счетный вход счетчика 2, изменяет его состояние на единицу и тем самым подготавливает устрой ство для обращения к следующей ячейке памяти. В дальнейшем работа устройства повторяется, происходит серия последовательных обращений к проверяемым ячейкам контролируемой памяти до тех пор, пока не будет проверена вся память. После этого изменяется состояние счетчика 3 и устройство переходит к выполнению последующего теста. В процессе работы устройства, в зависимости от кода, поступающего с выходов счетчика 2у На входы 13 коммутатора 12 (фиг. 2), потенциал одного из его выбранных информационных входов 14 коммутируется на второй выход 15 блока 10 и управляющий вход -коммутатора 16, осуществляющего коммутацию входов 17 и 18 на выход 19. Последовательность нулевых и единичных потенциалов, заданных на входах 14 KOMt iyTaTopa 12, определяет конфигурацию массива адресов., причем единичный потенциал соответствует группе адресов, подлежащей проверке, а нулевой потенциал - запрещенной группе адресов. В зависимости от управляющей информации на входах 13 блок 10 анализирует, разрешена или запрещена проверка текущей гр1уппы адресов. Если проверка текущей группы адресов раз-, решена, блок 10 разрешает работу формирователя 1 и выдачу счетного импульса на вход счетчика 2jf . При этом происходит периодический пересчет адресов и проверка соответствующих им ячеек контролируемой памяти. Если .проверка текущей группы адpecoB запрещена, блок 10 запрещает формирование счетного импульса, и разрешает вырабатывать импульс, поступающий с его третьего выхода на вход 18 блока 10. Этот импульс передаетсся на выход блока 10, поступает На вход коммутаторов 8, затем на счетный вход счетчика 22 и изменяет состояние этого счетчика на единицу. Таким образом, любая группа ячеек памяти, емкост1 которой определяется длиной счетчика 2, или несколько произвольно расположенных групп ячеек памяти могут быть исключены из проверки, что позволяет обходить при проверке неисправные микросхемы пг1мяти и локализовать неисправ.ность с точностью до элемента. Автоматическая адаптация устройства к проверяемой памяти, отличающейся емкостью применяемых в ней микросхем, достигается за счет введения коммутаторов 8, формироватеЛИ 9 .и делителя 11 частоты, управляемого сигналами с выходов формирователя 9.

Известно, что динамические тестьа для полупроводниковых ЗУ оЕТанизуются в пределах полной емкости микросхем,памяти, используемих в проверяемых ЗУ, пЬэтому посредством коммутаторов 8, на первые входа которых поступают уйраляюиие сигналы от блока 7, осуиествляется nepecifpottKa счетчиков 2( и 2лi При этом в зависимости от емкости микросхем памяти, на построена проверяемая память, выбирается соответствующее количество разрядов счетчиков 2 и 2j (первая группа разрядЬв), Для которых организует естественньй порядок счета а последуйадие (старшие) разряды счетчика 2 jr выделяются в отдельную ВТОРУЮ группу, осу14ествляющую счет импульсов, поступающих на третьи входы коммутаторов 8 с выхо- да делителя 11 частоты.

Формирователь 9 бсуществляе формирование сигналов переноса для первой группы )азрядов счетчиков 2 и 22 соответствующей емкости микросхем памяти, которые поступают на ОДНи из входов/делителя 11 частоты. /

В. зависимости от теста, по которому контролируется проверяема память делитель 11 частоты осутест,вляет деление ча&тоты следования сиг налой переноса на требуемое число. Та«, Например/ если в тесте Марш 6суй1ёствляется двойной перебор всех ячеек проверяемого элемента пгиляти, :То.частота следования иг ульса йереноса делится на 2, а в тесте Скачу щая 1(0) частота сигналов Переноса делится на 2, -где N - колй41ество разрядов первой группы сметчиков 2ц и 2 .

Рассмотрим работу формирователя 9. В процессе работы на вход 24(фиг. 3) поступает сигнал переноса с выхода счетчика 2, а на вход 25 сигнал с выходовсчетчика 2. Эти 5 сигналы управляют работой элементов И 20, 21 и 22..;

Поскольку период следования сигналов типа Меандр, поступающих на первые входы элементов И 20, 21 и 22 o y №aивaeтcя с каждым последующим элементом И 20, 21 и 22, то и ч стоты сигналовна выходах Соседних из .элементов И 20, 21 И 22 отличаются в два раза. Сигналы О выходов элег s ментов И 20, 21 и 22 поступают на Шнформационные входы коммутатора 23 и, в зависимости от информации: На let-o управляющих, входах, один из сигналов коммутируется Навыход: 2 Т фор0 .мирователя 9,:,

Таким образом, ПОмере наращивания первой группй разрядов счетчит, ков 2 и 2 достигается вс1зможнс сть осуществлять на выходе формировате5 :|Ля 9 поразрядный сдвиг сигналов пе. реноса, что позволяет перестраивать . . счетчики и 2 применительно к емкоСти микросхем, на которых пОстроён.а проверяемая память. g .Благодаря такому построению достигается возможность адаптации устройства .к емкости проверяемых блоков памяти без йзм енения конструктивных связей путем смены котЛекта блоков в устройстве. . Технико-экономическое преимущеСтво предложенного устройства заключается в его более высокой надежности по сравнению С прототипом, а также 0 в том, чТо оно Позволяет проверять блоки памяти с различной емйостью применяемых в них микросхем.

23

Z7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1403097A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ , ПАМЯТИ, содержащее первый счетчик адреда, счетчик циклов, формирователь синхросигналов, формирователь тестовых сигналов, одни из йходов которого соединены бьответствённо с выходами счетчика циклов и с одними из выходов первого счетчика а выходы - с контрольными входами формигэователя сигналов ошибки и блока согласования уровней напряжений, выходы и информационные входа которого подключены соответственно к информационным входам формирователя сигналов ошибки и к nepBONQ выходу формирователя синхросигналов н управляющим входам формирователи сигналов ошибки, выход которого соединён с первым входом формирователя синхросигналов, второй вход и второй выходу которого подключены соответственно к первому вцХоду блока местного уп- равления и к счеТному входу первого счетчика адреса, о т л и ч а ю щ её с я тем, что, с целью повышения его надежности, в него введены вТорой счетчик адреса, блок задания массив.а адресов, коммутаторы, формирователь сигналов переноса и делитель частоты причем первый выход и одни из входов блока задания массива адресов соединены соответственно с первыми входами коммутаторов, с третьим эыходсм формирователя синхросигналов и с одними из входов формирователя .сигналов переноса и вторыми входами Коммутаторов, выходы и третьи входы которых подключены соответственно к счетному входу второго счетчика адреса и к выходу делителя частоты, Вх0дф4 которого соединены соответствен но с выходами счетчика циклов и с вы-р ходами формирователя сигналов перено-jS са, входа которого подкдиочены соответственно к одним из выходов второго счетчика адреса и к другому выходу первого счетчика адреса и второму входу блока зёшания массива адресов, ВТОРОЙ выход которого соединен с (третьим входом формирователя синхросигналов, другие входы являются управ .ляющими, другие выходы втррого счетчика шреса подключены к другим ввоО5 дам формирователя тестовых сигналов. Другие входы формирователя сигналов переноса и четвертый кол таторов являются управляющими. 2. Устройство по п. 1 о Т л и4:: ,чающееся тем, что блок задания массива адресов содержит коммутаторы, путчем выход первого коммутатора подключен к управляющему входу второго коммутатора, информационные входы которого и одни из входов .первого коммутатора являются входами блока, первым и вторым выходами и управляющими входами которого являются соответственно выход второго коммутатора, гыход и другие входы . первого коммутатора.

сриб.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ изготовления мозаичного электрода для иконоскопа | 1935 |

|

SU43977A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

Авторы

Даты

1983-12-15—Публикация

1982-03-12—Подача