л

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ и системах.

Целью изобретения является увеличение, точности.

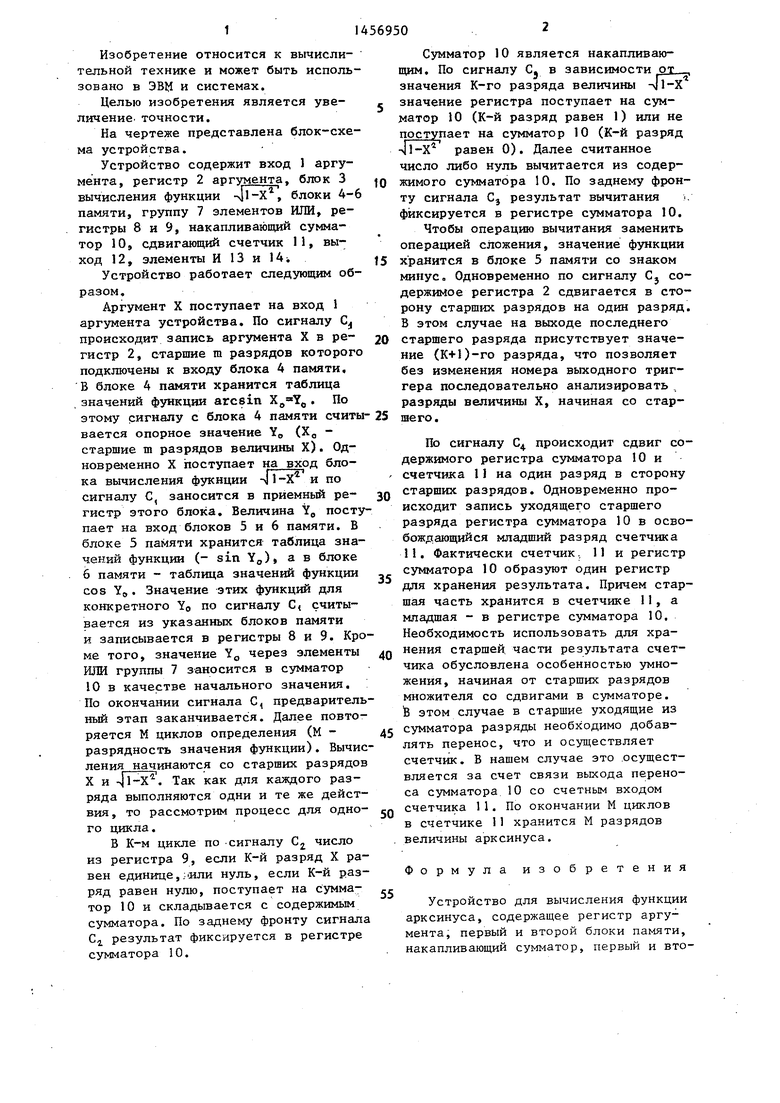

На чертеже представлена блок-схема устройства.

Устройство содержит вход 1 аргумента, регистр 2 аргумента, блок 3 вычисления функции -41-X , блоки 4-6 памяти, группу 7 элементов ИЛИ, регистры 8 и 9, накапливающий сумматор 10, сдвигающий счетчик 11, выход 12, элементы И 13 и 14

Устройство работает следующим образом.

Аргумент X поступает на вход 1 аргумента устройства. По сигналу С., происходит запись аргумента X в регистр 2, старшие m разрядов которого подключены к входу блока 4 памяти, В блоке 4 памяти хранится таблица значений функции arcsin . По этому сигналу с блока 4 памяти считы вается опорное значение Ye (Хо - старшие m разрядов величины X). Одновременно X поступает на вход блока вычисления фукнции -jl-X и по сигналу С, заносится в приемный регистр этого блока. Величина У поступает на вход блоков 5 и 6 памяти. В блоке 5 памяти хранится таблица значений функции (- sin YO), а в блоке 6 памяти - таблица значений функции cos YO. Значение этих фзшкций для конкретного YO по сигналу С, считывается из указанных блоков памяти и записывается в регистры 8 и 9. Кроме того, значение Y, через элементы ИЛИ группы 7 заносится в сумматор 10 в качестве начального значения. По окончании сигнала С, предварительный этап заканчивается. Далее повторяется М циклов определения (М - разрядность значения функции). Вычисления нал1инаются со старших разрядов X и . Так как для каждого разряда выполняются одни и те же действия , то рассмотрим процесс для одного цикла.

В К-м цикле по сигналу С число из регистра 9, если К-й разряд X равен единице,;«ли нуль, если К-й разряд равен нулю, поступает на сумматор 10 и складывается с содержимым сумматора. По заднему фронту сигнал GI результат фиксируется в регистре сумматора 10.

Сумматор 10 является накапливаю0

5

0

25 дО 45

30

35

50

55

щим. По сигналу С. в зависимости oi, значения К-го разряда величины -gl-X значение регистра поступает на сумматор 10 (К-й разряд равен 1) или не поступает на сумматор 10 (К-й разряд 1 -X равен 0). Далее считанное число либо нуль вычитается из содержимого сумматора 10. По заднему фронту сигнала Cj результат вычитания фиксируется в регистре сумматора 10. Чтобы операцию вычитания заменить операцией сложения, значение функции хранится в блоке 5 памяти со знаком минус. Одновременно по сигналу Cj содержимое регистра 2 сдвигается в сторону старших разрядов на один разряд. В этом случае на выходе последнего старшего разряда присутствует значение (К+)-го разряда, что позволяет без изменения номера выходного триггера последовательно анализировать , разряды величины X, начиная со старшего.

По сигналу 64. происходит сдвиг содержимого регистра сумматора 10 и счетчика 11 на один разряд в сторону старших разрядов. Одновременно происходит запись уходящего старшего разряда регистра сумматора 10 в освобождающийся младший разряд счетчика П. Фактически счетчик, 11 и регистр сумматора 10 образуют один регистр для хранения результата. Причем старшая часть хранится в счетчике 11, а младшая - в регистре сумматора 10. Необходимость использовать для хранения старшей, части результата счетчика обусловлена особенностью умножения, начиная от старших разрядов множителя со сдвигами в сумматоре. Ь этом случае в старшие уходящие из сумматора разряды необходимо добавлять перенос, что и осуществляет счетчик. В нашем случае это .осуществляется за счет связи вькода переноса сумматора 10 со счетным входом счетчика 11. По окончании М циклов в счетчике 11 хранится М разрядов величины арксинуса.

Формула изобретения

Устройство для вычисления функции арксинуса, содержащее регистр аргумента, первый и второй блоки памяти, накапливающий сумматор, первый и вто

рой регистры, причем вход аргумента устройства соединен с информационным входом регистра аргумента, выход старших разрядов которого соединен с адресным входом первого блока памяти отличающееся тем, что, с целью увеличения точности, в него введены третий блок памяти, два элемента И, группа элементов ИЛИ, сдви- ганлций счетчик и блок вычисления

f

функции -Jl-X , причем выход старшего разряда регистра аргумента соединен с первым входом первого элемента И, выход первого блока памяти соединен с адресными входами второго и третьего блоков памяти и поразрядно с первыми входами соответствующих элементов ШЩ группы, выходы второго и третьего блоков памяти соединены с информационными входами соответственно первого и второго регистров, ёьссоды которых поразрядно соединены соответственно с первьми и вторыми входами соответствующих элементов ИЛИ группы, выходы которых соединены с информационным входом накапливаю- щёло сумматора, выход старшего разряда которого соединен с последовательным входом сдвигаклцего счетчика, счетный вход и вькод которого соединены соответственно с выходом переноса накапливающего cyNMaTopa и выхо

дом старших разрядов арксинуса устройства, последовательный и парал- лельный вь1ходы блока вычисления функ0

5

0

ции

соединены

соответственно с первым входом второго элемента И и

BTOPOI AfbF

ВЫХОДОМ функции л|1-Х устройства, выходы первого и второго элементов И соединены с входами разрешения считывания соответственно второго и первого регистров, вход аргумента устройства соединен с входом аргумента блока вычисления функции , вход первого тактового импульса устройства соединен с входами разрешения за-- писи регистра аргумента, первого и вторюго регист ров и блока вычисления функции л11-Х и входами разрешения считывания всех блоков памяти8 вход второго тактового импульса устройства соединен с вторым входом первого элемента И, вход третьего тактового импульса устройства соединен с вторым входом второго элемента И, так5 товым вхоудом блока вычисления функции лП-Х и входом сдвига регистра аргумента, вход четвертого тактового импульса устройства соединен с входами сдвига информации в блоке вы0 числения функции лГь-Х% сдвигающего счетчика и накапливающего сумматора, вход синхронизации которого соединен с тактовым входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Устройство для вычисления экспоненты | 1988 |

|

SU1636843A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВЙ и системах. Целью . изобретения является увеличение точности. Устройство содержит вход 1 аргумента, регистр 2 аргумента, блок 3 вычисления функции -vjl-X , блоки 4-6 памяти, группу 7 элементов ИЛИ, регистры 8, 9, накапливающий сумматор I О, сдвигающий счетчик II, выход. 12, элементы И 13, 14. I ил.

Составитель А.Зорин Редактор О.Юрковецкая Техред М.Ходанич Корректор С.Черни

Заказ 7489/47

Тираж 667

ВНИНПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-07—Публикация

1986-05-15—Подача