О vj 4Ьь Ю СЛ Ю

Изобретение относится к вычислительной технике и может использоваться в системах обработки информации.

Целью изобретения является повышение выхода годных микросхем памяти.

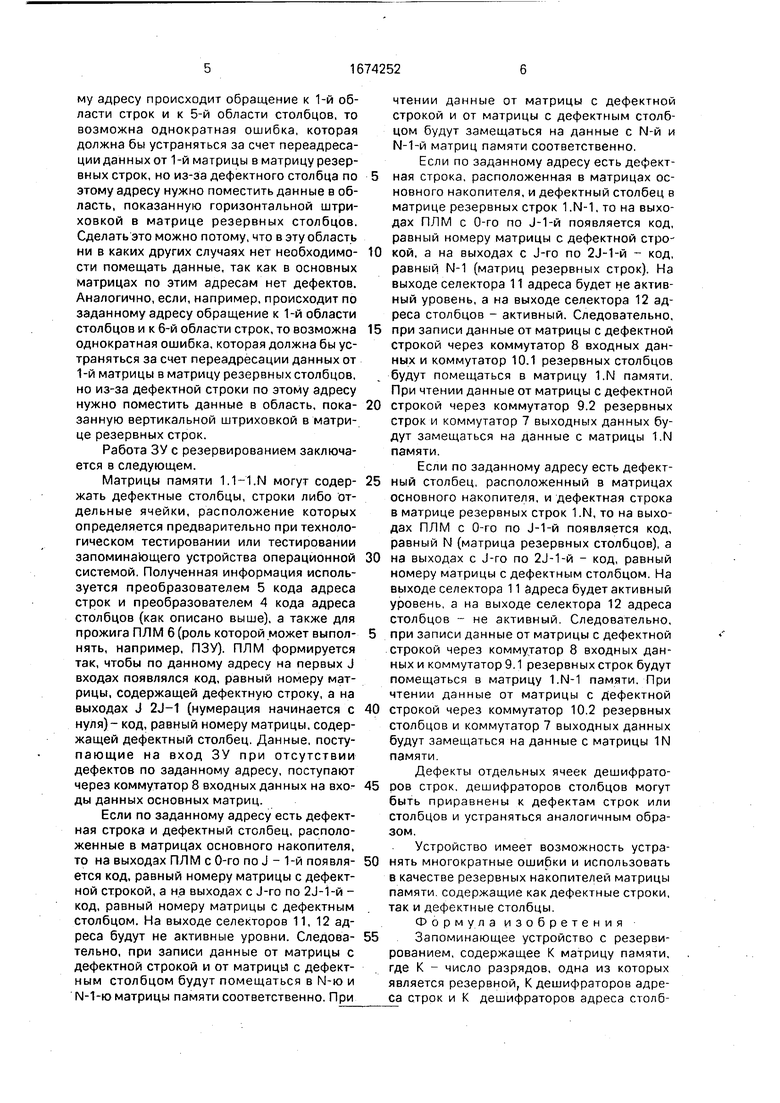

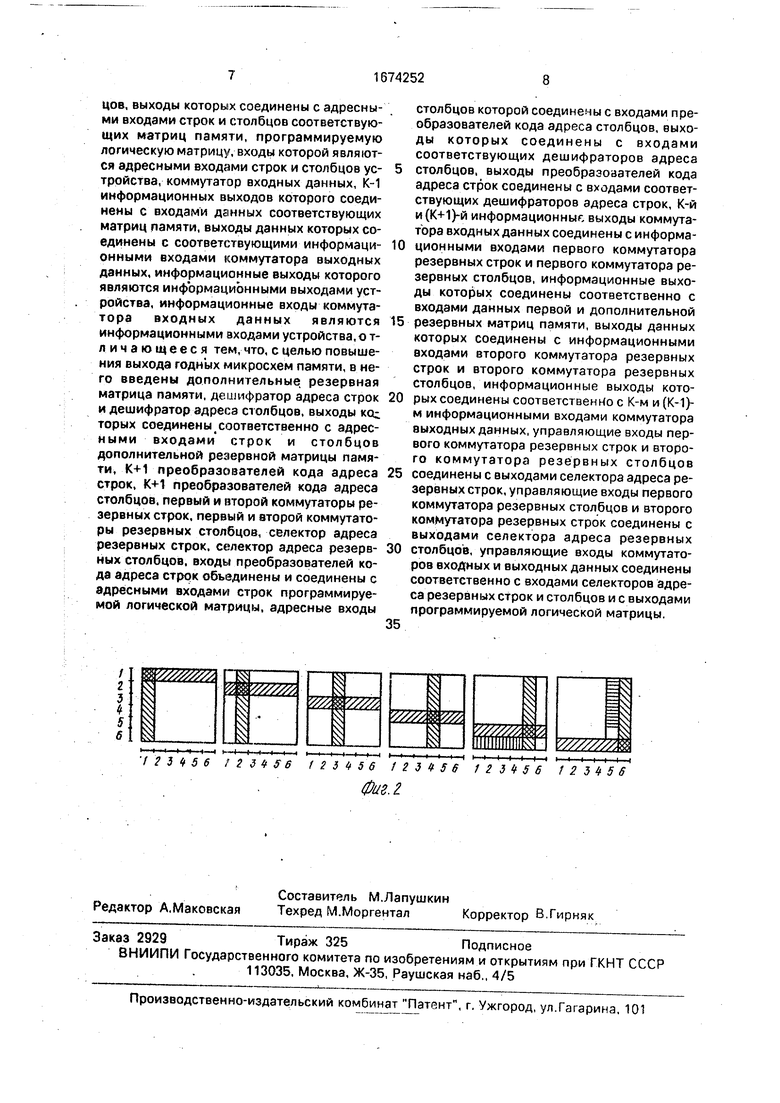

На фиг.1 показана структурная схема запоминающего устройства с резервированием; на фиг.2 - пример принципа работы запоминающего устройства с резервированием.

Устройство содержит матриц памяти 1.1-1.N, N дешифраторов адреса строк 2.1-2.N и N дешифраторов адреса столбцов 3.1-3.N, N преобразователей кода адреса столбцов4.1-4.М, N преобразователей кода адреса строк 5.1-5.N, программируемую логическую матрицу 6(ПЛМ), коммутатор выходных данных, коммутатор 8 входных данных, первый 9.1 и второй 9.2 коммутаторы резервных строк, первый 10.1 и второй 10.2 коммутаторы резервных столбцов, се- лектор 11 адреса резервных строк и селектор 12 адреса резервных столбцов.

Принцип работы ЗУ с резервированием заключается в следующем.

Матрицы памяти 1.1-1.N могут содер- жать дефектные столбцы, строки либо отдельные ячейки, расположение которых определяется предварительно при технологическом тестировании или тестировании запоминающего устройства операционной системой. Преобразователи кода адреса столбца 4.1-4.N и адреса строки 5.1-5.N представляют собой, например, запоминающие устройства, на адресный вход которых поступают соответственно адреса столбца и строки, а содержимое ячеек является фактическим номером используемого столбца или строки матрицы памяти. Если осуществляется технологическое тестирование матриц памяти, то преобразователи адреса могут представлять собой постоянные запоминающие устройства, программируемые в процессе изготовления кристаллов. При тестировании операционной системой в качестве преобразователей могут использоваться ОЗУ, заполняемые в процессе тестирования. Блоки и связи, необходимые для занесения информации в преобразователи адресов в последнем случае, не принципиальны для работы предла- гаемого устройства и на функциональной схеме не показаны. Объем дополнительной памяти, необходимый для хранения информации в преобразователях адресов, мал по сравнению с объемом основных матриц па- мяти. Так, при объеме матрицы 256 Кбит ее размер 512 строк на 512 столбцов, необходимый объем дополнительной памяти 9К, т.е. менее 4% основной памяти.

Если суммарное количество дефектных строк во всех матрицах памяти не превышает количества строк одной матрицы и суммарное количество дефектных столбцов во всех матрицах памяти не превышает количества столбцов одной матрицы, то всегда путем преобразования адресов строк и столбцов можно добиться, чтобы по одному и тому же адресу было не более одной дефектной строки и не более одного дефектного столбца. Следовательно, после преобразования адресов, максимальная кратность ошибки будет равна 2 (в одной матрице есть дефектная строка, в другой - дефектный столбец). Поэтому для устранения дефектов достаточно иметь две резервные матрицы - матрицу резервных строк и матрицу резервных столбцов. Но при наличии одновременно дефектных строк и дефектных столбцов в резервных матрицах нельзя просто перекоммутировать данные с основной матрицы на резервную, так как все равно будет существовать дефектная область (дефектные столбцы в матрице резервных строк и дефектные строки в матрице резервных столбцов). В то же время в резервных матрицах можно выделить годные области, которые не принимают участия в сохранении данных. Это ячейки памяти, расположенные: в матрице резервных строк - по адресам ячеек памяти, образованных дефектными строками и столбцами в матрице резервных столбцов: в матрице резервных столбцов - по адресам ячеек памяти, образованных дефектными строками и столбцами в матрице резервных строк. Если адрес теперь подан так, что он попадает на дефектную строку в основной матрице и на дефектный столбец в матрице резервных строк, то можно поместить данные не в матрицу резервных строк, а в матрицу резервных столбцов. Аналогично можно поступить, когда поданный адрес попадает на дефектный столбец в основной матрице и на дефектную строку в матрице дефектных столбцов.

Поясним все это на примере. Пусть после переадресации дефектные строки и столбцы расположены в матрицах памяти, как показано на фиг.2 (штриховкой вправо для каждой матрицы обозначены области дефектных строк, штриховкой влево - области дефектных столбцов). Если, например, по заданному адресу происходит обращение к 1-й области строк и к 3-й области столбцов, то возможна двойная ошибка, которая устраняется за счет переадресации данных от 1-й и 3-й матриц соответственно в матрицу резервных строк и матрицу резервных столбцов. Если, например, но заданному адресу происходит обращение к 1-й области строк и к 5-й области столбцов, то возможна однократная ошибка, которая должна бы устраняться за счет переадресации данных от 1-й матрицы в матрицу резервных строк, но из-за дефектного столбца по этому адресу нужно поместить данные в область, показанную горизонтальной штриховкой в матрице резервных столбцов. Сделать это можно потому, что в эту область ни в каких других случаях нет необходимости помещать данные, так как в основных матрицах по этим адресам нет дефектов. Аналогично, если, например, происходит по заданному адресу обращение к 1-й области столбцов и к 6-й области строк, то возможна однократная ошибка, которая должна бы устраняться за счет переадресации данных от 1-й матрицы в матрицу резервных столбцов. но из-за дефектной строки по этому адресу нужно поместить данные в область, показанную вертикальной штриховкой в матрице резервных строк.

Работа ЗУ с резервированием заключается в следующем.

Матрицы памяти 1.1-1.N могут содержать дефектные столбцы, строки либо отдельные ячейки, расположение которых определяется предварительно при технологическом тестировании или тестировании запоминающего устройства операционной системой. Полученная информация используется преобразователем 5 кода адреса строк и преобразователем 4 кода адреса столбцов (как описано выше), а также для прожига ПЛМ 6 (роль которой может выполнять, например, ПЗУ). ПЛМ формируется так, чтобы по данному адресу на первых J входах появлялся код, равный номеру матрицы, содержащей дефектную строку, а на выходах J 2J-1 (нумерация начинается с нуля) - код, равный номеру матрицы, содержащей дефектный столбец. Данные, поступающие на вход ЗУ при отсутствии дефектов по заданному адресу, поступают через коммутатор 8 входных данных на входы данных основных матриц.

Если по заданному адресу есть дефектная строка и дефектный столбец, расположенные в матрицах основного накопителя, то на выходах ПЛМ с 0-го по J - 1-й появляется код, равный номеру матрицы с дефектной строкой, а на выходах с J-ro по - код, равный номеру матрицы с дефектным столбцом. На выходе селекторов 11, 12 адреса будут не активные уровни, Следовательно, при записи данные от матрицы с дефектной строкой и от матрицы с дефектным столбцом будут помещаться в N-ю и N-1-ю матрицы памяти соответственно. При

чтении данные от матрицы с дефектной строкой и от матрицы с дефектным столбцом будут замещаться на данные с N-й и N-1-й матриц памяти соответственно.

Если по заданному адресу есть дефектная строка, расположенная в матрицах основного накопителя, и дефектный столбец в матрице резервных строк 1 .N-1, то на выходах ПЛМ с 0-го по J-1-й появляется код, равный номеру матрицы с дефектной стро0 кой, а на выходах с J-ro по - код, равный N-1 (матриц резервных строк). На выходе селектора 11 адреса будет не активный уровень, а на выходе селектора 12 адреса столбцов - активный. Следовательно.

5 при записи данные от матрицы с дефектной строкой через коммутатор 8 входных данных и коммутатор 10.1 резервных столбцов будут помещаться в матрицу 1.N памяти. При чтении данные от матрицы с дефектной

0 строкой через коммутатор 9.2 резервных строк и коммутатор 7 выходных данных будут замещаться на данные с матрицы 1.N памяти.

Если по заданному адресу есть дефект5 ный столбец, расположенный в матрицах основного накопителя, и дефектная строка в матрице резервных строк 1.N, то на выходах ПЛМ с 0-го по J-1-й появляется код, равный N (матрица резервных столбцов), а

0 на выходах с J-ro no 2J-1-U - код. равный номеру матрицы с дефектным столбцом. На выходе селектора 11 адреса будет активный уровень, а на выходе селектора 12 адреса столбцов - не активный. Следовательно.

при записи данные от матрицы с дефектной строкой через коммутатор 8 входных данных и коммутатор 9.1 резервных строк будут помещаться в матрицу 1.N-1 памяти. При чтении данные от матрицы с дефектной

0 строкой через коммутатор 10.2 резервных столбцов и коммутатор 7 выходных данных будут замещаться на данные с матрицы 1N памяти.

Дефекты отдельных ячеек дешифрато5 DOB строк, дешифраторов столбцов могут быть приравнены к дефектам строк или столбцов и устраняться аналогичным образом.

Устройство имеет возможность устра0 нять многократные ошибки и использовать в качестве резервных накопителей матрицы памяти, содержащие как дефектные строки, так и дефектные столбцы.

Формула изобретения

5Запоминающее устройство с резервированием, содержащее К матрицу памяти, где К - число разрядов, одна из которых является резервной, К дешифраторов адреса строк и К дешифраторов адреса столбцов, выходы которых соединены с адресными входами строк и столбцов соответствующих матриц памяти, программируемую логическую матрицу, входы которой являются адресными входами строк и столбцов устройства, коммутатор входных данных, К-1 информационных выходов которого соединены с входами данных соответствующих матриц памяти, выходы данных которых соединены с соответствующими информационными входами коммутатора выходных данных, информационные выходы которого являются информационными выходами устройства, информационные входы коммутатора входных данных являются информационными входами устройства, о т- личающееся тем, что, с целью повышения выхода годных микросхем памяти, в него введены дополнительные резервная матрица памяти, дешифратор адреса строк и дешифратор адреса столбцов, выходы кос торых соединены соответствен но с адресными входами строк и столбцов дополнительной резервной матрицы памяти, К+1 преобразователей кода адреса строк. К+1 преобразователей кода адреса столбцов, первый и второй коммутаторы резервных строк, первый и второй коммутаторы резервных столбцов, селектор адреса резервных строк, селектор адреса резервных столбцов, входы преобразователей кода адреса строк объединены и соединены с адресными входами строк программируемой логической матрицы, адресные входы

столбцов которой соединены с входами преобразователей кода адреса столбцов, выходы которых соединены с входами соответствующих дешифраторов адреса

столбцов, выходы преобраэоаателей кода адреса строк соединены с входами соответствующих дешифраторов адреса строк, К-й и(К+1)-й информационные выходы коммутатора входных данных соединены с информационными входами первого коммутатора резервных строк и первого коммутатора резервных столбцов, информационные выходы которых соединены соответственно с входами данных первой и дополнительной

резервных матриц памяти, выходы данных которых соединены с информационными входами второго коммутатора резервных строк и второго коммутатора резервных столбцов, информационные выходы которых соединены соответственно с К-м и(К-1)- м информационными входами коммутатора выходных данных, управляющие входы первого коммутатора резервных строк и второго коммутатора резервных столбцов

соединены с выходами селектора адреса резервных строк, управляющие входы первого коммутатора резервных столбцов и второго коммутатора резервных строк соединены с выходами селектора адреса резервных

столбцов, управляющие входы коммутаторов входных и выходных данных соединены соответственно с входами селекторов адреса резервных строк и столбцов и с выходами программируемой логической матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Запоминающее устройство | 1982 |

|

SU1023393A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Запоминающее устройство | 1984 |

|

SU1241291A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1418816A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

Изобретение относится к вычислительной технике и может использоваться в системах обработки информации. Целью изобретения является повышение выхода годных микросхем памяти. Устройство содержит (K + 1) матриц памяти 1, две из которых являются резервными, N дешифраторов адреса строк 2, N дешифраторов адреса столбцов 3, N преобразователей кода адреса строк 5, N преобразователей кода адреса столбцов 4, программируемую логическую матрицу 6, коммутаторы выходных 7 и входных 8 данных, коммутаторы резервных строк 9 и столбцов 10, селекторы адреса резервных строк 11 и резервных столбцов 12. Устройство позволяет устранить многократные отказы при использовании резервных матриц памяти, содержащих дефектные столбцы и строки. 2 ил.

| Резервированное запоминающее устройство | 1985 |

|

SU1370668A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Конопельке В.К. | |||

| Лосев В.В | |||

| Надежное хранение информации в полупроводниковых запоминающих устройствах | |||

| М.: Радио и связь, 1986 | |||

| с | |||

| Ударно-вращательная врубовая машина | 1922 |

|

SU126A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-08-30—Публикация

1989-01-02—Подача