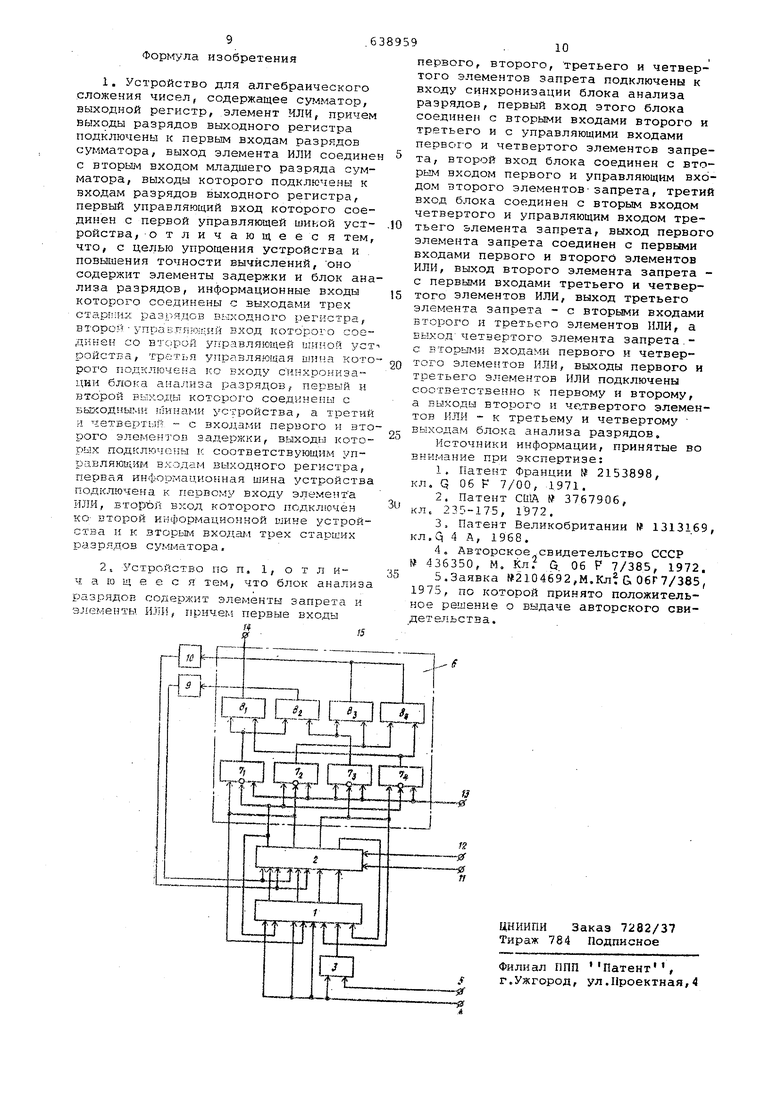

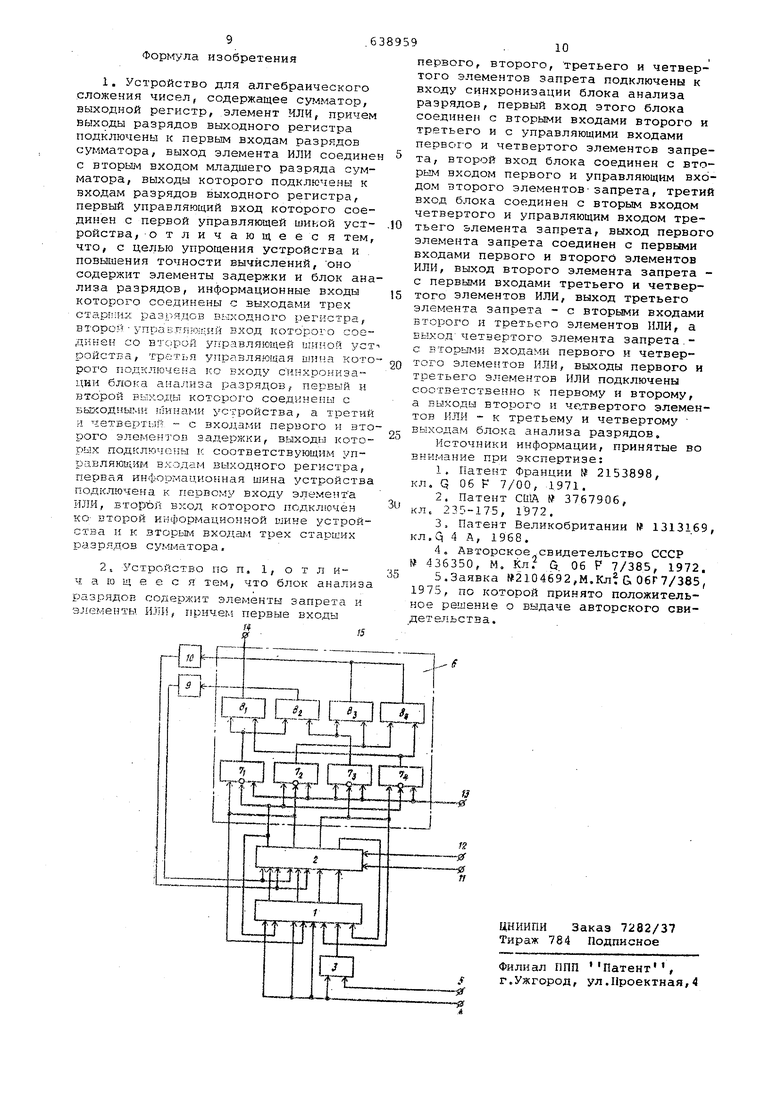

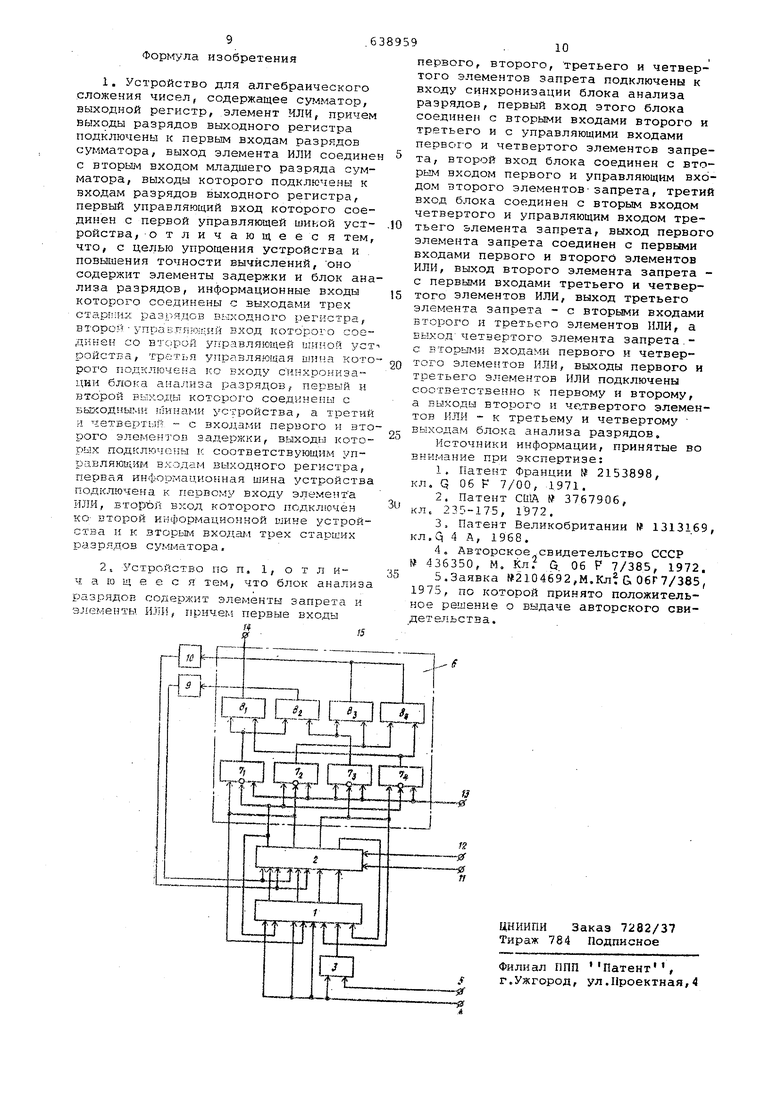

6 ключеиы к первым входам разрядов сумматора, выход элемента ИЛИ соединен с вторь. входом младшего разряда сумматора f выходы которого подключены к входам разрядов выходного регистра, первый управляющий вход которого соединен с первой управляющей шиной устройства 5 . В этом устройстве для представления операндов и результата используется избыточная дв ичная система счис ления с цифрами , 1,0,1,2ф:После полу чения К разрядов, младший из которых имеет вход 2 , погрешность вычисления в устройстве не превьшает по модулю значения.Z. а 2 , где, П - разрядность окончательного результата; Ck цифры результата. Поскольку j Oil ддощд : 2 можно 3 и ЛЮчить, что известное устройство обладает глухой точностью. Кроме того, это устройство имеет довольно сложную конструкцию Целью изобретения является упрощение устройства и повышение точности вычислений Для этого устройство содержит элементы задержки и блок анализа разрядов , информационные входы которого соединены с выходами трех старших разрядов вылодного регистра, второй управляющий вход которого соединен с второй управляющей шиной устройств,, третья управляющая шина которого под ключена к входу синхронизации блока анализа разрядов первый и второй БЫ ходы которого соединены с выходньи /тн шинами устройства, а третий и четвер тый - с входами первого и второго эл ментов задеркки, выходы которых под кЛючены к соответствующим управляющим входам выходного регистра, первая ин формационная шина устройства подклю™ чена к первому входу элемента ИЛИ, второй вход которого подключен к вто рой информационной шине устройства н к вторьи ч входам трех старших разрядов сумматора Кроме того блок анализа разрядов содержит элементы запрета и элементы ИЛИ, причем первые входы первого,второго, третьего и четвертого элементов запрета подключены к входу Ьинхронизации блока анализа разрядов первый вход этого блока соединен с вторыми входами второго и третьего и с управляющими входами первого и четвертого элементов запрета, второй вкод блока соединен с вторым входом первого и управляющим входом второго элементов запрета, третий вход блока соединенно вторым входом четвертого и управляющим входом.третьего элемен та запрета, выход первого элемента запрета соединен с первыми входами первого и второго элементов ИЛИ, выход второго элемента запрета - с пер вглми входами третьего и четвертого 4 элементов ИЛИ, выход третьего элемента запрета - с вторыми входами второго и третьего элементов ИЛИ, а выход четвертого элемента запрета - с вторыми входами первого и четвертого элементов ИЛИ, выходы первого и третьего элементов ИЛИ подключены соответственно к первому и второму, а .ы второго и четвертого элементов ИЛИ - к третьему и четвертому выходам блока анализа разрядов„ На чертеже изображена функциональная схема устройства для алгебраического сложения чисел. В состав устройства входят cyNmaтор 1 и выходной регистр 2, имеющий цепь сдвигов. Сумматор 1 и выходной регистр 2 содержат четыре разряда. Вьзходы суг-д-матора 1 подключены к входам нькодного регистра 2, причем выход - го разряда cy№v aTopa 1 подключен по зкоду J - го разряда выходного регистра 2 . Выходы выходного регистра 2 подключены к входам суьматора 1, причем выход j - го разряда выходного регистра 2 связан с одним входом j - го разряда сул-шатора 1 Устройство также содержит элемент ИЛИ 3 и информационные входы 4, 5 Выход элемента ИЛИ 3 подключен к входу младшего разряда сумг-итора 1 „ Информационный вход 4 связан с вторыгли входами трех старших разрядов сумматора 1 н одним входом элемента ИЛИ 3, Второй вход элемента ИЛИ 3 связан с глнформа-ционньай входо.м 5, 3 состав устройства также входят блок б анализа разрядов, содержащий элементы запрета 1i Т и элементы ИЛИ 8 - 8 , а также элементы задержки 9 и 10, Выходы трех старших разрядов выкодного регистра 2 подлключены к входам блока анализа разрядов 6, причем первого (старшего) разряда выходного ре.гистра 2 связан с инверсными входами элементов запрета 7 и 7д и с прямыми входами элементов запрега /2 и 70 , Выход второго разряда в«2ходного регистра 2 подключен к прямом входу элемента запрета и к инверсному входу эл. iBHTa запрета 7е . Выход ретьего разряда выходного регистра 2 связан с инверсным входом элемента запрета 7§ и лрякййм входом элемента запрета 7. а Выходы элементов запрета 7j - 74 подключены к входам элементов ИЛИ . Выход элемента запрета 7 подключен к входам элементов 1-ШИ 8 , Sg Выход элемента запрета 7g связан со входами элемента ИЛИ 8, 84 , Выход элемента запрета 7 подключен к вкодам элементов ИЛИ 3 к 8 Выход элемента запрета. 7д связан с вяодагли элементов ИЛИ 8 84, Выход элемента ИЛИ Sj связан с вх дом элемента задержки 9, выход которого подключен к входам установки в О двух старших разрядов выходног регистра 2. Выход элемента ИЛИ 84. связан с вх дом элемента задержки 10, выход кото рого подключен к входам установки в двух старших разрядов выходног регистра 2, Кроме того, устройство содержит управляющие входы 11, 12, 13 и выход 14, 15. Управляющий вход 11 подключен к цепи Приемки кода выходного регистра 2, Управляющий вход 12 связан с цепь сдвига выходного регистра 2.. Управля ющий вход 13 связан с управляющим входом блока анализа разрядов 6, а именно с входами элементов запрета 7i - 74.. Выходы 14, 15 соединены с выходам .блока анализа разрядов б, причем выход 14 связан с выходом элемента ИЛИ а выход 15 соединен с выходом эле мента ИЛИ 8. В качестве сумматора 1 может быть использован четырехразрядный комбина ционный сулчматоре : Выходной регистр 2 может быть построен по схеме сдвигающего регистра Прием кода в выходной регистр 2 из сумматора производится с задержкой, которая определяется внутренним стро нием триггеров, из которых построен выходной регистр 2 (триггеры с внутренней задеряской) , Предлагаемое устройство работает следующим образом. В начальном состоянии выходной регистр 2 установлен в нулевое состояние Алгебраическая двух чисел вычисляется в (п 2 циклах,, каждый из которых состоит из четырех тактов, где п - разрядность представления операндов« На управляющие входы 11, 12, 13 последовательно во .времени поступают управляющие сигналы К началу первого такта казкдого i -го цикла на информационные вхо,цы 4 5 поступают -и разряд первого опера да. Если единичный сигнал поступит на информацион ный вход 4 это говорит о том, что i -и разряд.первого операнда численно равен 1 если единичный сигнал поступит на информационный вход 5, это свидетельствует о том, что } -и разряд первого операнда чис ленно равен I; если же единичный сигнал не поступит ни на один из информа ционных входов 4, 5, это еви,цетель ствует о том, что -и разряд первого операнда численно равен нулю, Код, описанный в выходном регистре 2, суммируется с кодом, поступаклци с информационных входов 4, 5, причем сигнал, пропорциональнЕлй 1, представлен в дополнительном виде. В первом такте по управляющему сигналу, поступающему на управляющий вход 11, производится прием кола с выходов сумматора 1 в выходной регистр 2 „ К началу второго такта на информационные входы 4 и 5 поступает i й разряд второго операнда, также пропорциональным двоичньом кодом с цифрами Г, О, 1 в каждом разряде. Содержание выходного регистра 2 суммируется с кодом, поступающим с информационных входов 4 и 5, Во втором такте по управляющему сигналу, поступающему также на управляющий вход 11, производится прием кода в выходной регистр 2. В результате, по окончании второго такта, в выходном регистре 2 образуется код, значение которого равно значению очередных разрядов операндов, и кода, который был записан в выходном регистре 2 перед началом 1цикла. В третьем такте по управляющему сигналу, поступающему на управляющий вход 13, производится выдача информации на выходе устройства. Два старших разряда выходного регистра 2 являются знaкoвы Iiв Тогда, если значение кода, записанного в выходном регистре 2,lR-i--j; то единичный сигнал появится на выходе 15. что свидетельствует о том, что очередной разряд алгебраической сумж численно равен 1 о, . ЕслиТ -|;, то единичный сигнал появится на выходе 14, что свидетельствует о TOMf что очередной разряд результата численно равен 1„ - аналогичный сигнал не появится ни на одном из выходов 14, 15, что свидетельств5вт о том, что очередной разряд алгебраической cyb.iMbJ численно равен нулю. Кроме того, в третьем такте производится начальная установка двух старших (знаковых) разрядов внходного регистра 2 через время, гопределяемое элементами задержки 9 и 10, При этом, если единичный сигнал присутствует на выходе элемента ИЛИ 8 , знаковые разряды выходного регистра 2 устанавливаются в нулевое состояние. Если единичный сигнал присутствует на выходе элемента ИЛИ 8, то знаковые разряды выходного регистра 2 устанавливаются в единичное состояниеЕсли же единичный сигнал не присутствует одном из выходов элементов ИЛИ 82, 8 , знаковые разряды выхолного регистра 2 не меняют своего состояния.-. При это-М выполняется условие; время задержки распространения сигналов в элементах задержки 9,- 1-0 больше

длительности управлякацего сигнала, поступакнцего на управляющий вход 13,

В четвертом такте по управляющему сигналу, поступающему на управляющий вход 12, производится сдвиг влево кода, записанного в выходном регистре 2

В результате выполнения ( 2) циклов на выходах 14, 15 последовагельно разряд за разрядом формируется значение алгебраической суммы двух чисел,представленное избыточным двоичным кодом с цифрами Г, О, 1 в каждом разряде.

Ввиду того, что операция содержит П разрядов S (П -f 1) и (п+2) циклах на входы 4 и 5 единичные сигналы не поступают; (П4-1) и () разряды операндов численно равны нулю.

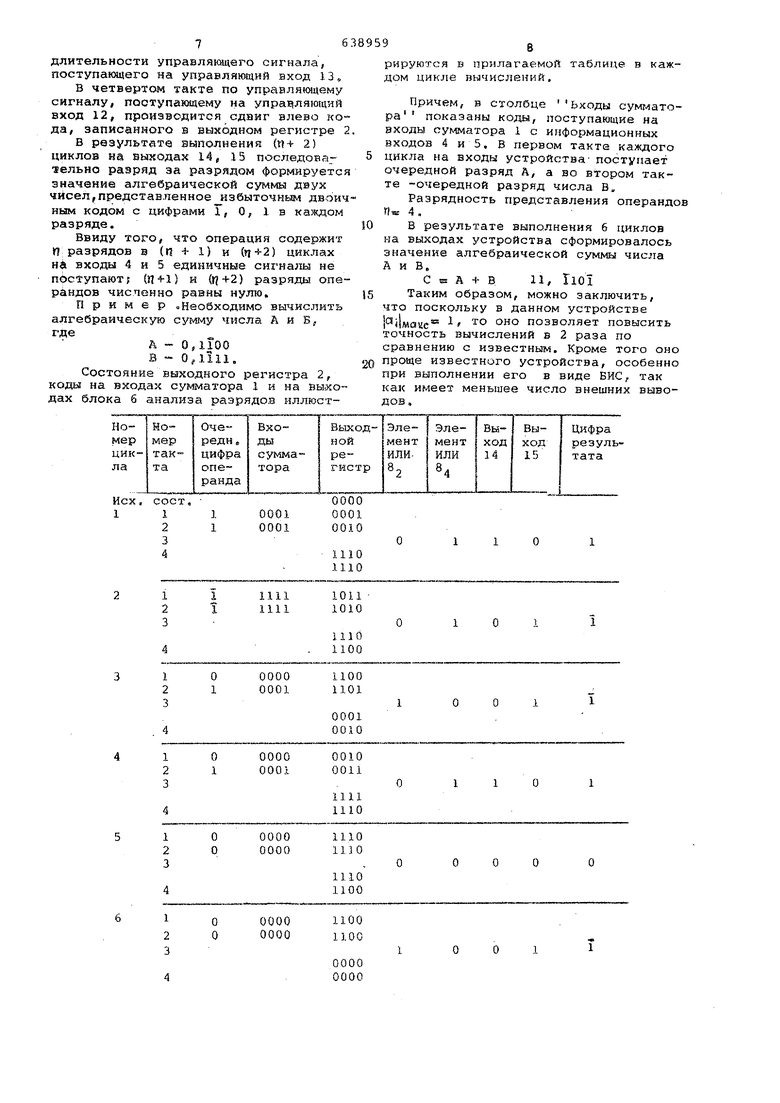

Пример .Необходимо вычислить алгебраическую cywvsy числа А и Б, где

А OfllOO В - Of 3.111.

Состояние выходного регистра 2, коды на входах сумматора 1 и на вы-ходах блока б анализа разрядов иллюстрируются в прилагаемой таблице в каждом цикле вычислений.

Д1ричем, в столбце Ьходы сумг-saToра показаны коды, поступающие на входы сумматора 1 с информационных входов 4 и 5. В первом такте каждого цикла на входы устройства- поступает очередной разряд А, а во втором такте -очередной разряд числа В,

Разрядность представления операндов Пж 4 ,

В результате выполнения 6 циклов на выходах устройства сформировалось значение алгебраической суммы числа А и В.

С в А + В 11, ГЮ

Таким образом, можно заключить, что поскольку в данном устройстве | маис° позволяет повысить точность вычислений в 2 раза по сравнению с известным. Кроме того оно

проще известного устройства, особенно при выполнении его в виде ВИС, так как имеет меньшее число внешних выводов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Устройство для нормализации чисел | 1980 |

|

SU953636A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

Авторы

Даты

1978-12-25—Публикация

1976-04-26—Подача