1-(1-11

41

Gb СО

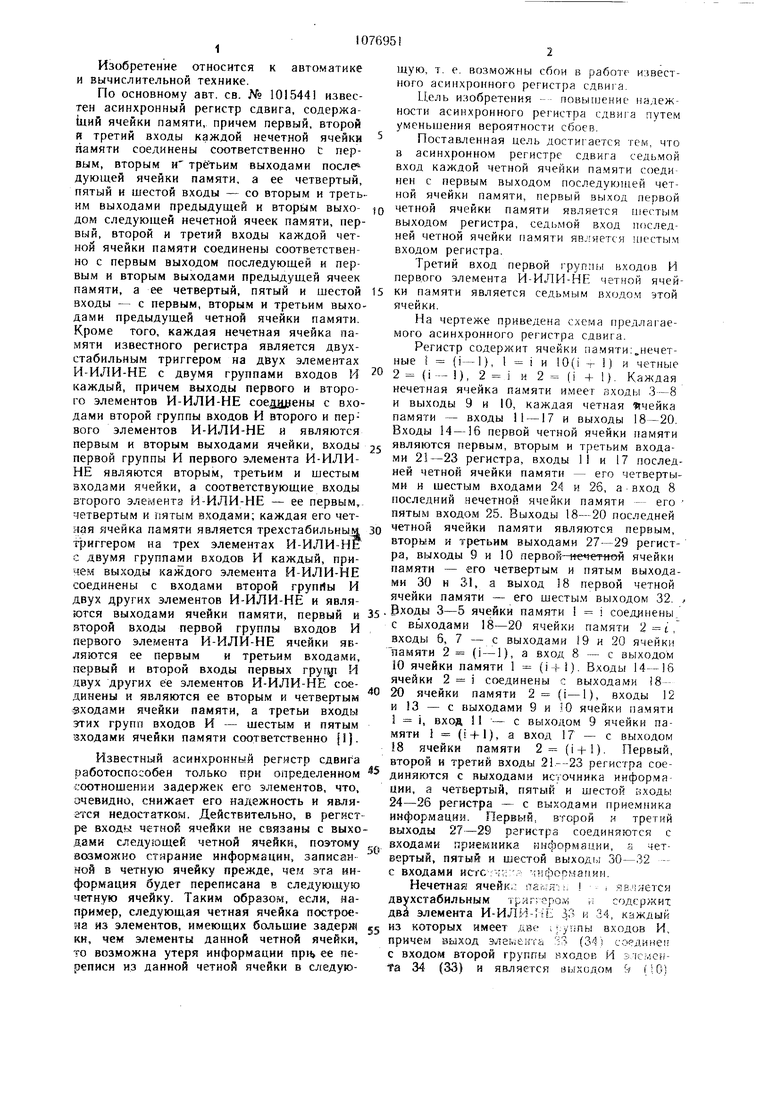

сл Изобретение относится к автоматике и вычислительной технике. По основному авт. св. № 1015441 известен асинхронный регистр сдвига, содержаШий ячейки памяти, причем первый, второй 8 третий входы каждой нечетной ячейки памяти соединены соответственно t первым, вторым и третьим выходами после дующей ячейки памяти, а ее четвертый, пятый и шестой входы - со вторым и третьим выходами предыдущей и вторым выхо- to дом следующей нечетной ячеек памяти, первый, второй и третий входы каждой четной ячейки памяти соединены соответственно с первым выходом последующей и первым и вторым выходами предыдущей ячеек памяти, а ее четвертый, пятый и шестой 15 входы - с первым, вторым и третьим выходами предыдущей четной ячейки памяти. Кроме того, каждая нечетная ячейка памяти известного регистра является двухстабильным триггером на двух элементах И-ИЛИ-НЕ с двумя группами входов И 20 каждый, причем выходы первого и второго элементов И-ИЛИ-НЕ сое,ащ1ены с входами второй группы входов И второго и первого элементов И-ИЛИ-НЕ и являются первым и вторым выходами ячейки, входы 35 первой группы И первого элемента И-ИЛИНЕ являются вторым, третьим и шестым входами ячейки, а соответствующие входы второго элемента И-ИЛИ-НЕ - ее первым,. четвертым и пятым входами; каждая его четпая ячейка памяти является трехстабильнын 30 триггером на трех элементах И-ИЛИ-НЁ с двумя группами входов И каждый, причем выходы каждого элемента И-ИЛИ-НЕ соединены с входами второй групПы И двух других элементов И-ИЛИ-НЕ и являются выходами ячейки памяти, первый и 35 второй входы первой группы входов И первого эле лента И-ИЛИ-НЕ ячейки ЯБляются ее первым и третьим входами, первый и второй входы первых груш И двух -других ее элементов И-ИЛИ-НЕ сое- „ динены и являются ее вторым и четвеотым уходами ячейки памяти, а третьи входы этих групп входов И - шестым и пятым зходами ячейки памяти соответственно J1. Известный асинхронный регистр сдвига работоспособен только при определенном соотношении задержек его элементов, что, очевидно, снижает его надежность и является недостатком. Действительно, в регистре входы четной ячейки не связаны с выходами следующей четной ячейки, поэтому возможно стирание информации, записанной в четную ячейку прежде, черл эта информация будет переписана в следующую четную ячейку. Таким образом, если, например, следуюш,ая четная ячейка построена из элементов, имеющих большие задерж gj ки, чем элементы данной четной ячейки, то возможна утеря информации при ее пеоеписн из данной четной ячейки в следующую, т. е. возможны сбои в работе известного асинхронного регистра сдвига. Цель изобретения -- ловы иение надежмости асинхронного регистра сдвига путем уменьшения вероятности сбоев. Поставленная цель достигается тем, что в асинхронном регистре сдвига седьмой вход каждой четной ячейки па.мяти соедииен с первым выходом последующей четной ячейки памяти, первый выход первой четной ячейки памяти является 1иестым выходом регистра, седьмой вход последней четной ячейки па.мяти яв.гяется иесты.м входом регистра. Третий вход первой группы входов И перв.ого элемента И-ИЛИ-НЕ четной ячеики па.мяти является седьмым входо.м этой ячейки. На чертеже приведена схема предлагаемого асинхронного регистра сдвига, Регистр содержит ячейки памяти:.нечетные I (i-1), 1 j и 10(1--) и четные 2 (i-- 1), 2 i и 2 (i + 1). Каждая нечетная ячейка памяти имеет входы 3-8 и выходы 9 и 10, каждая четная чейка памяти - входы 11 -17 и выходы 18-20. Входы 14 -16 первой четной ячейки памяти являются первым, вторым и третьим входами 21-23 регистра, входы 11 и 17 последней четной ячейки памяти - его четвертыми и шестым вхо.дами 24 и 26, а - вход 8 последний нечетной ячейки памяти - его пятым входом 25. Выходы 18--20 последней четной ячейки памяти являются первым, «торым и третьим выходами 27-29 регистР 9 и 10 пepвoк- eчeтiтои ячейки - ,f« четвертым и пятым выходаf « 31. а выход 18 первой четной еики памяти - его шестььм выходом 32. , B™№ 3-5 ячейки памяти , . соединены выходами 18-20 ячейки памяти , 67 - с выходами 9 и 20 ячейки . 2 (i-l), а вход 8 - с выходом ячейки памяти 1 ,+ 1). Входы 14-16 соединены с выходами 820 ячейки памяти 2 (s-l), входы 12 и 13 - с выходами 9 и Ш ячейки амяти ,1 .Г f ™ Г + Ь - / , выходом 18 ячейки памяти 2 (i + l). Первый, второй и третий входы 21.-23 регистра соединяются с выходами источника инфор.ма ции, а четвертый, пятый и шестой входы 24-26 регистра - с выходами прием1 ика информации. Первый, второй и третий выходы 27-29 рггистра соединяются с входами приемника информации, а четвертый, пятый и шестой выходы 30-32 - с входами исгс-ч-;г, чнгфсрна.пим. Нечетная ячейк,:: пгмя-;г, , яв.гяется двухстабильным триг:-epo,vi ,; содержит два элемента И-ИЛИ-НЕ 43 и 34, каждый которых имеет две угшы входов И, причем выход элемента (34) седине ; с входом второй группы входов И з ICMCH ta 34 (33) и является выходом м (0) ячейки памяти i, а входы его первой группы входов И - входами ,4 5 и 8 (3, 6 и 7) ячейки памяти 1 i.j Четная ячейка памяти является трехстабильным триггером и содержит три элемента И-ИЛИ-НЕ 35-37, каждый из которых имеет две группы входов И, причем выходы элементов 35-37 соединены соответственно с входами вторых групп входов И элементов 36, 37; 35, 37 и 35, 36 и являются выходами 18-20 ячейки памяти 2 1, входы первой группы входов И элемента 35 являются входами 11, 13 и 17 ячейки памяти , первый и второй вхо; ды первых групп входов И элементов 36 и 37 соединены и являютс я входами 12. и 14 ячейки памяти 2 i,a третьи входы первых групп входов И этих элементов ее входами 16 и 5 соответственно, В асинхронном регистре сдвига так же, как и в прототипе, состояния четной ячей ки памяти 2 i (значения ка ее выходах 18-20) соответствуют: О -- икформац; я стерта, 101 - записана единица. 110 записан ноль; а состояния нечетной ячейки 1 i (значения-хна ее выходах 9, 10) -10 - записана метка, О - метка стерта. Запись информации в ячейку памяти 2 происходит, как и в прототипе, если в ячейке памяти 2 (i-1) записана информация, а в ячейке памяти 1 i метка стерта. Стирание информации в ячейке памяти 2 i происходит, если в ячейке памяти 1 i записана метка, а в ячейке памяти i (1 + 1) метка стерта, чо, кроме того, при этом в ячейке памяти 2 (i-f-1) должна быть записана информация, чем и отличается функционирование предлагаемого рггвстра от функционирования прототипа. Так-м образом, в регистре инфор.мация в ячейке памяти 2 i стирается только после того, как будет переписана в ячейку памяти 2 (i-f 1). Запись метки в ячейку памяти 1 i происходит, как и в прототипе, когда в ячейку памяти 2 i записана информация, а в ячейке памяти 2 (i-I) информация стерта. Стирание метки в ячейке памяти 1 i происходит, если в ячейке памяти 2 1 информация стерта, а в ячейке памяти (i + ) записана метка. В результате каждая порция информации, помещенная источником в регистр. переписывается из каждой четной ячейки памяти в следующую четную. При этом сначала информация записывается в ячейку памяти 2 i из ячейки памяти 2 (i-I), затем, если в ячейке памяти 2(i + l) информация стерта, т. е. эта ячейка памяти готова к приему новой порции информации, в ячейку памяти 1 i записывается метка, . а в ячейку памяти 2 (i + 1) переписывается информация з ячейки памяти 2 i. Только после этого (ив этом отличие предлагаемого регнстра от прототипа) может быть стерта информация в ячейке памяти 2 i, затем; в ячейку памяти I (i -(-1) записывает-.ся метка, после чего в ячейке памяти 1 j метка стирается, в результате ячейка памяти 2 i может принять новую порцию информации из ячейки памяти 2 (i-1). Заметим, что перепись каждой порции информации из данной четной ячейки памяти в следующую четную сопровождается переписью метки из соответствующей гтечетной ячейки памяти в следующую нечетную, что и позволяет отличать соседние порции информация, помещенные в четные ячейки регистра. Задержка записи (считывания) порции информации в регистр составляет ЮГ, причерл 2Т требуется для записи информации в ячейку памяти и ВТ - для возврата ее в исходное состояние, где Т - задержка элемента И-ИЛИ-НЕ. Как уже было указано, в известном асинхронном регистре сдвига возможно стирание информации в четной ячейке памяти 2 i еще до того, как эта информация будет переписана в следующую четную ячейку памяти - 2 (i-f I), что приводит к неправильному функционированию регистра. в предлагаемом регистре стирание информации в ячейке памяти 2 i блокируется по входу 17 до тех пор, пока в ячейку памяти 2 (i-f-1) не будет записана информация, что предотвращает неправильное функционирование асинхронного регистра сдвига. Таким образом, предлагае.мый регистр, в отличие от прототипа, работоспособен при любых величинах задержек его элементов и при любом соотнощенни этих величин, и, следовательно, имеет меньщую вероятность сбоев, чем известный асинхронный регистр сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1259337A1 |

| Асинхронный регистр сдвига на МДП-транзисторах | 1986 |

|

SU1411829A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1117712A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

1. АСИНХРОННЫЙ РЕГИСТР (ЬДВИГА по авт. св. № 1015441, отмщающийся тем, что, с целью повышения надежности путем уменьшения вероятности сбоев, седьмой вход каждой четной ячейки памяти соединен с первым выходом последующей четной ячейки памяти, первый выход первой четной ячейки памяти является шестым выходом регистра, седьмой вход последней четной ячейки памяти является шестым Бходом регистра. 2. Регистр по п. 1, отличающийся тем, что третий вход первой группы входов И первого элемента И-ИЛИ-НЕ четной ячейки памяти является седьмым входом этой ячейки.

| I | |||

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1984-02-28—Публикация

1982-11-16—Подача