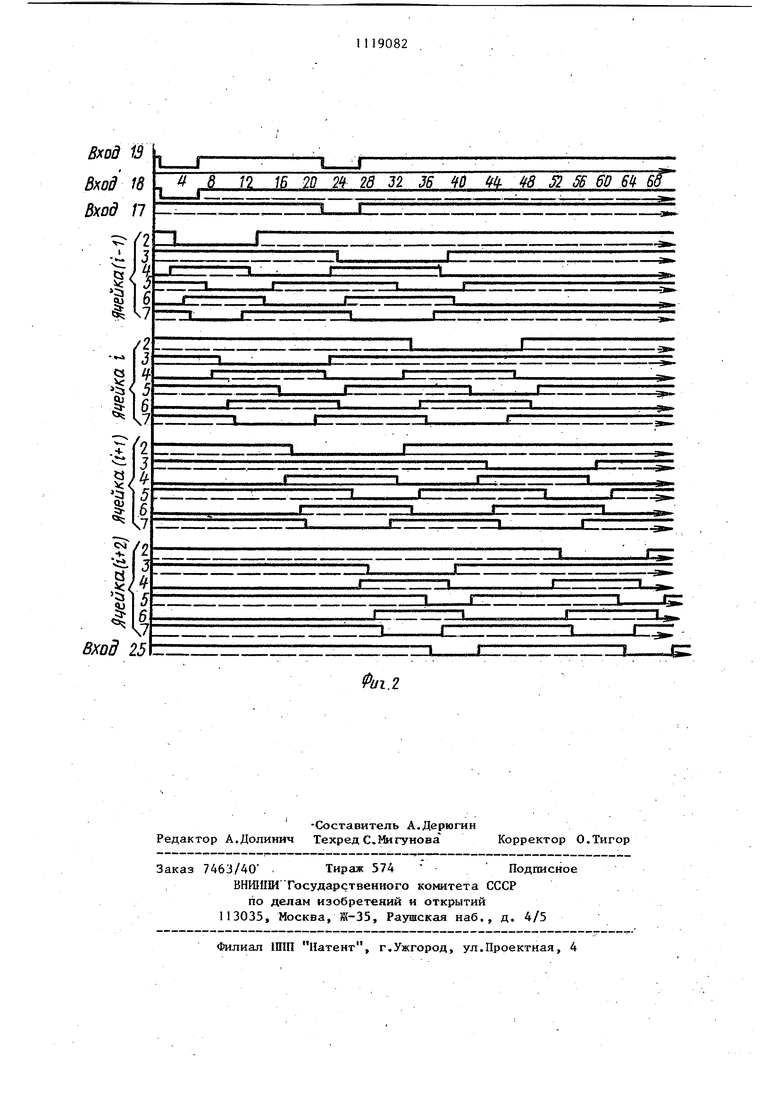

Изобретение относится к автоматике и вычислительной технике. Известен асинхронный регистр сдвига, содержащий ячейки памяти, каждая из которых выполнена по схеме трехстабильного триггера на трех элементах И-НЕ, причем два выхода трехстабильного триггера каждой ячейки соединены с двумя входами трехстабильного триггера следующей ячейки, а третий выход - с третьим входом трехстабильного триггера предьщущей ячейки 11 1. Достоверность функционирования регистра обеспечивается только при определенном соотношении задержек его элементов, что снижает, надежнос регистра и является его недостатком Наиболее близким техническим решением к данному является асинхронный регистр, содержащий ячейки памяти, каждая из которых состоит из четырех элементов И-НЕ, первый, второй и третий из которых образуют трехстабильный триггер, причем первые входы первого и второго элементов И-НЕ первой ячейки памяти являются информационными входами регистра, а(первые входы третьего и четвертого элементов И-НЕ - управ ляющим входом регистра, выходы перв го и второго элементов И-НЕ последней ячейки памяти являются информационными выходами регистра, а выход четвертого элемента И-НЕ - управляющим выходом регистра, первые входы первого и второго элементов И-НЕ i-и ячейки памяти, где 1 , П рязрядность регистра, соединены с выходами первого и второго элементов И-НЕ (1-1)-й ячейки памяти, а первый вход третьего и четвертого элементов И-НЕ i-й ячейки памяти - с выходЪм четвертого элемента И-НЕ (1-1)-й ячейки памяти, выход третьего элементаИ-НЕ каждой ячейки памяти соединен со вторым входом ее..четвертого элемента И-НЕ, два входа первого и второго элементов И-НЕ i-й ячейки и третий вход ее четвертого элемента И-НЕ соединены соответственно с выходами первого, второго и четвертого элементов И-НЕ (1+1)-й ячейки памяти, а четвертый и пятый входы четвертого элемента И-НЕ i-й ячейкипамяти - с выходами первого и второго элементов И-НЕ (Л+2)-и ячейки памяти 2J. 822 Достоинством регистра является егс высокая надежность, обеспечиваемая достоверным функционированием при любых величинах задержек его элементов,, а недостатком - избыточность оборудования. Цель изобретения - упрощение регис.тра. С этой целью в асинхронном регистре сдвига, содержащем ячейки памяти, каждая из которых состоит из четырех элементов И-НЕ, причем первые входы первого и второго, элементов И-НЕ первой ячейки памяти являются информационными входами регистра, а первые входы ее третьего и четвертого элементов И-НЕ - управляющим входом регистра, выход третьего элемента И-НЕ каждой ячейки памяти соединен со вторыми входами ее первого и второго элементов И-НЕ, выходы которых соединены перекрестными связями с их третьими входаментов И-НЕ последней ячейки памяти являются информационными выходами регистра, а выход ее -четвертого элемента И-НЕ - управляющим выходом регистра, первые входы первого и второго элементов И-НЕ м-й ячейки памяти (где , fi - разрядность регистра) соединены с выходами первого и второго элементов И-НЕ (1-1)-й ячейки памяти, а первые входы третьего и четвертого элементов И-НЕ 1-й ячейки памяти с выходом четвертого элемента И-НЕ(1-1)-й ячейки памяти , каждая ячейка памяти содержит пятый и шестой элементы И-НЕ, причем входы пятого элемента И-НЕ ка1ждой ячейки памяти соединены с выходами ее первого и второго элементов.И-НЕ, а его выход - со вторым и первым входами соответственно четвертого и шестого элементов И-НЕ, выход шестого элемента И-НЕ i-й ячейки памяти соединен со вторым входом третьего элемента И-НЕ данной ячейки памяти и вторым входом шестого элемента И-НЕ ()-м ячейки памяти, второй вход шестого элемента И-НЕ i-й ячейки памяти соединен с третьим входом четвертого Элемента И-НЕ (i-1) -и ячейки памяти и.выходом шестого элемента И-НЕ (1)-й ячейки памяти, третий вход четвертого элемента И-НЕ i-и ячейки памяти соединен со вторым входом шестого элемента И-НЕ (1+1)-й ячейки па3мяти и выходом шестого элемента И-НЕ (i+2)-fl ячейки памяти, причем выходы шестого элемента И-НЕ первой и второй ячеек памяти являются дополнительными управляющими выходами регистра, а третий и второй входы соответственно четвертого и шестого элементов И-НЕ последней ячейки являются дополнительными управляющими входами регистра. На фиг.1 приведена схема предлож ного регистраj на фиг.2 - временная диаграмма его работы. Асинхронный регистр сдвига содер жит ячейки памяти 1, каждая из кото рых имеет первый 2, второй 3, третий. 4, четвертый 5, пятый 6 и шестой 7 элементы И-НЕ. Первые входы элементов 2,3 являются информационными входами 8,9 ячейки 1, а выходы этих элементов - ее информационными выходами 10,11. Первые входы элементов 4,5 являются управляющим входом 12 ячейки I, выход элемента 5 - ее управляющим выходом 13. Выход элемента 4 соединен со вторыми входами элементов 2,3, выходы которых соединены с третьими входами друг друга и входами элемента 6, выход которого соединен со вторым входом элемента 5 и первым входом элемента 7, выход которого является дополнительным управляющим выходом 14 ячейки 1. Второй вход элемента 7 и третий вход элемента 5 являются дополнительными управляющими входами 15 и 16 соответственно ячейки Входы 8,9,12 i-й ячейки 1 соединены соответственно с выходами 10,11,13 (1-1)-й ячейки 1, а входы 15 и 16 i-й ячейки 1 - с выходами 14 ()и (1+2)-й ячеек 1. Информационные 8 и управляющий 12 входы первой ячейк 1 регистра являются его информацион ными 17,18 и управляющим 19 входами соответственно, а информационные 10,11 и управляющий 13 выходы его последней ячейки - его информационными 20,21 и управляющим 22 выходами соответственно. Дополнительные у равляющие выходы 14 первой и второй ячеек 1 регистра являются его допол твльныхми управляющимивыходами 23 и 24 соответственно, а дополнительные управляющие входы 15 и 16 соответст венно последней ячейки - его дополнительными управляющими входами 25 и 26. 2 Асинхронный регистр работает следующим образом. При наличии значения 1 на всех входах ячейки 1, последняя может находиться в одном из следующих трех устойчивых состояний (значения на выходах элементов 2 - 7)i 1 10101 - информация в ячейке стерта, 101010 и 011010 - в ячейке записана информация, причем если для четных ячеек одно из этих двух состояний соответствует единице, а второе нулю, то для нечетных - наоборот. ,Запись информации с i-ю ячейку 1 начинается в результате поступлени с выхода элемента 5 ( ячейки 1 через ее выход 13 и вход .12 i-й ячейки 1 на вход элемента 4 последней значения О, из-за чего на выходе этого элемента появляется значение 1. После этого на выходе одного из .элементов 2 или 3 t-й ячейки 1 установится значение О, затем на выходе элемента 6 - значение наконец, на выходе ее элемента 7 - значение О. Таким образом 1-я ячейка I перейдет из состояния 110101 в состояние 10 МО или 011110. После этого в результате подачи значения О с выхода элемента 7 i-й ячейки 1 через ее выход 14 на вход 15(1-1)-й ячейки Г. в последней происходит стирание информации. При этом сначала устанавливается значение 1 на выходе элемента 7 (i-i)-ft ячейки I, затем - значение. О на выходе ее элемента 4, далее на выходах обоих элементов 2,3 этой . ячейки установится значение J, после чего на выходе ее элемента 6 значение О и, наконец, на выходе ее элемента 5 - значение . Последнее через выход 13 (1-1)-й ячейки 1 и Вход 12 i-й ячейки }, поступив на вход элемента 5 последней, вызовет появление на его выходе если при этом на выходе 14 (1«-2)-й ячейки 1 имеется значение I, Таким образомj i-я ячейка окажется в состоянии 101010 или 011010 и сможет передать информацию в (1+1)-ю ячейку 1. Состояние 11 входов.7, 18 регистра соответствует отсутствию инормации, состояния 01 и .10 наличию нуля и единицы соответственно. Значение О на входе 19 регистра разрешает прием информации с его входов 17,18.и должно устанавливаться не раньше чем установится состояние 10 последних. Зна чение О на выходе 23 регистра является квитанцией о приеме им информации. По этой квитанции на входе 19 регистра может быть уст новлено значение 1, а на входах 17,18 - состояние 11. Значение 1 на выходе 24 регистра разрешает установку значения О на его входе 19, при условии, что на его входе 2 также имеется значение 1. Состояние 11 выходов 20, 21 ре гистра соответствует отсутствию информации, состояния 01 и 10 единице и нулю, в соответствии с номером последней ячейки регистра, состояние 00 на этих входах не возникает. Значение О на выходе 22 регистра разрешает считывание ин формации с его выходов 20, 21 и устанавливается после появления состояния 01 или 10 этих выходов. Значение О на входе 25 регистра я ляется квитанцией о приеме информ ции с его выходов. По этой квитанции на выходе 22 регистра устанавливается значение 1, а на выходах 20, 21 - состояние П. Значение 1 на входе 26 регистра разрешает установку значения О на ег выходе 22, при условии, что на его входе 25 также имеется значение 1 Функционирование регистра пр пр хождении через.него последовательности 101 представлено временной диаграммой фиг.2. В исходном состоя нии (такт № 0) информация во всех ячейках регистра стерта. Диаграмма построена. в предположении, что задержки всех элементов регистра равны Т . На входе 26 регистра, введенном в его состав для унификации входного и выходного интерфейса, зафиксировано значение 1,

25 26 разрешающее изменение значений на его выходе 22. Поэтому значения на входе 26 регистра в диаграмме не приводятся. Из временной диаграммы видно, что быстродействие регистра (время между последовательными записями информации в регистр) составляет 26 С если очередная запись происходит в такте № 23, то следующая может произойти не раньше, чем в .такте № 49. При этом минимальная длительность сигнала на входе 19 регистра (значение О на этом входе) составляет 5 -I , соответственно интервал между сигналами на этом входе (т.е. значение 1 на нем) составляет 21f . Для сигнала на входе 25 регистра эти величины равны 6 С и 20 f соответственно.. Из функционирования асинхронного регистра следует, что в процессе записи и последующего стирания информации в каждой его ячейке памяти все элементы переключаются последовательно. Это обеспечивает достоверное функционирование реги.стра при любых величинах задержек его элементов. Предложенное техническое решение упрощает асинхронный сдвиговый peгиctp по сравнению с прототипом, так как реализация предложенного регистра требует более экономичных (двух и трехвходовых) элементов И-НЕ, чем реализация прототипа, требующая использования пятивходовых элементов И-НЕ. Оценивая сложность реализации суммарным числом входов элементов, составляющих одну ячейку, получим соответствено 15 у предложенного регистра, против 18 у известного регистра, что подтверждает достижение поставленной цели изобретения .

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный регистр сдвига | 1982 |

|

SU1117712A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1383444A1 |

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

АСИНХРОННЫЙ РЕГИСТР СДВИГА, содержащий ячейки .памяти, каждая из которьпс состоит из четырех элементов И-НЕ,причем первые входы первого и .второго элементов И-НЕ первой ячейки памяти являются информационными входами регистра,а первые входы ее третьего и четвертого элементов И-НЕ управляющим входом регистра, выход третьего элемента И-НЕ каждой ячейки памяти соединен со вторыми входами ее первого и второго элементов. И-НЕ, выходы которых соединены перекрестными связями с их третьими входами, выходы первого и второго элементов. И-НЕ последней ячейки памяти являются информационными выходами регистра, а выход ее четвертого элемента И-НЕ - управляющим выходом регистра, первые входы первогои второго элементов И-НЕ Н-й ячейки памяти соединены с выходами первого и второго элементов И-НЕ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВСЕСОЮЗНАЯ | 0 |

|

SU374663A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Асинхронный регистр сдвига | 1978 |

|

SU728161A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-10-15—Публикация

1982-04-15—Подача