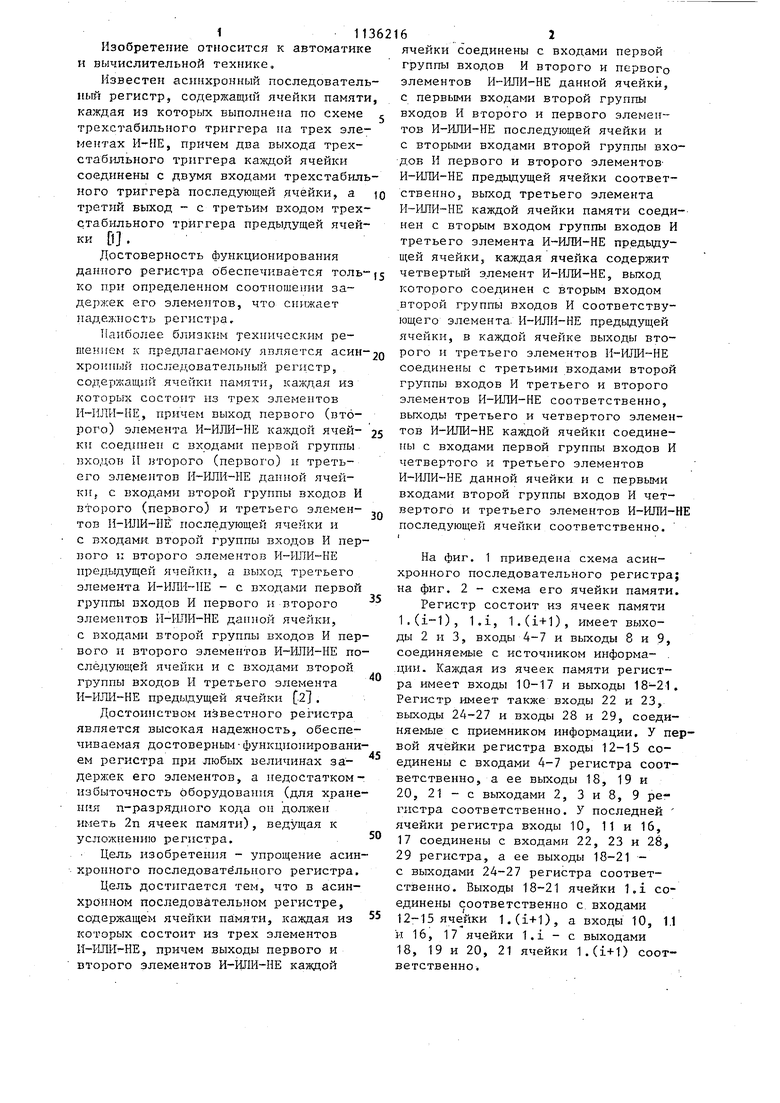

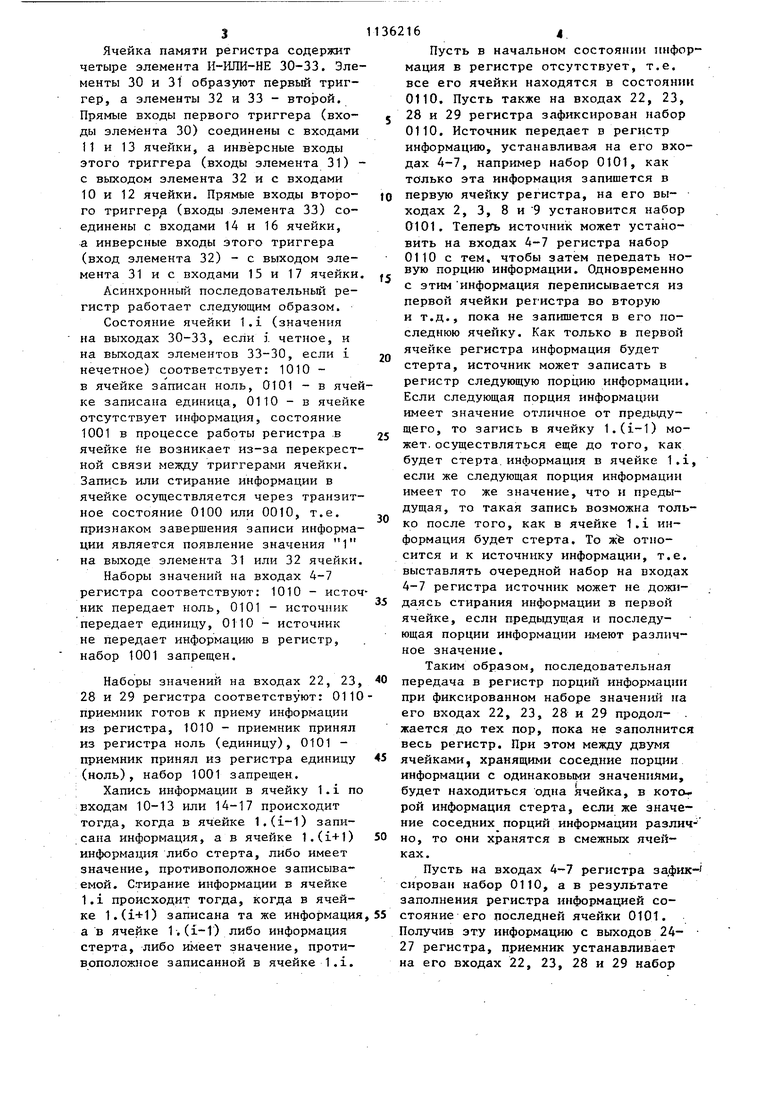

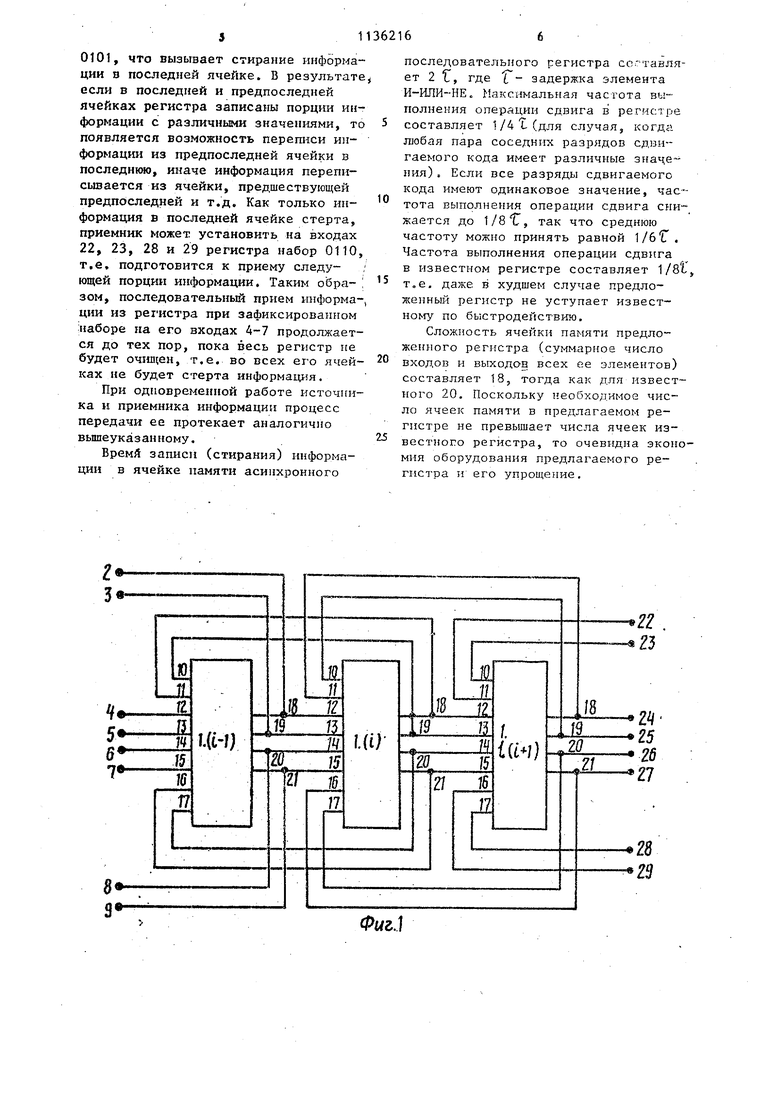

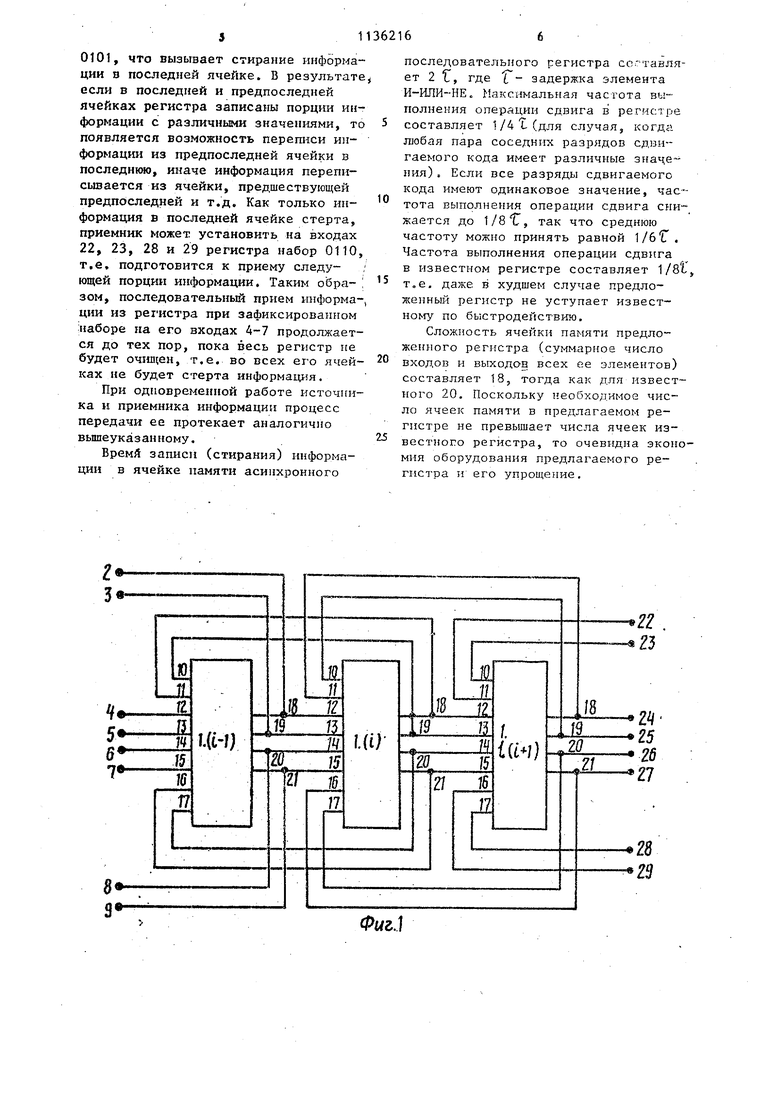

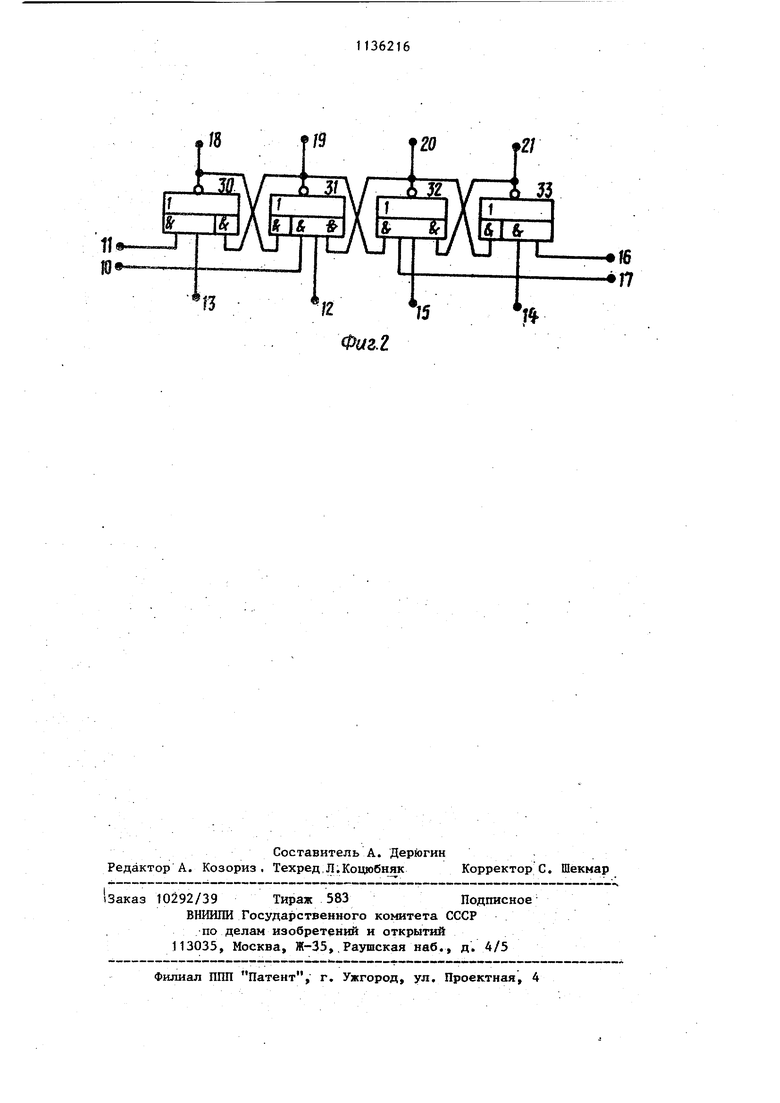

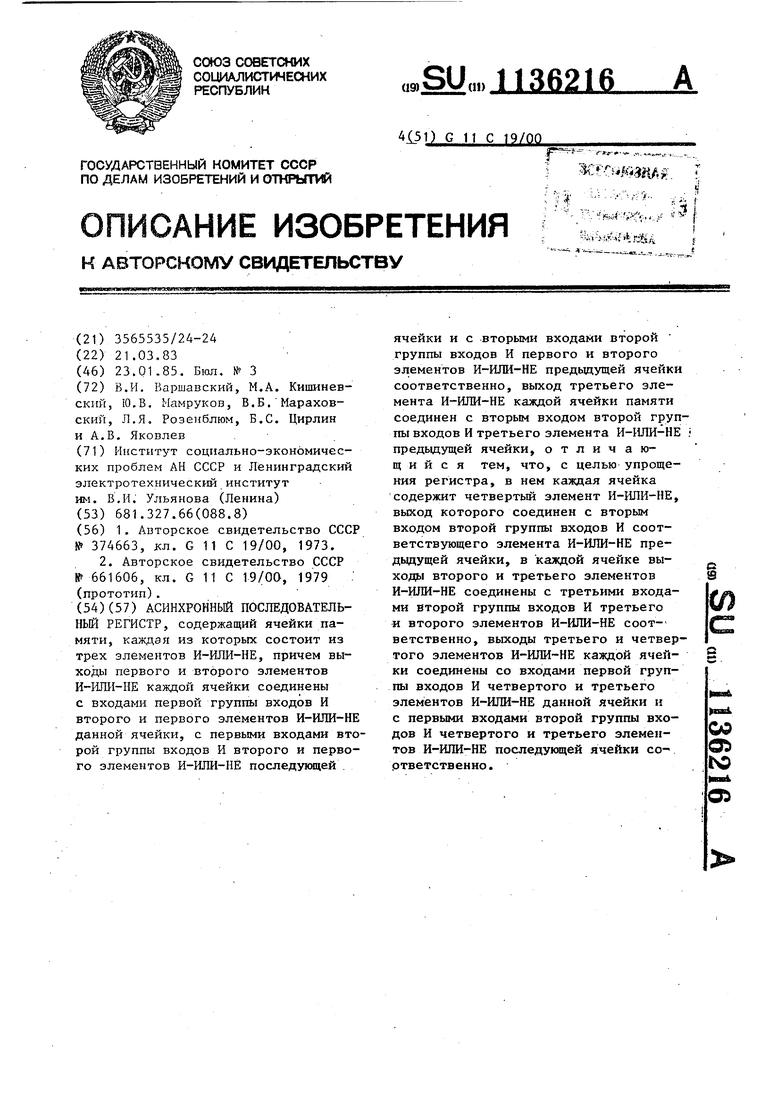

11 Изобретение относится к автоматик и вычислительной технике. Известен асинхронный последовател ный регистр, содержащий ячейки памят каждая из которых выполнена по схеме трехстабильного триггера на трех эле ментах И-ПЕ, причем два выхода трехстабильного триггера калодой ячейки соединены с двумя входами трехстабил ного триггера последующей ячейки, а третий выход с третьим входом трех стабильного триггера предыдущей ячей ки 0. Достоверность функционирования данного регистра обеспечивается толь ко при определенном соотношении задержек его элементов, что снижает пггдежность регистра Наиболее близким теунтчсским решением к предлагаемому является асин хронный последовательный регистр, содержащий ячейки памяти, каждая из которых состоит из трех элементов , причем выход первого (второго) элемента И-ИЛИ-НЕ ка}кдой ячейки соединен с входами первой группы входов И второго (первого) и третьего элементов И ИЛИ-НЕ дапно1{ ячейки, с входами второй группы входов И второго (первого) и третьего элементов И-Ш1И-Г1К последующей ячейки и с входами, второй группы входов И пер вого i: второго элементов И-ИЛИ-НЕ предыдущей ячейки, а выход третьего элемента И-ШШ-НЕ - с входами первой группы входов И первого и второго элементов ИЧ-ШИ-НЕ данной ячейки, с входами второй группы входов И пер вого и BTopoio элементов И-ИЛИ-НЕ по следующей ячейки и с входами второй группы входов И третьего элемента И-ИЛИ-НЕ предг щущей ячейки -21. Достоинством известного регистра является высокая надежность, обеспечиваемая достоверньп«1 функционировани ем регистра при любых величинах задержек его элементов, а недостатком избыточность оборудования (для хране ния п-разрядного кода он должен иметь 2п ячеек памяти), ведущая к усложнению регистра. . Цель изобретения - упрощение асин хронного последовательного регистра. Цель достигается тем, что в асинхронном последовательном регистре, содержащем ячейки , каждая из которых состоит из трех элементов Н-ИЛРГ-НЕ, причем выходы первого и второго элементов И-ЩШ-НЕ каждой 62 ячейки соединены с входами первой группы входов И второго и первого элементов И-1-ШИ-НЕ данной ячейки, с первыми входами второй группы входов И второго и первого элементов И-ИЛИ-НЕ последующей ячейки и с вторыми входами второй группы входов И первого и второго элементовИ-ИЛИ-НЕ предыдущей ячейки соответственно, выход третьего элемента И-МИ-НЕ каждой ячейки памяти соеди-нен с вторым входом группы входов И третьего элемента И-ИЛИ-НЕ предьщущей ячейки, каждая ячейка содержит четвертый элемент И-ИЛИ-НЕ, выход которого соединен с вторым входом второй группы входов И соответствующего элемента. И-ИЛИ-НЕ предьщущей ячейки, в каждой ячейке выходы второго и третьего элементов И- ШИ-НЕ соединены с третьими входами второй группы входов И третьего и второго элементов И-ИЛИ-НЕ соответственно, выходы третьего и четвертого элементов И-ИЛИ-НЕ каждой ячейки соединены с входами первой группы входов И четвертого и третьего элементов И-ИЛИ-НЕ данной ячейки и с первыми входами второй группы входов И четвертого и третьего элементов И-ИЛИ-НЕ последующей ячейки соответственно. На фиг. 1 приведена схема асинхронного последовательного регистра; на фиг. 2 - схема его ячейки памяти. Регистр состоит из ячеек памяти l.(i-l), l.i, 1.(i+1), имеет выходы 2 и 3, входы 4-7 и выходы 8 и 9, соединяеь1ые с источником информа- . ции. Каждая из ячеек памяти регистра имеет входы 10-17 и выходы 18-21. Регистр имеет также входы 22 и 23, выходы 24-27 и входы 28 и 29, соединяемые с приемником информации. У первой ячейки регистра входы 12-15 соединены с входами 4-7 регистра соответственно, а ее выходы 18, 19 и 20, 21 - с выходами 2, 3 и 8, 9 регистра соответственно. У последней ячейки регистра входы 10, 11 и 16, 17 соединены с входами 22, 23 и 28, 29 регистра, а ее выходы 18-21 с выходами 24-27 регистра соответственно. Выходы 18-21 ячейки l.i соединены соответственно с входами 12-15 ячейки 1.(i+1), а входы 10, 1.1 и 16, 17 ячейки 1.1 - с выходами 18, 19 и 20, 21 ячейки 1.(i+1) соответственно. 3 Ячейка памяти регистра содержит четыре элемента Н-ИЛИ-НЕ 30-33. Эле менты 30 и 31 образуют первый триггер, а элементы 32 и 33 - второй. Прямые входы первого триггера (входы элемента 30) соединены с входами 11 и 13 ячейки, а инверсные входы этого триггера (входы элемента 31) с выходом элемента 32 и с входами 10 и 12 ячейки. Прямые входы второго триггера (входы элемента 33) соединены с входами 14 и 16 ячейки, а инверсные входы этого триггера (вход элемента 32) - с выходом элемента 31 и с входами 15 и 17 ячейки Асинхронный последовательный регистр работает следующим образом. Состояние ячейки 1.1 (значения на выходах 30-33, если 1 четное, и на выходах элементов 33-30, если i нечетное) соответствует: 1010 в ячейке записан ноль, 0101 - в яче ке записана единица, 0110 - в ячейк отсутствует информация, состояние 1001 в процессе работы регистра .в ячейке Не возникает из-за перекрест ной связи между триггерами ячейки. Запись или стирание информации в ячейке осуществляется через транзит ное состояние 0100 или 0010, т.е. признаком завершения записи информа ции является появление значения 1 на выходе элемента 31 или 32 ячейки Наборы значений на входах 4-7 регистра соответствуют: 1010 - исто ник передает ноль, 0101 - источник передает единицу, 0110 - источник не передает информацию в регистр, набор 1001 запрещен. Наборы значений на входах 22, 23 28 и 29 регистра соответствуют: 011 приемник готов к приему информации из регистра, 1010 - приемник принял из регистра ноль (единицу), 0101 приемник принял из регистра единицу (ноль), набор 1001 запрещен. Хапись информации в ячейку 1.i п входам 10-13 или 14-17 происходит тогда, когда в ячейке 1.(i-1) записана информация, а в ячейке 1.(i+1) информация либо стерта, либо имеет значение, противоположное записываемой. Стирание информации в ячейке 1.1 происходит тогда, когда в ячейке l.(i-t-l) записана та же информация а в ячейке Г. (1-1) либо информация стерта, либо имеет значение, противоположное записанной в ячейке 1.1. 164 Пусть в начальном состоянии информация в регистре отсутствует, т.е. все его ячейки находятся в состоянии 0110. Пусть также на входах 22, 23, 28 и 29 регистра зафиксирован набор 0110. Источник передает в регистр информацию, устанавлива-я на его входах 4-7, например набор 0101, как только эта информация запишется в первую ячейку регистра, на его выходах 2, 3, 8 и 9 установится набор 0101. Тепергь источник может установить на входах 4-7 регистра набор 0110 с тем, чтобы затем передать новую порцию информации. Одновременно с этим информация переписывается из первой ячейки регистра во вторую и т.д., пока не запишется в его последнюю ячейку. Как только в первой ячейке регистра информация будет стерта, источник может записать в регистр следующую порцию информации. Если следующая порция информации имеет значение отличное от предыдущего, то запись в ячейку 1.(1-1) может, осуществляться еще до того, как будет стерта, информация в ячейке 1.1, если же следующая порция информации имеет то же значение, что и предыдущая, то такая запись возможна только после того, как в ячейке 1.1 информация будет стерта. То же относится и к источнику информации, т.е. выставлять очередной набор на входах 4-7 регистра источник может не дожидаясь стирания информации в первой ячейке, если предьщущая и последующая порции информации имеют различное значение. Таким образом, последовательная передача в регистр порций информации при фиксированном наборе значений на его входах 22, 23, 28 и 29 продол- . жается до тех пор, пока не заполнится весь регистр. При этом между двумя ячейками, хранящими соседние порции информации с одинаковыми значениями, будет находиться одна ячейка, в кото рой информация стерта, если же значение соседних порций информации различно, то они хранятся в смежных ячейках. Пусть на входах 4-7 регистра за.фиксироваи набор 0110, а в результате заполнения регистра информацией состояние его последней ячейки 0101. Получив эту информацию с выходов 2427 регистра, приемник устанавливает на его входах 22, 23, 28 и 29 набор

0101, что вызывает стирание информации в последней ячейке. В результате если в последней и предпоследней ячейках регистра записаны порции информации с различньми значениями, то появляется возможность переписи информации из предпоследней ячейки в последнюю, иначе информация переписьюается из ячейки, предшествующей предпоследней и т.д. Как только информация в последней ячейке стерта, приемник может установить на входах 22, 23, 28 и 29 регистра набор 0110, т.е. подготовится к приему следующей порции информации. Таким образон, последовательньй прием инфорнации из регистра при зафиксированном наборе на его входах 4-7 продолжается до тех пор, пока весь регистр не будет оч1щен, т.е. во всех его ячейках не будет стерта информащш.

При одновременной работе источника II приемника информации процесс передачи ее протекает аналогично вьппеуказанному.

Времй записи (стирания) информации в ячейке памяти асинхронного

последовательного регистра ссгтавляет 2 С, где Г задержка элемента И-ИЛИ-НЕ. Максимальная частота выполнения операции сдвига в регистре составляет 1/41 (для случая, когда любая пара соседних разрядов сдвигаемого кода имеет различьгые значе- ния). Если все разряды сдвигаемого кода имеют одинаковое значение, частота выполнения операции сдвига снижается до 1/81Г, так что среднюю частоту можно принять равной 1/6Г. Частота выполнения операции сдвига в известном регистре составляет 1/8t т,е. даже в худшем случае предложенный регистр не уступает известноьгу по быстродействию.

Сложность ячейки памяти предложенного регистра (суммарное число входов и выходов всех ее элементов) составляет 18, тогда как для известного 20, Поскольку необходимое число ячеек памяти в предлагаемом регистре не превышает числа ячеек известного регистра, то очевидна экономия оборудования предлагаемого регистра и его упрощение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Асинхронный регистр сдвига на МДП-транзисторах | 1986 |

|

SU1411829A1 |

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1076951A2 |

| Асинхронный последовательный регистр | 1985 |

|

SU1372361A1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный последовательный регистр | 1990 |

|

SU1805501A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

АСИНХРОННЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ РЕГИСТР, содержащий ячейки памяти, каждая из которых состоит из трех элементов И-ИЛИ-НЕ, причем выходы первого и второго элементов И-ИЛИ-НЕ каждой ячейки соединены с входами первой групгш входов И второго и первого элементов И-ИЛИ-НЕ данной ячейки, с первыми входами второй группы входов И второго и первого элементов И-ИЛИ-НЁ последующей . ячейки и с вторыми входами второй группы входов И первого и второго элементов И-ИЛИ-НЕ предьщущей ячейки соответственно, выход третьего элемента И-ИЛИ-НЕ каждой ячейки памяти соединен с вторым входом второй группы входов И третьего элемента И-ИЛИ-НЕ предыдущей ячейки, отличающийся тем, что, с целью упрощения регистра, в нем каждая ячейка содержит четвертый элемент И-ИЛИ-НЕ, выход которого соединен с вторым входом второй группы входов и соответствующего элемента И-ШШ-НЕ предьщущей ячейки, в каждой ячейке вы§ ходы второго и третьего элементов И-ИЛИ-НЕ соединены с третьими входами второй группы входов И третьего и второго элементов И-ШШ-НЕ соответственно, выходы третьего и четвертого элементов И-ИЛИ-НЕ каждой ячейки соединены со входами первой группы входов И четвертого и третьего элементов И-ШШ-НЕ данной ячейки и с первыми входами второй группы вхоОд дов И четвертого и третьего элеменOl тов И-ШШ-НЕ последукнцей ячейки соIsD ртветственно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВСЕСОЮЗНАЯ | 0 |

|

SU374663A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ячейка памяти для буферного регистра | 1976 |

|

SU661606A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-01-23—Публикация

1983-03-21—Подача