1

Изобретение относится к автоматике и вычислительной технике.

Известен асинхронный регистр сдви га, содержащий ачейки памяти, каждая из которых выполнена по схеме трехстабильноро триггера на трёх элементах И-НЁ, причем два выхода трехстабильного триггера каждой ячейки соединены с двумя входами трехстабильного триггера следующей ячейки, а третий выход - с третьим входом трехстабильного триггера предыдущей ячейки lj .

Однако.достоверность функционирования регистра обеспечивается только при определенном соотношении задержек его элементов, что снижает надежность регистра.

Наиболее близким к изобретению по технической сущности является асинхронный регистр сдвига, содержащий .ячейки памяти, каждая из которьк состоит из четырех элементов И-НЕ, первый, второй и третий из которых образуют трехстабильный т|эиггер,

.причем первые входы первого и второго элементов И-НЕ первой ячейки памяти являются информационными входами регистра, а первые входы третье го и четвертого элементов И-НЕ управляющим входом регистра, выходы первого и второго элементов И-НЕ последней ячейки йамяти являются информационными выходами регистра, а выход четвертого элемента И-НЕ - управляющим выходом регистра, первые входы первого и второго элементов И-НЕ ( -и ячейки памяти соединены с выходами первого и второго элементов И-НЁ )-Й1 ячейки памяти,(Где 1 $ i 6 П , и - разрядность регистра, а первый вход-третьего и четвертого элементов И-НЕ н -и ячейки памяти со.единен с выходом четвертого элемента И-НЕ ( 1 -1)-й ячейки памяти, выход третьего элемента И-НЕ каждой ячейки памяти соединен с вторым входом ее четвертого элемента И-НЕ, две. входа первого и второго элементов И-НЕ «-и ячейки и третий вход ее четвертого элемента И-НЕ соединены соответственно с выходами первого,

, второго и четвертого элементов И-НЕ (1 +1)-й ячейки памяти, а четвертый и пятьй вхйды четвертого элемента

И-НЕ 1 -и ячейки памя.ти - с выходами первого и второго элементов И-НЕ { 2)-й ячейки памяти. Регистр обладает высокой надежностью, обеспе17712-2

чиваемой достоверным функционированием регистра при любых величийах задержек его элементов 2.

Недостатком известного устройства является избыточность оборудования, ведущая к усложнению регистра.

Цель, изобретения - упрощение асинхронного регистра сдвига.

С этой целью в асинхронном реJO гистре сдвига, содержащем ячейки памяти, каждая из которых состоит из четырех элементов И-НЕ, причем первые входы первого и второго элементов И-НЕ первой ячейки памяти являют j ся информационными входами регистра, а первые входы ее третьего и четвертого элементов И-НЕ - первым управляющим входом регистра, выход третьего элемента И-НЕ каждой ячейки

2Q соединен с вторыми входами ее первого и второго элементов И-НЕ, выходы которых соединены перекрестными связями с их третьими входами, выходы первого и второго элементов

25 И-НЕ последней ячейки памяти являются информационными выходами регистра, а выход ее четвертого элемента И-НЕ - первым управляющим выходом регистра, первые входы первого и второго элементов И-НЕ i -и ячейки памяти соединены с выходами первого и второго элементов И-НЕ (i -1)-й ячейки памяти (1 -1 .п , П разрядность регистра), первые входы третьего и четвертого элементов

35 И-НЕ i -и ячейки памяти соединены с выходом четвертого элемента И-НЕ ( i -1)-й ячейки памяти, а второй вход четвертого элемента И-НЕ i -и ячейки памяти соединен с выходом

0 четвертого элемента И-НЕ ( +1)-й ячейки памяти, при этом выход четвертого элемента И-НЕ первой ячейки памяти является вторым управляющим выходом регистра, а второй вход четвертого элемента И-НЕ последней ячейки памяти - вторым управляющим входом регистра, каждая ячейка памяти содержит пятый и шестой элементы И-НЕ, причем входы пятого

50 элемента И-НЕ каждой ячейки соединены с выходами ее первого и второго элементов И-НЕ,а выход этого элемента - с третьим и первым входами соответственно четвертого и шестого

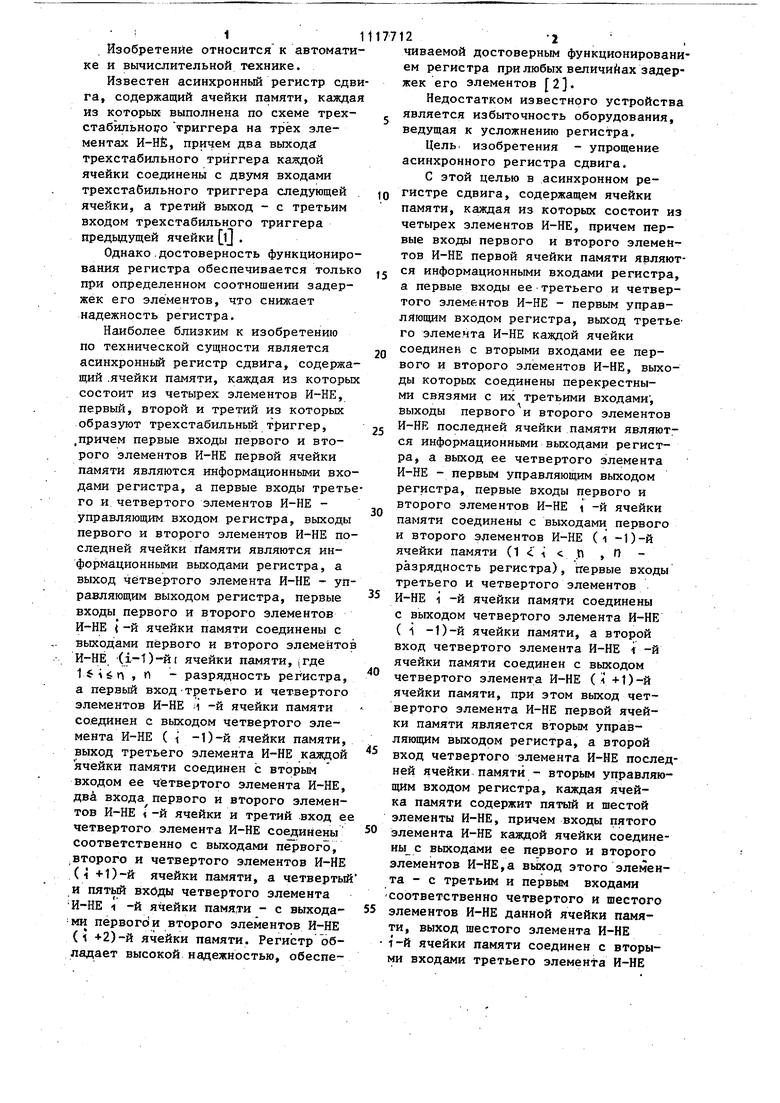

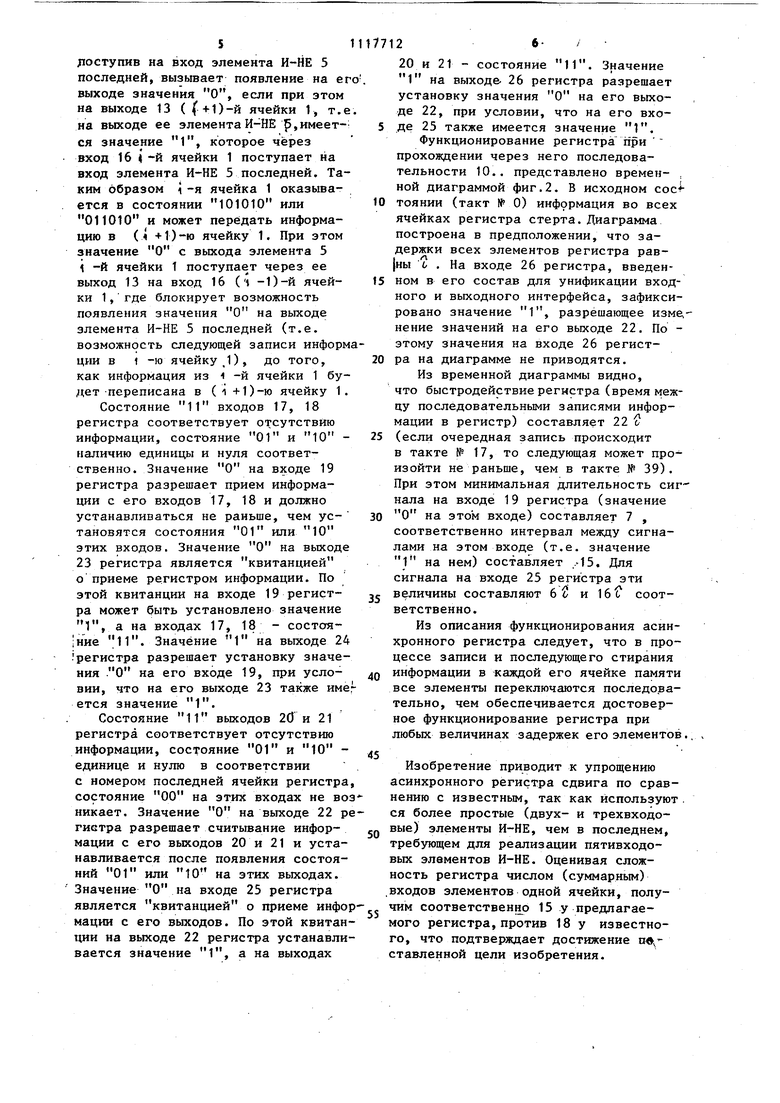

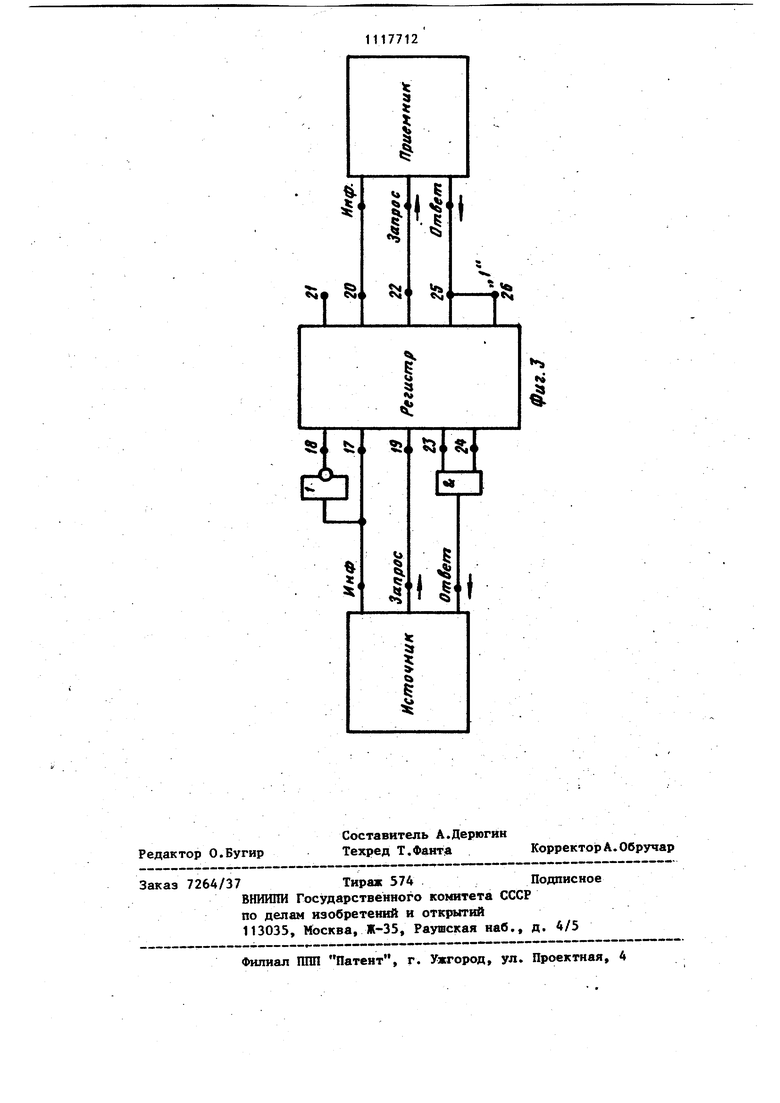

55 элементов И-НЕ данной ячейки памяти, выход шестого элемента И-НЕ i-й ячейки памяти соединен с вторыми входами третьего элемента И-НЕ 31 t-й ячейки памяти и шестого элемента И-НЕ ( 1.-1)-й ячейки памяти, второй вход шестого элемен- а И-НЕ -и ячейки памяти соединен с выходом шестого элемента И-НЕ (1+1)-й ячейки памяти при этом выход шестого элемента И-НЕ первой ячейки памяти является третьим управляющим выходом регистра, а второй вход шестого элемента И-НЕ последней ячейки памяти третьим управляющим .входом регистра. На фиг.1 приведена схема/предлагаемого регистра; на фиг.2 - временная диаграмма его работы; на фиг.З пример подключения предлагаемого регистра к источнику и приемнику информации, работающим в режиме эапросответ. Асинхронный регистр сдвига содержит ячейки 1 памяти, каждая иэ которых имеет первый 2, второй 3, третий 4, четвертый 5, пя.тый 6 и шестой 7 элементы И-НЕ. Первые входы элементов Й-НЕ 2 и 3 являются информационными входами б и 9 ячейки 1, а выходы этих элементов - ее информационными выходами 10 и 11. Первые входы элементов И-НЕ 4 и 5 являются первым управляющим входом 12 ячейки 1, выход элемента И-НЕ 5 - ее первым управляющим выходом 13. Выход элемента И-НЕ4 соединен с вторыми входами элементов И-НЕ 2 и 3, выходы которьк соединены с третьими входами друг друга и входами: элемента И-НЕ 6, выход которого соединен с третьим входом элемента И-НЕ 5 и- первым входом элемента И-НЕ 7, выход которого соединен с вторым входом элемента И-НЕ 4 ц.вляется вторым управляющим выходом 14 ячейки 1. Вторые входы элементов И-НЕ 7 и 5 являются третьим 15 и вторым 16 управляющими входами ячейки 1. Входы 8,9 и 12 i -и ячейки 1 соединены соответственно с выходами 10, 11 и 13 ( -1)-й ячейки 1, а входы 15 и 16 1-й ячейки 1 - с выходами 13 и 14 соответственно (t 1)-й ячейки 1. Инфр1 ационные 8 и 9 и первый управляющий 12 входы первой ячейки 1 регистра являются его информационными 17 и 18 и первым управляющим 19 входами, а информационные 10 и 11 и управляющий 13 (первый) выходы последней ячейки регистра являются его информационны 4и 20 и 21 ff перв управляющим 22.выходами.Пер124вый 13 и второй 14 управляющие выходы первой ячейки регистра являются его вторым 24 и третьим 23 управляющими выходами, а третий 15 и второй 16 управляющие входы последней ячейки регистра являются его третьим 25 и вторым 26 управляющими входами. Асинхронный регистр работает следующим обраэом.. При наличии значения 1 на всех I входах ячейки 1 последняя может, нахоДиться в одном из следующих трех ус ойчивых состояний (значения, на выходах элементов 2,3,4,5,6,7 ячейки 1): 110101 - информация в ячeйJкe стер,та, 101010 и 011010 - в ячейке записана информация, причем, если для четных ячеек одно из этих двух , состояний соответствует единице. а второе нулю, то для нечетных наоборот.. Запись информации в i -ю ячейку 1 начинается в результате поступления с выхода элемента И-НЕ 5 ( i -1)-й ячейки 1 через ее выход 13 на вход 12 -и ячейки 1 и далее на вход ее элемента И-НЕ 4 значения О, из-эа чего на выходе этого элемента появ- , ляется значение 1. После этого на выходе одного из элементов И-НЕ 2 или 1-й ячейки 1 устанавливается значение О, затем на выходе ее элемента И-НЕ 6 - значение 1 и, наконец, на выходе ее элемента И-НЕ 7 значение О, если при этрм на входе 15 этой ячейки также имеется значение 1, куда это значение поступает с выхода элемента И-НЕ 7 (+1)-й ячейки через ее выход 14. Таким образом 1-я ячейка 1 переходит из состояния 110101 в состояние 101110 или 011110. После этого, в результате поступления зн ачения G с выхода элемента И-НЕ 7 1 -и ячейки 1 через ее выход 14 на вход 15 ( i -1)-й ячейки 1, в последней происходит стирание информации. При этом сначала устанавливается значение 1 на выходе элемента И-НЕ 7 ( -1)-й ячейки 1, затем значение О на выходе ее элемента И-НЕ 4, далее на выходах обоих элементов 2 и 3 этой я:чейки устанавливается значение 1, после чего на выходе ее элемента И-НЕ 6 значение О и, наконец, на выходе ее элемента И-НЕ 5 - значение Г. Последнее через выход 13 ( i -1)-й ячейки 1 и вход 12 (-и ячейки 1,

5

лоступив на вход элемента И-НЕ 5 последней, вызьгоает появление на ег выходе значения О, если при этом на выходе 13 ( (+1)-й ячейки 1, т.е на выходе ее элемента И-НЕ р,имеет-ся значение 1, которое через вход 164-й ячейки 1 поступает на вход элемента И-НЕ 5 последней. Таким образом i-я ячейка 1 оказывается в состоянии 101010 или 011010 и может передать информацию в (л -fD-ro ячейку 1. При этом значение О с выхода элемента 5 i -и ячейки 1 поступает через ее выход 13 на вход 16 (ч -1)-й ячейки 1 , где блокирует возможность появления значения О на выходе элемента И-НЕ 5 последней (т.е. возможность следующей записи информции в 1 -ю ячейку J), до того, как информация из i -и ячейки 1 будет -переписана в (i +1)-ю ячейку 1.

Состояние 11 входов 17, 18 регистра соответствует отсутствию информации, состояние 01 и 10 наличию единицы и нуля соответственно. Значение О на входе 19 регистра разрешает прием информации с его входов 17, 18 и должно устанавливаться не раньше, чем установятся состояния 01 или 10 этих входов. Значение О на выходе 23 регистра является квитанцией о приеме регистром информации. По этой квитанции на входе 19 регистра может быть установлено значение 1, а на входах 17, 18 - состоя|ние 11. Значение 1 на выходе 24 регистра разрешает установку значения О на его входе 19, при условии, что на его выходе 23 также име ется значение 1.

Состояние 11 выходов 20 и 21 регистра соответствует отсутствию информации, состояние 01 и 10 единице и нулю в соответствии с номером последней ячейки регистра состояние 00 на этих входах не во никает. Значение О на выходе 22 ргистра разрешает считывание информации с его выходов 20 и 21 и устанавливается после появления состояний 01 или 10 на этих выходах. Значение О на входе 25 регистра является квитанцией о приеме инфомации с его выходов. По этой квитанции на выходе 22 регистра устанавливается значение 1, а на выходах

77126- /

20 и 21 - состояние 11. Значение 1 на выходе 26 регистра разрешает установку значения О на его выходе 22, при условии, что на его вхо5 де 25 также имеется значение Г.

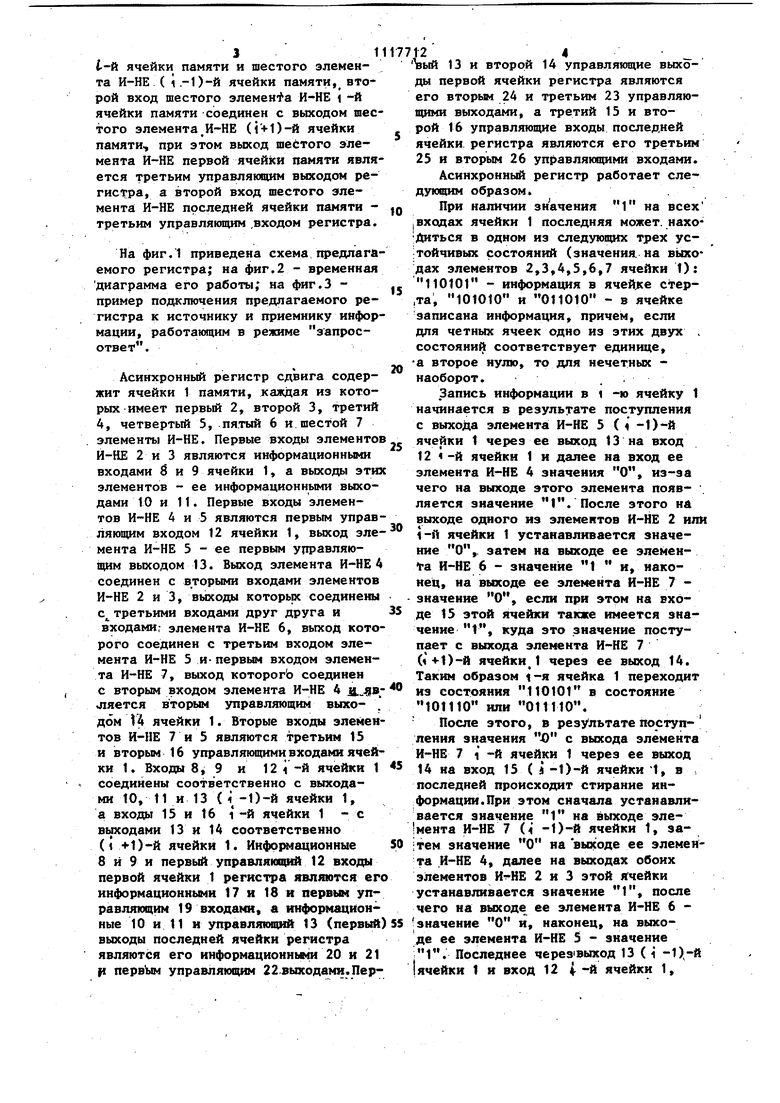

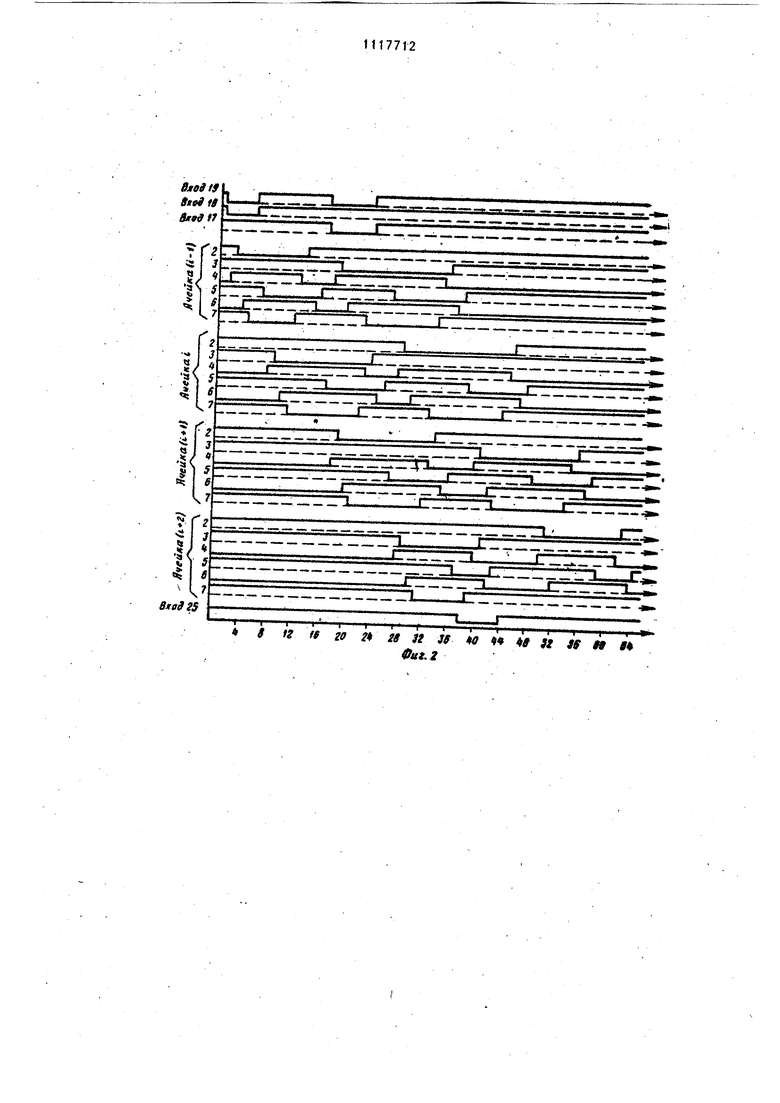

Функционирование регистра при прохождении через него последовательности 10.. представлено времен- , ной диаграммой фиг. 2. В исходном тоянии (такт № 0) инфррмация во всех ячейках регистра стерта. Диаграмма построена в предположении, что задержки всех элементов регистра рав|ны 6 . На входе 26 регистра, введен15 ном в его состав для унификации входного и выходного интерфейса, зафиксировано значение 1, разрешающее изме,нение значений на его выходе 22. По этому значения на входе 26 регист20 ра на диаграмме не приводятся.

Из временной диаграммы видно, что быстродействие регистра (время межцу последовательными записями информации в регистр) составляет 22 с)

5 (если очередная запись происходит

в такте № 17, то следующая может произойти не раньше, чем в такте № 39). При этом минимальная длительность сигнала на входе 19 регистра (значение

0 О на этом входе) составляет 7 , соответственно интервал между сигналами на этом входе (т.е. значение 1 на нем) составляет .-15. Для сигнала на входе 25 регистра эти

J величины составляют 6 С и 16с соответственно.

Из описания функционирования асинхронного регистра следует, что в процессе записи и последующего стирания

0 информации в каждой его ячейке памяти все элементы переключаются последовательно, чем обеспечивается достоверное функционирование регистра при любых величинах задержек его элементов.

Изобретение приводит к упрощению

асинхронного регистра сдвига по сравнению с известным, так как используют . ся более простые (двух- и трехвходоQ вые) элементы И-НЕ, чем в последнем, требующем для реализации пятивходовых элементов И-НЕ. Оценивая сложность регистра числом (суммарным) .входов элементов одной ячейки, получим соответственно 15 у предлагаемого регистра, против 18 у известного, что подтверждает достижение ЕИ ставленной цели изобретения.

«ч

Вяо919 Bttiie вквдП

ВяаЗгЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1383444A1 |

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

АСИНХРОННЫЙ РЕГИСТР СДВИГА, содержащий ячейки памяти, каждая из которых состоит из четырех элемен- , трв И-НЕ, причем первые входы первого и второго элементов И-НЕ первой ячейки памяти являются информационными входами регистра,а первые входы ее третьего и четвертого элементов И-НЕ - первым управляющим входом регистра, выход третьего элемента И-НЕ каждой ячейки соединен с вторыми входами ее первого и второго элементов И-НЕ, выходы которых соединены перекрестными связями с их третьими входами, выходы первого и второго элементов И-НЕ последней ячей Ки являются информационными выходами регистра, а выход ее четвертого элемента И-НЕ - первым управляющим выходом регистра, первые входы первого и второго элементов И-НЕ -и ячейки памяти соединены с выходами первого и второго элементов И-НЕ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВСЕСОЮЗНАЯ | 0 |

|

SU374663A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Асинхронный регистр сдвига | 1978 |

|

SU728161A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-10-07—Публикация

1982-05-19—Подача