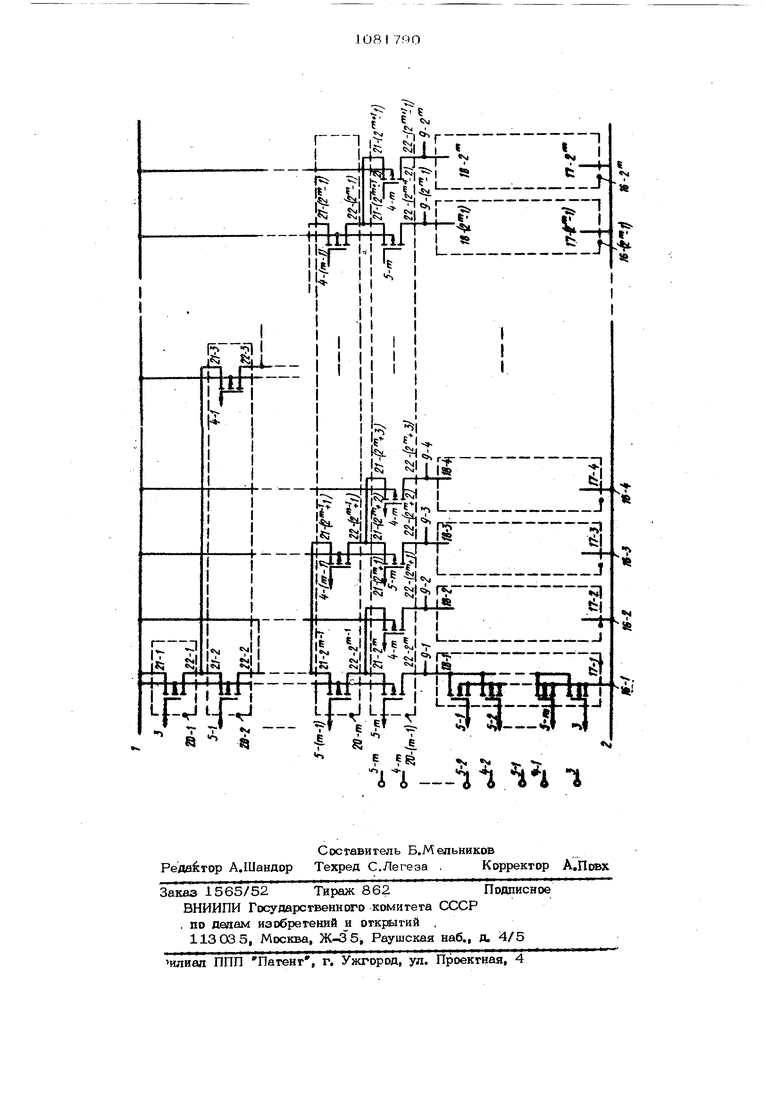

Изобретение огносигся к полупроводниковой электронике и вычислительной технике и может быть использовано при построении устрюйсгв, выполненных на основе комплементарной МДП технс«огии Известен дешифратор, содержащий -канальные и р-канальные транзисторы, плюсовую и минусовую шины питания, щ -адресных входов и 2 выходов ij. Однако данный дешифратор обладает низшим быстродействием. Наиболее близким техническим решением к изобретению является дешифратор содержащий сгробирующий и m -адресны парафазных входов, 2 выходов, п -канальные транзисторы и 2 групп па раплепьно соединенных р канапьнык гранзисторов,причем в каждой из 2 групп исто ки р-канальных транзисторов соединены межау собой и поаключены к плюсовой шине, а их стоки подключены к соответствующим выходам дешифратора 2 . Дешифраторы подобного типа, обладая хорошим быстродействием, требуют для реализации логических функций ботьшого числа транзисторов, что усложняет устройство и увеличивает потребляемую им мощность. Целью изобретения является упрощение дешифратора и снижение потребляем им мощности, Указанная цель достигается тем, что дешифратор, содержащий стробирующий и hi адресных парафазных входов, 2 выходов,И -канальных транзисторов и 2 групп параллельно соединенных р-канальных транзисторов, причем в каж дой из 2 групп истоки р-канальных транзисторов соединены между собой и подключены к плюсовой шине, а их стоки подключены к плюсовой шине, а их стоки подключены к соответствующим выходам дешифратора, п -канальные транз.исторы разделе11ы на m +1 групп по 2 транзисторов в каждой i -и группе, причем истокП -канального транзистора первой группы подключен к минусовой шине, сток каждого Г) -каналь ного транзистора в каждой i -и группе, кроме группы (wi+lj-й- подключен к истокам двух л-канальных транзисторов группы (i и ,-а каждый j -и сток каждого из двух -канальных транзисторов группы (т+1)-й группы Подключен к выходу j -{2 +1) дешифра тора. На чертеже приведена принципиальная электрическая схема предлагаемого дешифратора. Дешифратор содержит плюсовую шину 1, минусовую шину 2, стробирующий вход 3 ,т -парафазных прямых входов 4-1-4- ГЦ и инверсных входов 5-1-5- im , подключенных к каждой их 2 групп 6-1-6-2 , содержащих по W -параллельно соединенны р-канальных транзисторов, истоки 7-1-7-2 , которых подключены к плюсовой шине 1, а стоки 8-1-8-2 - к выходам 9-1-92 дешифратора, группы 10-1-10 (т+1) И -канальных транзисторов, истоки 11-1-11-2 которых подключены к стокам 12-1-12-2 последовательно соединенных У -канальных транзисторов. Дешифратор работает следующим образом. При подаче на -стробирующий вход 3 логического уровня О на всех выходах дешифратора появляется логический уровень 1 (дешифратор заперт). При этом единственный я-канальный транзистор группы 10-1 заперт, а р-канальные транзисторы, управляемые от стробирую щего входа 3, во всех группах 6-1-6-2 открыты, и через них на выходы 9-19-2 передается напряжение плюсовой шины 1 источника питания. В рабочем режиме, когда на строби- руюший вход 3 подан логический уровень 1, единственный п -канальный транзистор группы 10-1 постоянно открыт, и напряжение на его стоке 12-1 равно напряжению минусовой шины 2 источника пиганчя, а р-канальные транзисторы, управляемые стробирующим входом 3,БО Всех группах 6-l-6- 2 постоянно заперты,Когда на адресные парафазные входы 4-1, 5-1, 4- кп , 5- m подана произвольная комбинация двоичного кода, среди групп р-канальных транзисторов 6-1-6-2 выбирается одна единственная группа 6- i , в которой все транзисторы оказываются запертыми. Таким образом, выбранный выход G-ii изолируется от плюсовой шины 1 источника питания, в то время как каждый из остальных выходов 9- j ( j 1 ) соединен с шиной 1 через хотя бы один открытый транзистор в соответствующей групп по 6- i . Предлагаемый режим обеспечивается . соответствующим подключением затворов р-канальных транзисторов к парафазным входам. 31О Как следует на схемы п -канальные гранзисгоры. образуют древовидную струк туру, причем сток каждого транзистора 12-к Б группе 10-/-. подключен к истокам 11-2к и 11-(2к.1) двух транзис торов в rpyrftie 10- (f+1). Эти два транзистора управляются от парафазного входа 4-, 5-i , и, следовательно, при любой входной комбинации двоичного кода всегда один из них заперт, а второй открыт. Благодаря такому включению под воздействием входной комбинации двоичного кода в группах 10-2-10(м+1) образуется цепочка из открытых транзисторов, соединяющая выбранный выход 9-1 со стоком 12-1 открытого транзистора группы 10-1, а следовательно и с минусовой шиной 2 источника питания. Так как, кроме того, выбранный выход 9- 1 изолирован от плюсовой шины источника питания то на этом выходе появляется логический уровень О (соответствующий напряжению минусовой щины 2 источника питания), На пути любого другого выхода 9(j:(4 ) к минусовой шино найдется хотя бы один запертый п -канальный транзистор { хотя бы в одной из групп 10-2-10-(m+1), и поэтому все выходы кроме выбранного 9-1 , изоаированы о минусовой шины. Кроме того, все выходь1 9-1-9-W соединены с плюсов1й щиной 1 и на них появляется логический уровень 1, соответствующий напряжению этой шины. Преимущество предлагаемой схемы заключается в том, что в ней каждый И -канальный транзистор в группах 10-1-10-Ш обслуживает не один, как в известной, а несколько выходов, В частности, единственный транзистор группы 10-1 обслуживает все 2 вых1 дов, каждый из двух транзисторов группы 10-2 обслуживает по выходов и т,д. Благодаря этому число «-канальных транзисторов в предлагаемой схеме де90шифратора щ -разрядного кода со стробированием составляет - 1 против 2 (т+1) в дешифраторе-прототипе. При ги 5, например, эти числа равны соответственно 63 и 192, Число р-канальных транзисторов в обоих схемах в инаково и равн1 2: . Чгм +1), Уменьшение общего числа транзисторов позволяет сократить занятую ими ппошадь кристалла и упростить электрические связи. Потребляемая динамическая мощность (т,е, оищость, рассеиваемая при переключениях схемы) в предлагаемом дешифраторе Меньше, чем в известнее по сяедук щим причинам. Как известно, логачеснше схемы на комплементарных МДП-транзисторах в статическом режиме потребляют весьма незначительную мощность, В динамическом режиме потребляемая мощность возрастает пропорционально частоте переключения, причем заметную долю прироста мощности определяют сквозные броски тока от плюсовой щины питания к минусовой через переключающиеся ,вентили, В известной схеме при переходе от ранее выбранного 1-го к вновь И11бранному j -му выходу броски тока возникают как в 1 -м, так и в j -м вентилях, креме того, броски возможны также и в других вентилях, что заи1сит от сочетания единичных и нулевых уровней в предыдущей i -и и следующей j -и входных комбинациях двоичного кода, а также от задержек распространения управляющих сигналов в схеме. В предлагаем дешифраторе, независимо от действия перечисленных причин, для броска тока существует лишь один путь, проходящий через единственный транзистор группы 10-1 и поэтому ток, потребляемый ог источника питания в переходном режиме, меньше, чем в извёстн1 л дешифраторе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Усилитель парафазного сигнала | 1987 |

|

SU1564690A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Стробируемое пороговое устройство | 1985 |

|

SU1288903A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

ДЕШИФРАТОР, содержащий стробируюший и № адресных парафазных входов, 2 выводов, п -канальные транзисторы и 2 групп параллельно соединенных р-канальных транзисторов, причем в каждой из 2 групп истоки рканальных транзисторов соединены между собой и подключены к плюсовой шине, а их ст(жи подключены к соответсгаующим выходам дешифратора, отличаюш и и с я тем, что, с целью упрощения дешифратора и снижения потребляемой им мощности, М -канальные транзисторы разделены на m+1 групп по транзисторов в каждой - VI группе, причем исток J1 - санальнсхго транзистора первой группы подключен к минуссфой шкВе, сток каждого п санального транзистора в каждой i -ой группе, кроме группы (т +1)-й , подключен к истокам двух П -канальных транзисторов группы i. (-1 , а каждый j -ий сток каждого (Л из двух li -канальных транзисторов группы (w+l)-ft группы подключен к выходу j -

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н | |||

| и др | |||

| Микроэлект ровные схемы цифровых устройств | |||

| Совестное радио, 1975, с.311, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Справочник по интегральным микросхемам | |||

| Под ред | |||

| Тарабрина Б.В | |||

| М., Энергия , 1980, с | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПРЕВРАЩЕНИЯ КИНЕТИЧЕСКОЙ ЭНЕРГИИ КАПЕЛЬНЫХ, ПАРООБРАЗНЫХ И ГАЗООБРАЗНЫХ ЖИДКОСТЕЙ В ЭНЕРГИЮ ДАВЛЕНИЯ | 1923 |

|

SU633A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-03-23—Публикация

1982-01-05—Подача