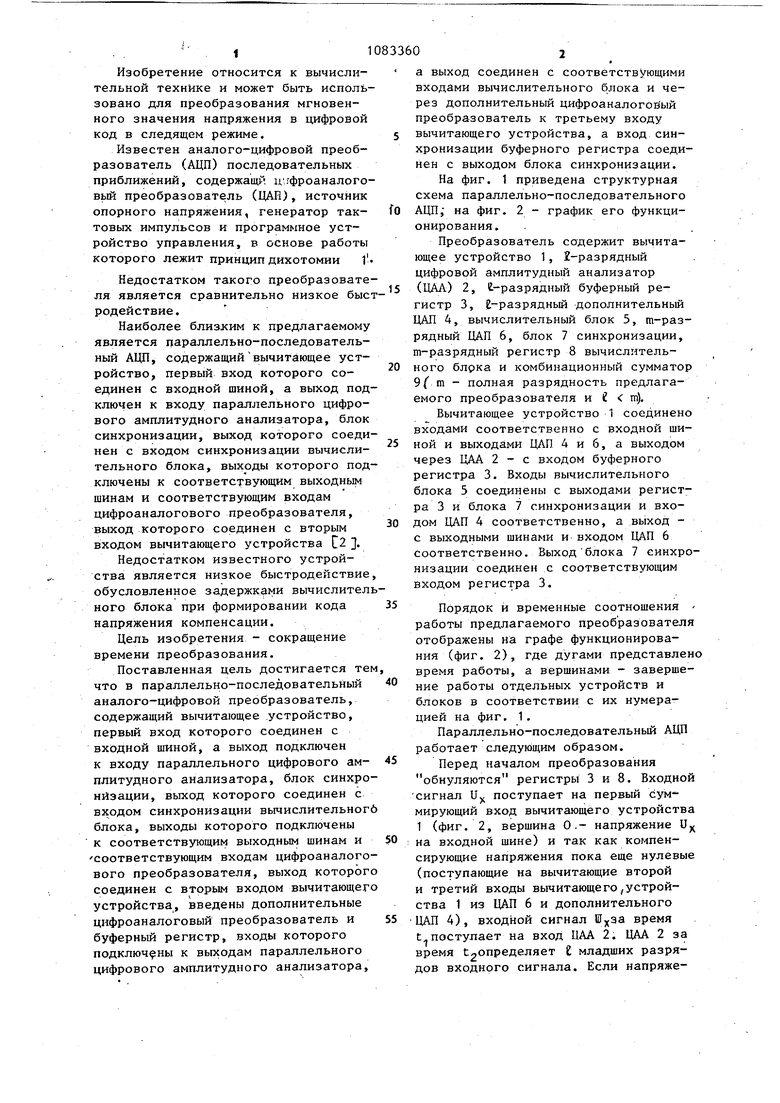

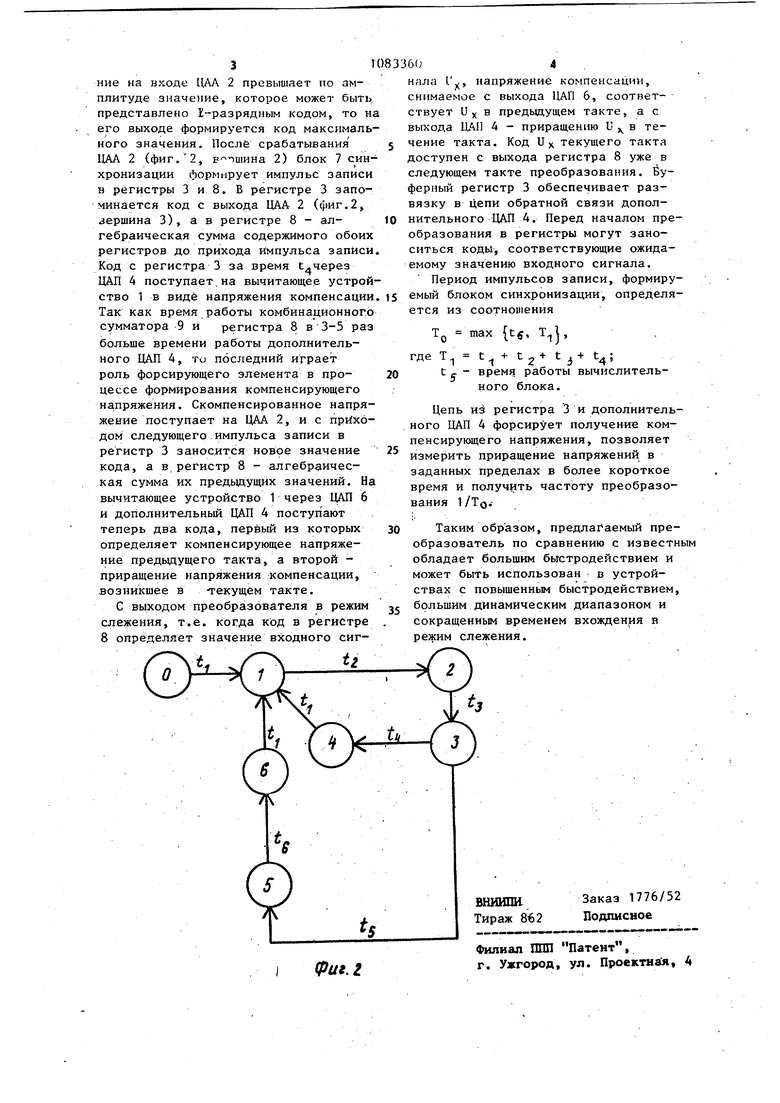

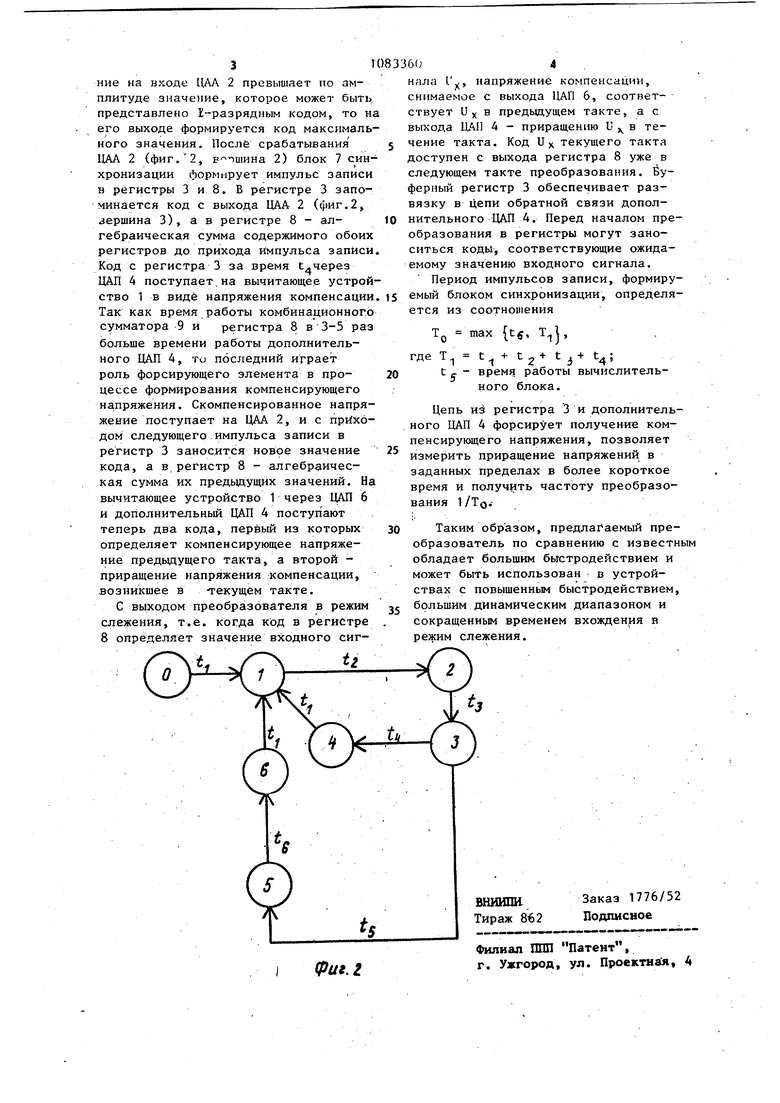

1 Изобретение относится к вычислительной технике и может быть исполь зовано для преобразования мгновенного значения напряжения в цифровой код в следящем режиме. Известен аналого-цифровой преобразователь (АЦП) последовательных приближений, содержащй цгфроаналого вьй преобразователь (ЦАИ), источник опорного напряжения, генератор тактовых импульсов и программное устройство управления, в основе работы которого лежит принцип дихотомии 1 Недостатком такого преобразовате ля является сравнительно низкое быс родействие. Наиболее близким к предлагаемому является параллельно-последовательный АЦП, содержащийвычитающее устройство, первый вход которого соединен с входной шиной, а выход под ключен к входу параллельного цифрового амплитудного анализатора, блок синхронизации, выход которого соеди нен с входом синхронизации вычислительного блока, выходы которого под ключены к соответствующим выходным шинам и соответствующим входам цифроаналогового преобразователя, выход которого соединен с вторым входом вычитающего устройства С2 Д. Недостатком известного устройства является низкое быстродействие обусловленное задержками вычислител ного блока при формировании кода напряжения компенсации. Цель изобретения - сокращение времени преобразования. Поставленная цель достигается те что в параллельно-последовательный аналого-цифровой преобразователь, содержащий вычитающее .устройство, первый вход которого соединен с входной шиной, а выход подключен к входу параллельного цифрового амплитудного анализатора, блок синхро низации, выход которого соединен с входом синхронизации вычислительног блока, выходы которого подключены к соответствующим выходным шинам и Соответствующим входам цифроаналого вого преобразователя, выход которог соединен с вторым входом вычитающего устройства, введены дополнительные цифроаналоговый преобразователь и буферный регистр, входы которого подключены к выходам параллельного цифрового амплитудного анализатора. 0 а выход соединен с соответствующими входами вычислительного блока и через дополнительный цифроаналоговый преобразователь к третьему входу вычитающего устройства, а вход синхронизации буферного регистра соединен с выходом блока синхронизации. На фиг. 1 приведена структурная схема параллельно-последовательного АЦП; на фиг. 2 - график его функционирования. Преобразователь содержит вычитающее устройство 1, -разрядный цифровой амплитудный анализатор (ЦАА) 2, li-разрядный буферный регистр 3, 2-разрядный дополнительный ЦАП 4, вычислительный блок 5, т-разрядный ЦАП 6, блок 7 синхронизации, т-разрядный регистр 8 вычислительного блрка и комбинационный сумматор 9( т - полная разрядность предлагаемого преобразователя к i т), Вычитающее устройство 1 соединено входами соответственно с входной шиной и выходами ЦАП 4 и 6, а выходом через ЦАА 2-е входом буферного регистра 3. Входы вычислительного блока 5 соединены с выходами регистра 3 и блока 7 синхронизации и входом ЦАП 4 соответственно, а выход с выходными шинами и входом ЦАП 6 соответственно. Выходблока 7 синхронизации соединен с соответствующим входом регистра 3. Порядок и временные соотношения работы предлагаемого преобразователя отображены на графе функционирования (фиг. 2), где дугами представлено время работы, а вершинами - завершение работы отдельных устройств и блоков в соответствии с их нумерацией на фиг. 1. Параллельно-последовательный АЦП работает следующим образом. Перед началом преобразования обнуляются регистры 3 и 8. Входной сигнал и поступает на первый суммирующий вход вычитающего устройства 1 (фиг. 2, вершина О.- напряжение V на входной шине) и так как компенсирующие напряжения пока еще нулевые (поступающие на вычитающие второй и третий входы вычитающего,устройства 1 из ЦАП 6 и дополнительного ЦАП 4), входной сигнал время t поступает на вход ЦАА 2. ЦАА 2 за время t2oпpeдeляeт i младших разрядов входного сигнала. Если напряжение на входе ЦМ 2 превышает по амплитуде значение, которое может быть представлено -разрядным кодом, то н , его выходе формируется код максималь ного значения. После срабатывания ЦАЛ 2 (фиг,2, в пшина 2) блок 7 син хронизации формирует импульс записи в регистры 3 и 8. В регистре 3 запоминается код с выхода ЦАА 2 (фиг.2, зершина 3), а в регистре 8 - алгебраическая сумма содержимого обоих регистров до прихода импульса записи Код с регистра 3 за время С через ЦАП 4 поступает.на вычитающее устрой ство 1 в виде напряжения компенсации Так как время работы комбинационного сумматора 9 и регистра 8 в 3-5 раз больше времени работы дополнительного ЦАП 4, то последний играет роль форсирующего элемента в процессе формирования компенсирующего напряжения. Скомпенсированное напряжение поступает на ЦАА 2, и с приходом следующего.импульса записи в регистр 3 заносится новое значение кода, а в регистр 8 - алгебр ическая сумма их предьщущих значений. На вычитающее устройство 1 через ЦАП 6 и дополнительный ЦАП 4 поступают теперь два кода, первый из которых определяет компенсирующее напряжение предыдущего такта, а второй приращение напряжения компенсации, возникшее в -текущем такте. С выходом преобразователя в режим слежения, т.е. когда код в регистре 8 определяет значение входного сиг60, напряжение компенсации, снимаемое с выхода ЦАП 6, соответствует Lx в предыдущем такте, а с выхода ЦАП 4 - приращению U ,. в течение такта. Код Ц текущего такта доступен с выхода регистра 8 уже в следующем такте преобразования, буферный регистр 3 обеспечивает развязку в цепи обратной связи дополнительного ЦАП 4. Перед началом преобразования в регистры могут заноситься коды, соответствующие ожидаемому значению входного сигнала. Период импульсов записи, формируемый блоком синхронизации, определяется из соотношения , т,) t - времд работы вычислительного блока. Цепь и регистра 3 и дополнительного ЦАП 4 форсирует получение компенсирующего напряжения, позволяет измерить приращение напряжений в заданных пределах в более короткое время и получить частоту преобразования I/TQ.Таким образом, предлаг аемый преобразователь по сравнению с известным обладает большим быстродействием и может быть использован в устройствах с повышенным быстродействием, большим динамическим диапазоном и сокращенным временем вхождения в режим слежения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1027810A1 |

| Функциональный аналого-цифровой преобразователь | 1989 |

|

SU1688411A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1982 |

|

SU1115219A1 |

| Следящий аналого-цифровой преобразователь | 1989 |

|

SU1674371A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Интерполирующий фильтр | 1982 |

|

SU1100715A1 |

ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий вычитающее устройство, первый вход которого соединен с входной шиной, а выход подключен k входу параллельного цифрового амплитудного анализатора, блок синхрониUx зации, выход которого соединен с входом синхронизации вычисли|гёльного блока, выходы которого подключены к соответствующим выходным шинам и соответствующим входам цифроана.логового преобразователя, выход которого соединен с бторым входом вычитающего устройства, -отличающийся тем, что, с целью сокращения времени преобразования,в него введены дополнительный цифроаналоговый преобразователь и буферный регистр, входы которого подключены к выходам параллельного цифрового амплитудного анализатора, а выход соединен с со-: i ответствующими входами вычислительного блока и через дополнительный (Л цифроаналоговый преобразователь С к третьему входу вычитающего устройства, а вход синхронизации буферного регистра соединен с выходом блока синхронизации. х :л :.о д

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бахтиаров Г.Д | |||

| Аналого-цифровые преобразователи, 1980, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразование информации в аналого-цифровых вычислительных устройствах и системах | |||

| Под ред | |||

| Г.К | |||

| Петрова, 1973, с | |||

| Гудок | 1921 |

|

SU255A1 |

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

Авторы

Даты

1984-03-30—Публикация

1981-06-26—Подача